Edge detection method and system and clock and data recovery circuit based on FPGA (Field Programmable Gate Array)

An edge detection and data signal technology, applied in the field of communication, can solve problems such as long locking time, loss of lock, and phase-locked loop that cannot meet fast synchronization, etc., and achieve the effects of fast capture, wide application range, and improved accuracy and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

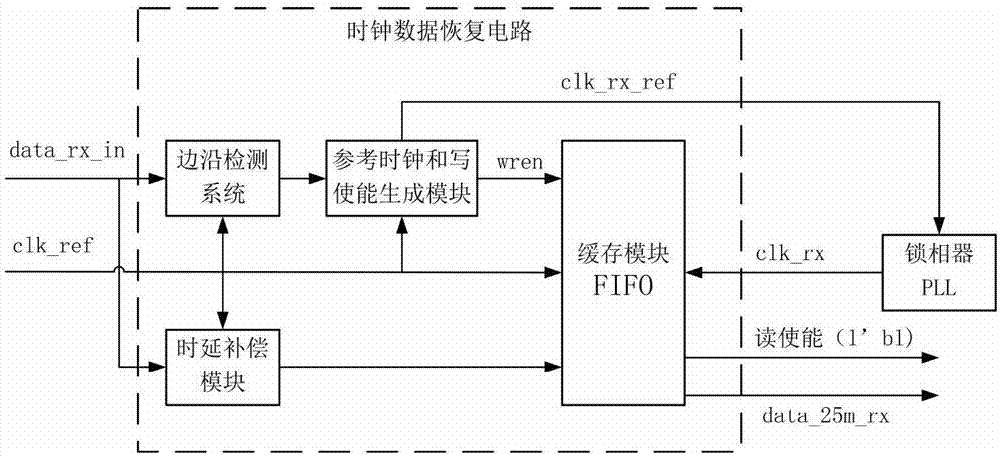

[0037] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

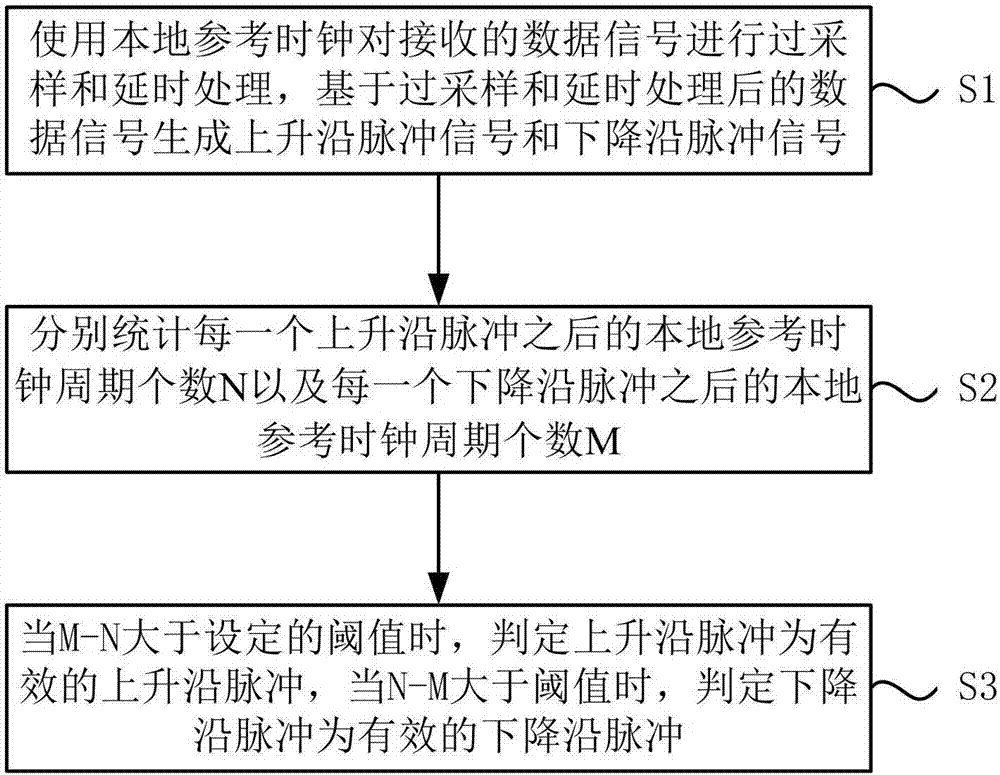

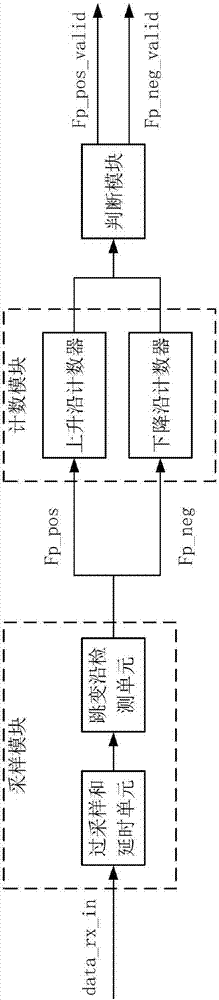

[0038] see figure 1 As shown, the embodiment of the present invention provides a kind of edge detection method based on FPGA, comprises the following steps:

[0039] S1. Use the local reference clock to oversample and delay the received data signal, and generate a rising edge pulse signal and a falling edge pulse signal based on the oversampled and delayed data signal. The rising edge pulse signal includes several rising edges Pulse, falling edge The pulse signal includes several falling edge pulses.

[0040] Jump edge pulses include rising edge pulses and falling edge pulses. Rising edge pulses include effective rising edge pulses and abnormal rising edge pulses introduced by interference, and falling edge pulses include effective falling edge pulses and abnormal falling edge pulses introduced by interference. Effective rising edge...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com