Frame packaging structure integrating passive device and manufacturing method thereof

A technology that integrates passive devices and packaging structures, and is used in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

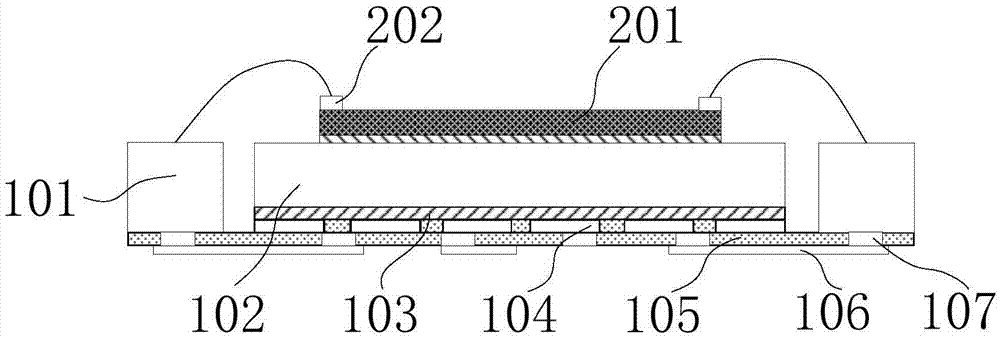

[0050] The method for preparing the frame package structure of integrated passive devices according to the embodiment of the present invention includes the following steps:

[0051] Step 1, providing a lead frame, which includes a die pad and a conductive pad located on the periphery of the die pad;

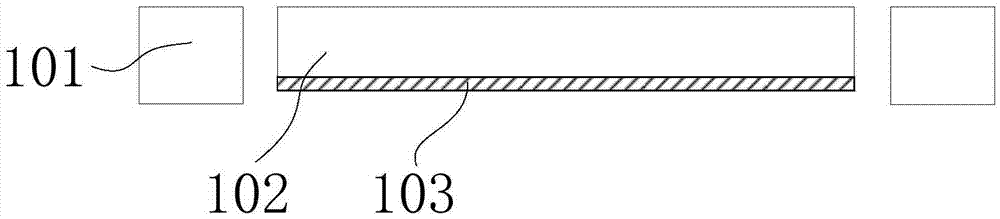

[0052] Step 2, forming a first insulating dielectric layer on the lower surface of the die pad, and the first insulating layer is deposited by chemical vapor deposition CVD, physical vapor deposition PVD and other processes;

[0053] Step 3, forming a layer of metal conductive material on the lower surface of the first insulating dielectric layer through an electroplating process, and then removing unnecessary metal materials through processes such as photolithography and etching processes, thereby forming a metal structure layer, the metal structure The shape of the layer can be a metal plane arranged in an array in the horizontal direction as the lower plate of the capacitive e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com