GaN-based VCSEL chip based on porous DBR and preparation method

A chip and current confinement layer technology, applied in laser parts, electrical components, lasers, etc., can solve the problems of complex device process, high cost, and lower quality factor of resonator, and achieve simple and repeatable process Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

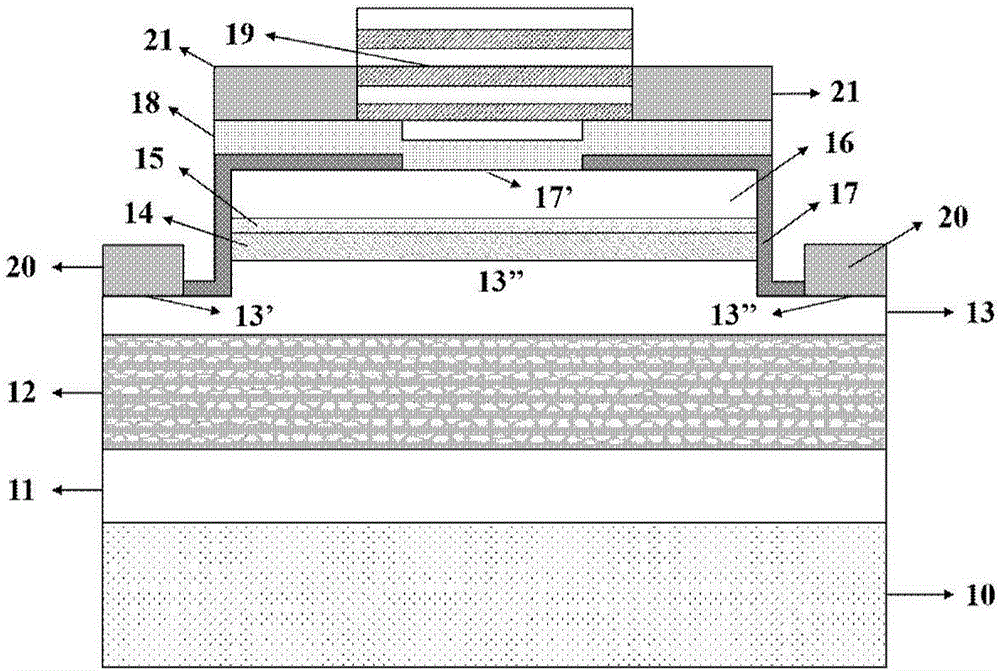

[0035] see figure 1 , the present invention provides a GaN-based VCSEL chip based on porous DBR, comprising:

[0036] A substrate 10 is a plane or pattern substrate, and the material of the substrate 10 is sapphire, silicon or silicon carbide;

[0037] A buffer layer 11, which is made on the upper surface of the substrate 10, the buffer layer is composed of a low-temperature GaN nucleation layer and an unintentionally doped GaN layer, using high-purity ammonia as a nitrogen source, trimethylgallium or triethylgallium As the Ga source, the GaN nucleation layer is grown at low temperature first, and then the unintentionally doped GaN layer is grown at high temperature. Materials that can be used as the nucleation layer also include AlN, ZnO or graphene;

[0038] A bottom porous DBR layer 12, which is made on the upper surface of the buffer layer 11, the material of the bottom porous DBR layer 12 is GaN, AlGaN, InGaN or AlInGaN, or a combination of the above materials. Porous l...

PUM

| Property | Measurement | Unit |

|---|---|---|

| reflectance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com