Domestic BMC (baseboard management controller) chip based SM4 algorithm IP (intellectual property) core design method

A BMC chip and design method technology, applied in the direction of internal/peripheral computer component protection, etc., can solve the problems that cannot meet the operation speed requirements of large data files, server security cannot be guaranteed, increase the layout space of the server motherboard, etc., and achieve saving Hardware cost, compensation limitations, effect of security guarantees

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

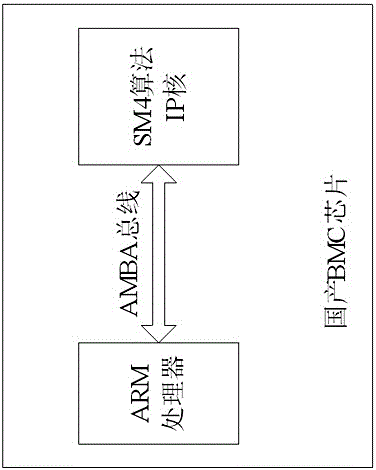

[0048] Such as figure 1 As shown, a design method based on the SM4 algorithm IP core of the domestic BMC chip, the method adopts the SM4 symmetric cryptographic algorithm suitable for commercial cryptographic applications issued by the State Cryptography Administration in the selection of the cryptographic algorithm, which has high security and is convenient Autonomous and controllable;

[0049] The specific design adopts the hardware description language Verilog to design and realize the SM4 algorithm, and package it into a hardware IP core and integrate it into the domestic BMC chip. The AMBA bus is connected to the ARM processor in the domestic BMC chip, which makes the design flexible and convenient, and can meet the application requirements for data calculation in the field of information security.

Embodiment 2

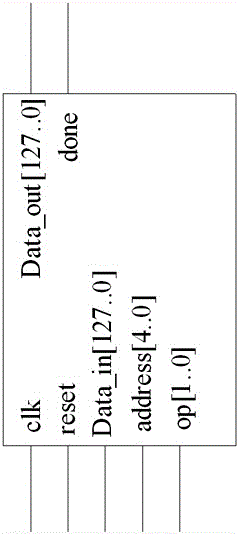

[0051] Such as figure 2 As shown, on the basis of Embodiment 1, all signals of the encapsulation interface of the SM4 algorithm IP core described in this embodiment are clock-synchronized, sampled on the rising edge, and active at a high level. Each signal and its functions are as follows:

[0052] clk: input signal, the clock of the AMBA bus, as the clock signal of the IP core;

[0053] reset: input signal, which is the reset signal of the IP core;

[0054] Data_in[127..0]: input signal, 128 bit data input;

[0055] address[4..0]: input signal, address bus, register for selecting IP core after decoding;

[0056] op[1..0] : input pin, function selection flag, when op=0, select write key operation; when op=1, select encryption operation; when op=2, select decryption operation;

[0057] Data_out[127..0]: output signal, 128 bit operation result output;

[0058] done: output pin: a completion flag generated when each data packet operation is completed, active high.

Embodiment 3

[0060] On the basis of embodiment 1 or 2, the SM4 algorithm IP core described in the present embodiment comprises 4 registers, and word length is 32 bit, and the function of each register is as follows:

[0061] 1) Key register: the offset address is 0x00-0x07, which is used to store the user key during SM4 encryption or decryption, and only write operations can be performed on this register;

[0062] 2) Data register: the offset address is 0x08-0x0B, which is used to store a plaintext group or ciphertext group data (128bit) of the SM4 algorithm, and only write operations can be performed on this register;

[0063] 3) Operation result register: the offset address is 0x10-0x13, which is used to store the operation result of a plaintext group or ciphertext group of the SM4 algorithm, and this register can only be read;

[0064] 4) Control register: The offset address is 0x14, which can read and write the control register, so as to control the function of the SM4 algorithm IP cor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com