Wafer encapsulation method

A chip packaging and chip technology, applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of time-consuming and high cost, reduce reflow baking, improve bonding ability, and hinder thermal diffusion Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to further explain the technical solution of the present invention, the present invention will be described in detail below through specific examples.

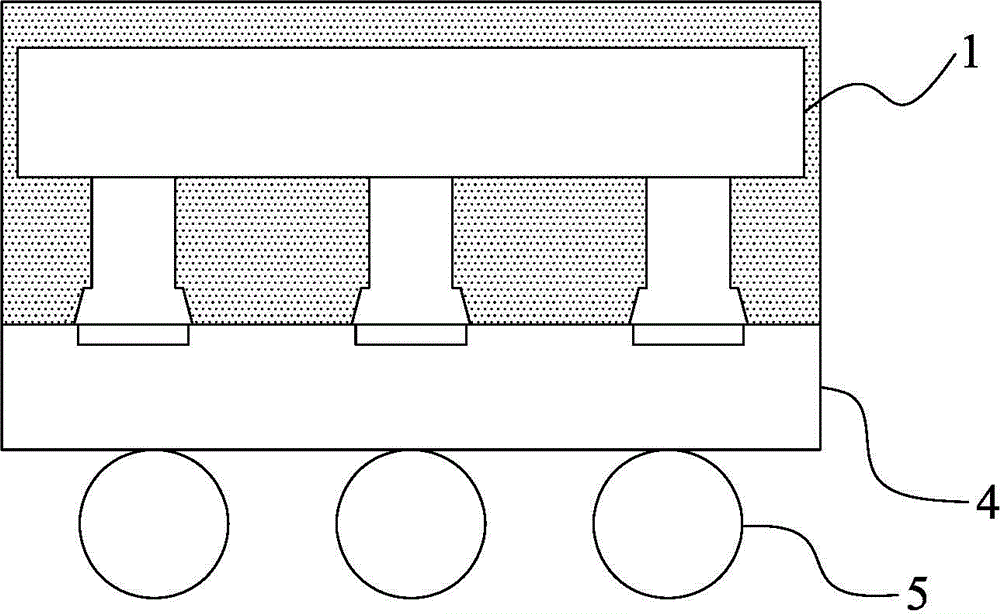

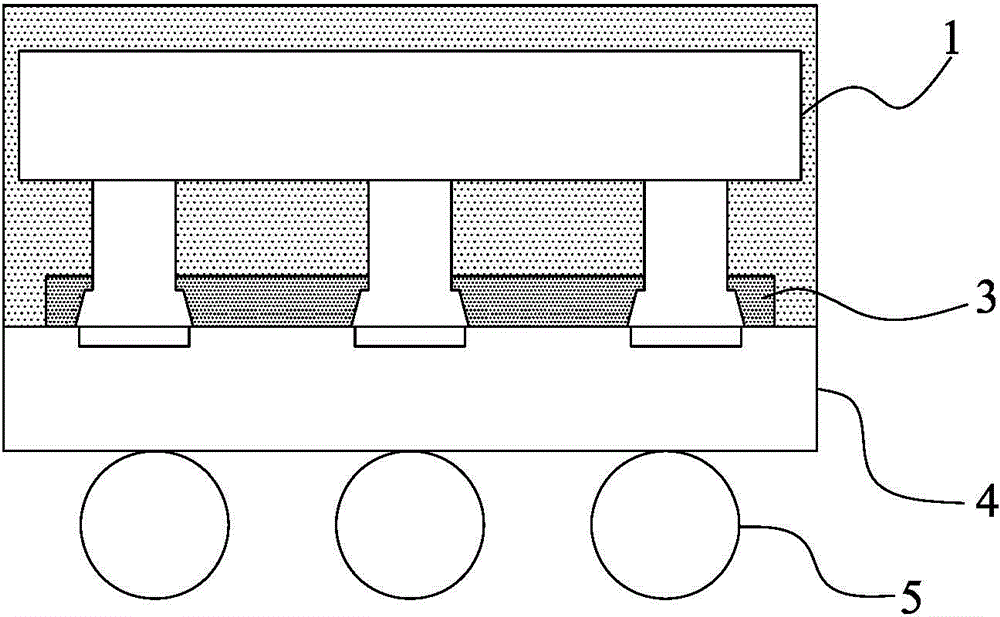

[0023] Such as image 3 The structure containing non-conductive glue (NCP) of the present invention is to apply flux 2 on the copper pillar between the integrated circuit 1 and the substrate 4, and connect the two by welding, and the substrate 4 is coated with non-conductive glue (NCP) 3. Solder balls 5 are arranged under the substrate to form a packaged integrated circuit structure.

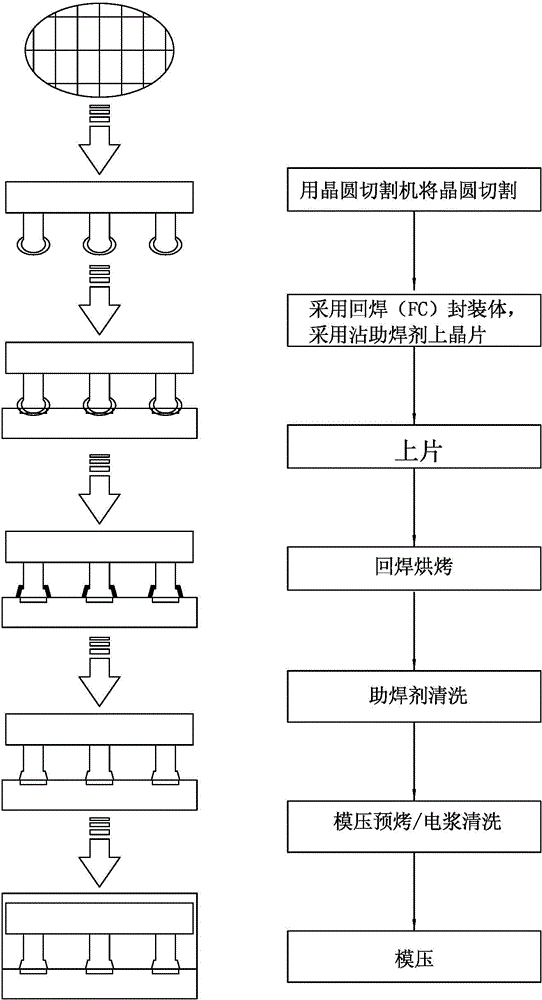

[0024] Such as Figure 4 Shown, a kind of chip packaging method of the present invention comprises the following steps:

[0025] The wafer is cut by a wafer cutting machine, and then the wafer is picked up by the loading equipment, and the tin bumps of the wafer are stained with flux.

[0026] Then use the glue material printing equipment to apply the non-conductive glue (NCP) on the front of the substrate by steel plate print...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com