Multilevel multitask parallel decoding algorithm on multicore processor platform

A multi-core processor and decoding algorithm technology, which is applied in the field of multi-level multi-task parallel decoding algorithm, achieves the effects of reducing frequent scheduling and switching, improving parallelism, and high engineering application value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Below in conjunction with accompanying drawing, technical scheme of the present invention is described in further detail:

[0026] The invention realizes the real-time parallel decoding of HEVC high-definition video aiming at the ultra-high parallel computing performance of the multi-core processor. We will use the Tilera GX36 multi-core processor as our experimental platform, which consists of 36 Tile cores. The Tilera multi-core processor has a complete set of multi-core development tools, which provides convenience for us to implement multi-core parallel programs.

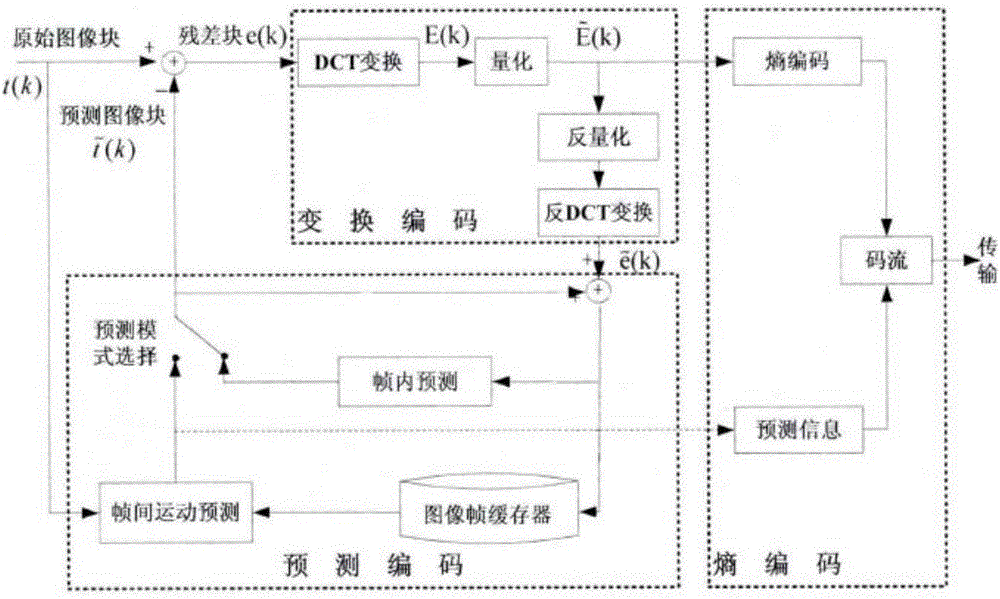

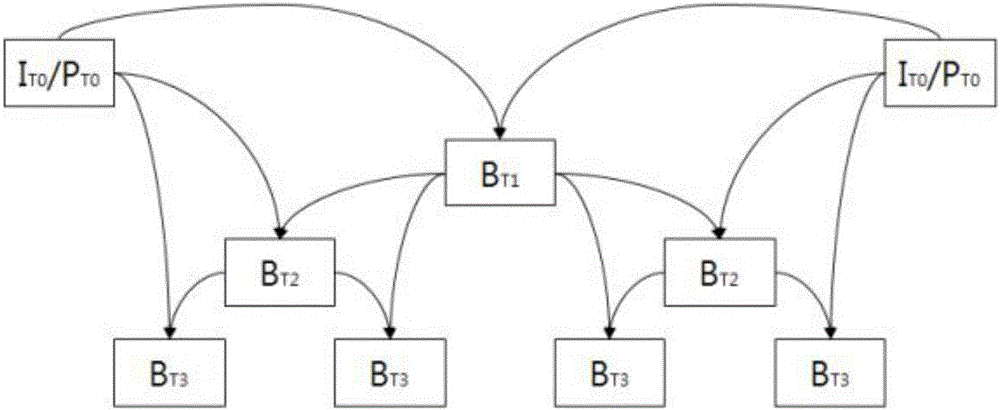

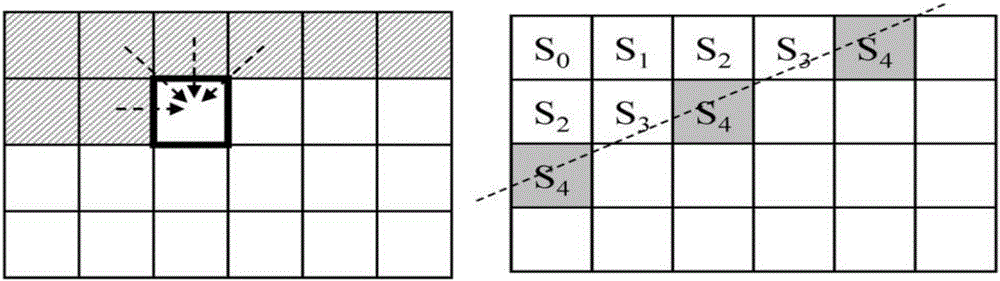

[0027] figure 1 Shown is the HEVC decoder block diagram. The basic structure of the HEVC encoding and decoding principle is basically the same as that of H.264 / AVC, but the performance improvement of the HEVC encoding and decoding comes from a series of in-depth optimizations at the module level and innovations in some design elements. Among them, the new features that are more important for the perform...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com