Formation method of LDMOS (Lateral Diffusion MOS) transistor and LDMOS transistor

A technology of transistors and semiconductors, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as poor performance of fin-type LDMOS transistors, and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

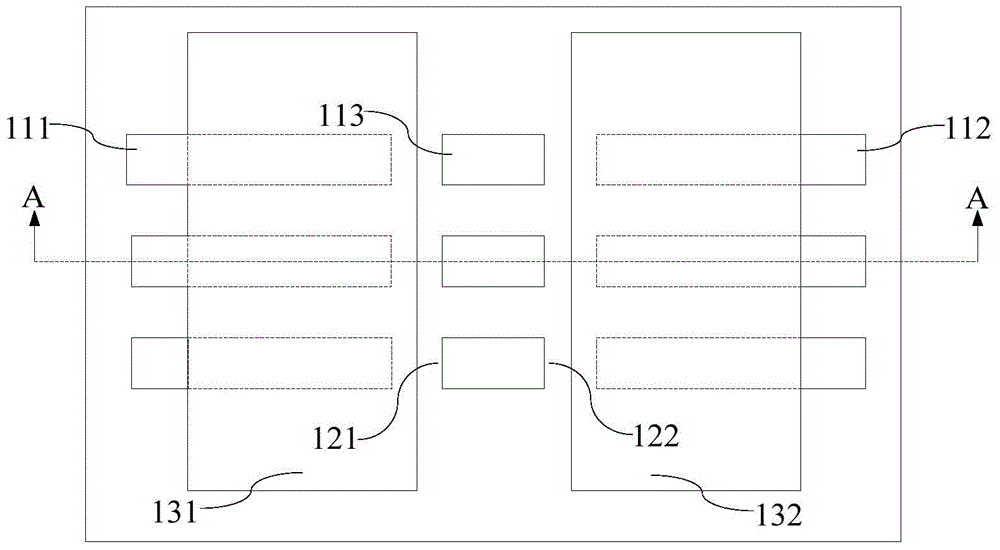

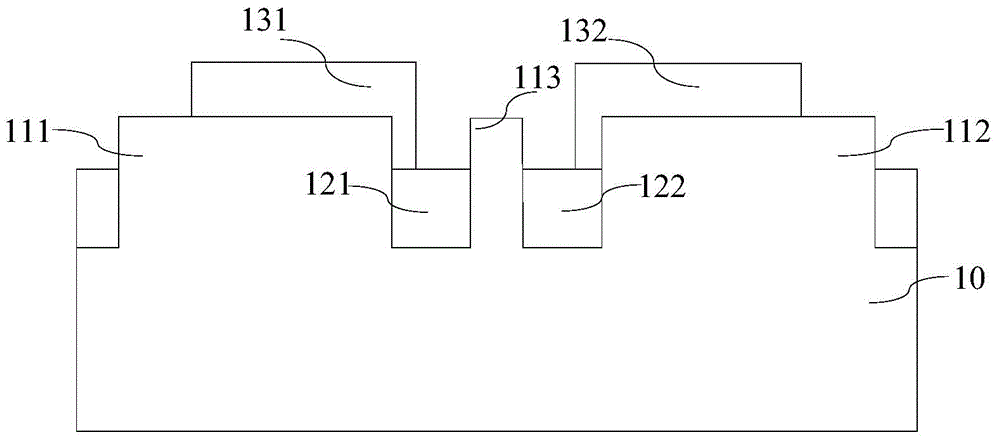

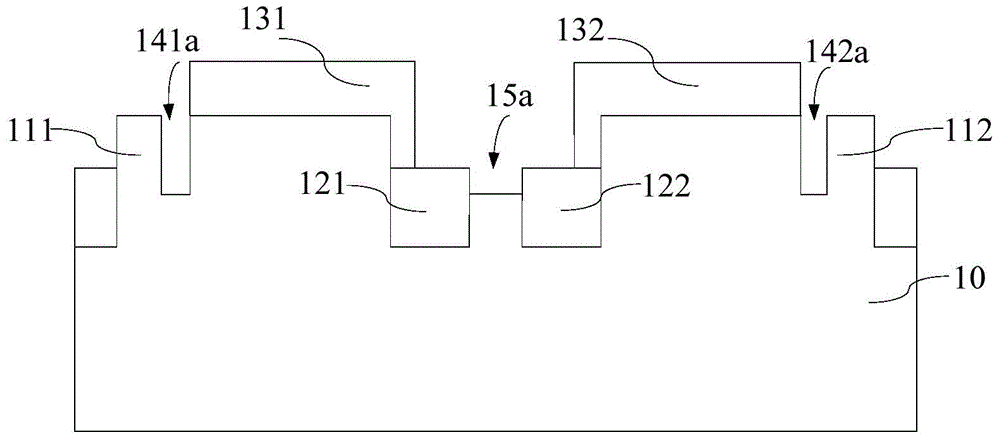

[0070] This embodiment This embodiment provides a method for forming an LDMOS transistor, which is described by using a common drain of two adjacent LDMOS transistors.

[0071] combined reference Figure 8 and Figure 9 , providing a semiconductor substrate 20 .

[0072] In this embodiment, the semiconductor substrate 20 is a silicon substrate. The semiconductor substrate 20 has at least one fin 201 . There is an insulating layer 202 lower than the fins 201 between the fins 201 . The material of the insulating layer 202 is silicon oxide. The specific formation method is as follows:

[0073] At least one protruding structure is formed on the semiconductor substrate 20, and then an insulating layer 202 having the same height and lower than the protruding structure is formed between the protruding structures, and the insulating layer 202 plays an insulating role between semiconductor devices. The protruding structure higher than the insulating layer 202 is the fin 201 .

...

Embodiment 2

[0150] refer to Figure 12 , the present invention also provides an LDMOS transistor structure, two adjacent LDMOS transistors share one drain. It specifically includes: a semiconductor substrate 20, the semiconductor substrate 20 has a fin 201, and the fin 201 has a well region therein; a gate structure 21 and a second gate structure 22;

[0151] The first source 251 and the drain 264 in the semiconductor substrate on both sides of the first gate structure 21, the second source 252 and the drain in the semiconductor substrate on both sides of the second gate structure 22 264, the drain 264 is a common drain of two adjacent LDMOS transistors;

[0152] The LDMOS transistor in this embodiment also includes:

[0153] The drift region 203, the drift region is located in the fin portion 201, surrounded by the well region, the first gate structure 21 and the second gate structure 22 respectively partially cover the drift region 203, and the The drain 264 is located in the drift ...

Embodiment 3

[0164] refer to Figure 13 This embodiment provides a method for forming an LDMOS transistor. The difference between this embodiment and Embodiment 1 is that Embodiment 1 has two sources, namely a first source and a second source. The first source and the second source share one drain. The LDMOS transistor in this embodiment has only one source 35, and the drain 364 in this embodiment is not a common drain. In this embodiment, there is only one gate structure 31 between the source 35 and the drain 364 . The gate structure 31 partially covers the drift region 303 .

[0165] A first barrier layer 331 to a first barrier layer 334 are formed on the drift region to define the position and width of the drain. The details are as follows: in the drift region 203 , two adjacent first barrier layers 333 and 334 define the position and width of the drain 364 .

[0166] In other embodiments, the first gate structure and the first barrier layer closest to the first gate structure defin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com