A calibration circuit design method for pipeline adc

A calibration circuit and assembly line technology, which is applied in the direction of analog/digital conversion calibration/test, electrical components, code conversion, etc., can solve the problems of complex implementation, slow calibration speed, and high power consumption of the calibration circuit, and achieve simplification of the calibration circuit. Small power consumption and area, easy to use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

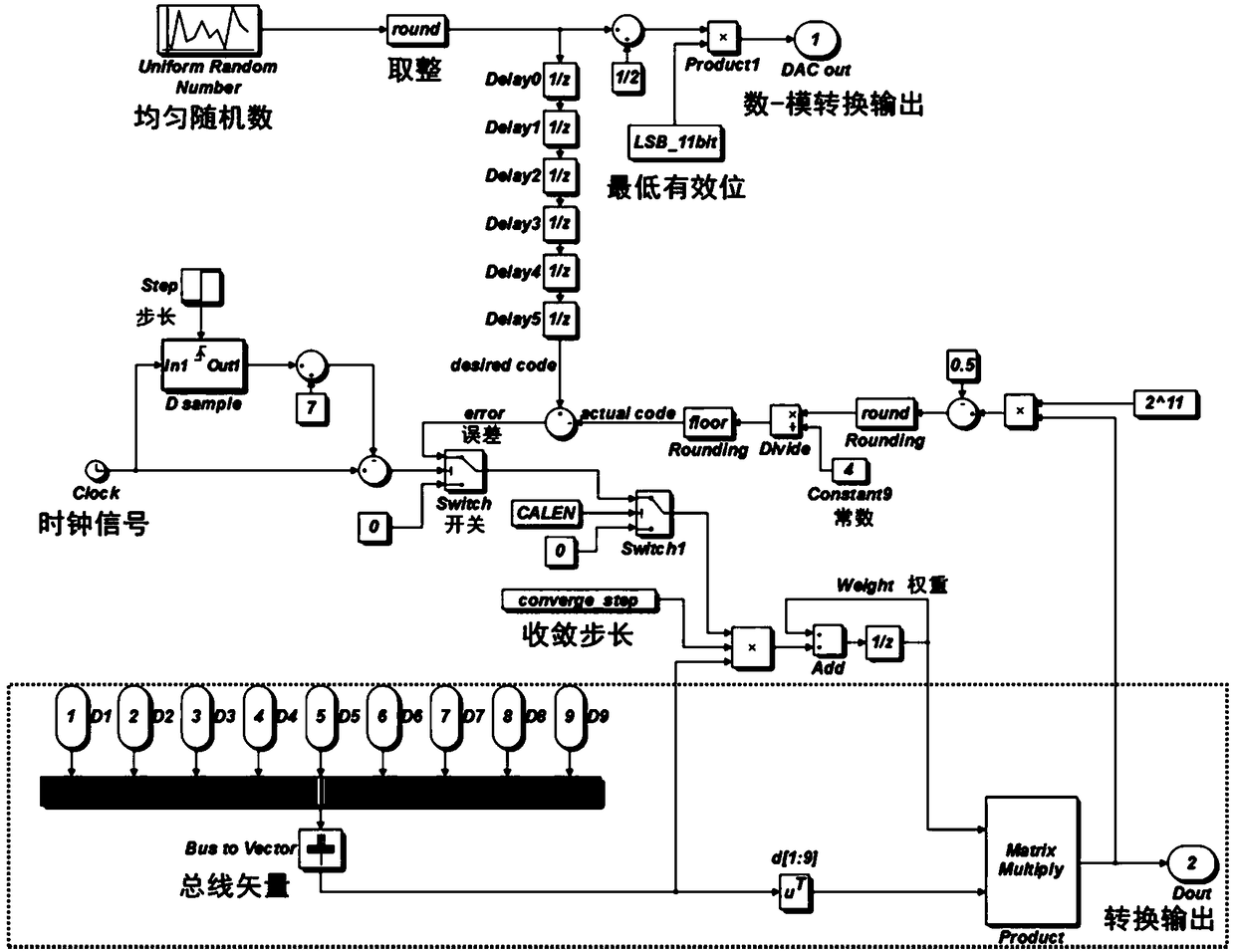

[0026] The present invention is described in detail below in conjunction with accompanying drawing

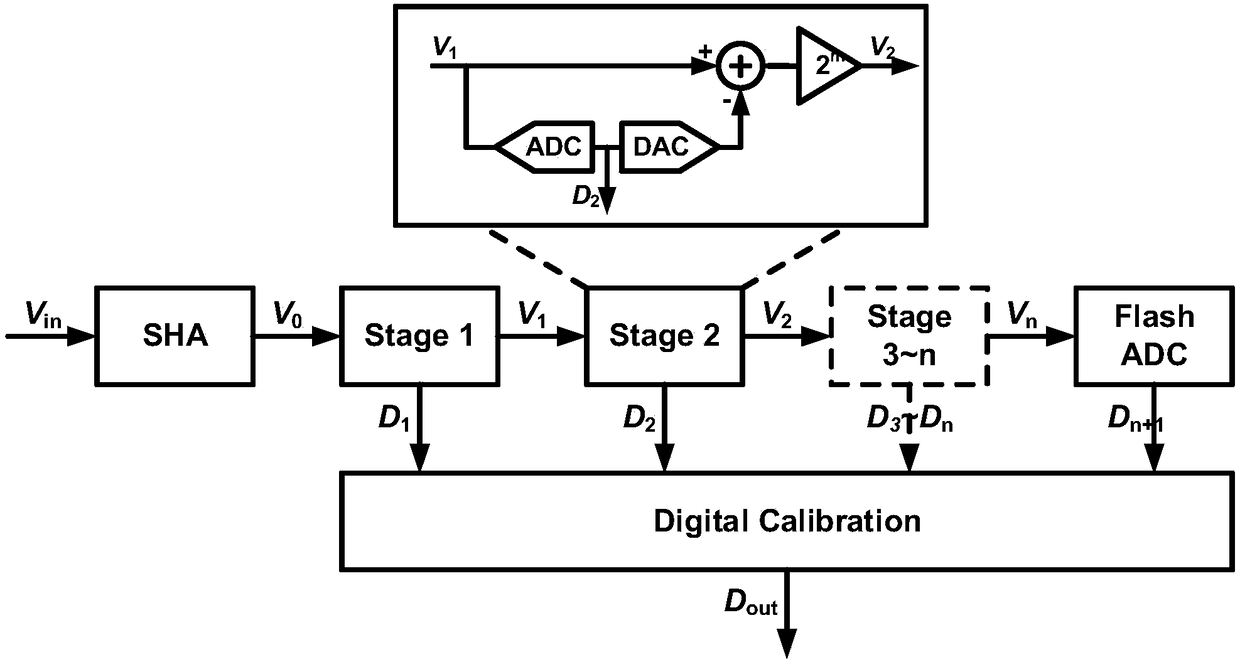

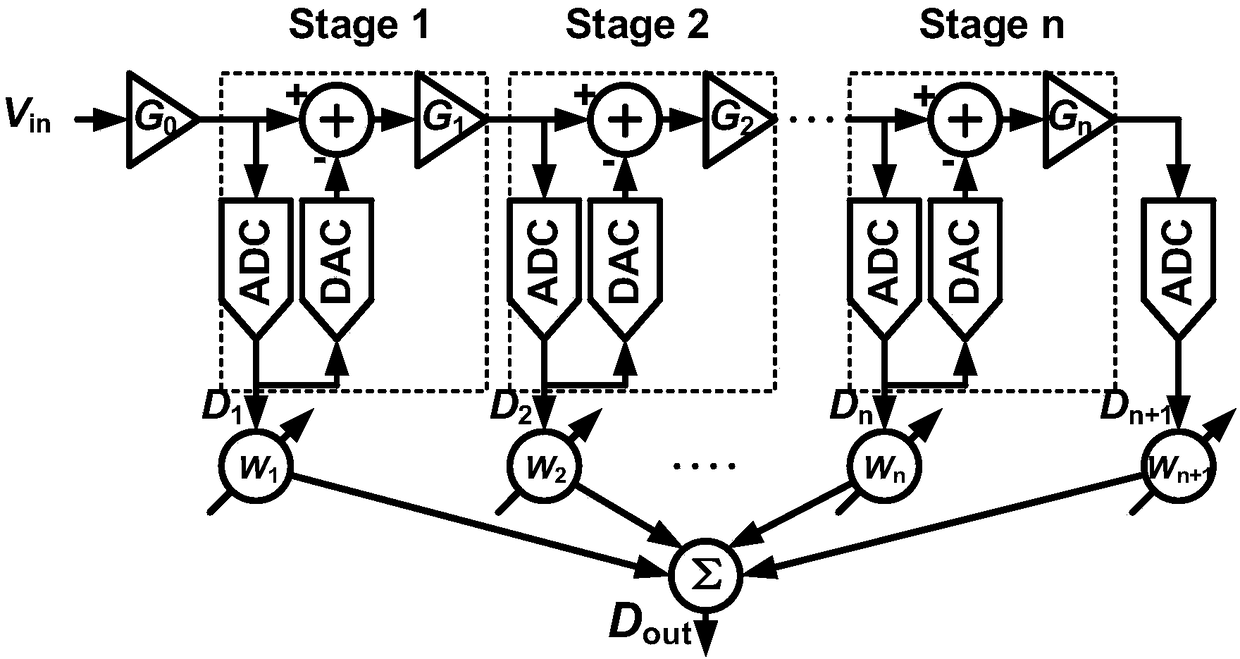

[0027] A typical pipeline ADC with a digital calibration module such as figure 1 and figure 2 Shown, including the front-end sampling and holding amplifier (SHA), sub-stage (Sub-Stage), the last stage Flash ADC and digital calibration part. The input voltage to the ADC can be expressed as,

[0028]

[0029] Among them, n is the number of stages of the pipeline ADC, G i is the redundancy gain (inter-stage gain) of the i-th redundant amplifier, G 0 Indicates the voltage gain of SHA, D n+1 Indicates the digital output of the flash ADC, V ref is the reference voltage of the entire ADC (the full-scale input of the entire ADC is -V ref ~+V ref ), V noise,out,i is the output noise voltage value of the i-th stage, D i is the i-th digital output, W i is the weight of the i-th digital output,

[0030] After adding the calibration algorithm, the equivalent voltage of the di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com