Multi-chip and single-lap stack sandwich package structure with exposed frames and technique for the multi-chip and single-lap stack sandwich package structure

A technology of packaging structure and process method, which is applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of high equipment purchase cost, inability to form one piece, low manufacturing efficiency, etc., and achieve saving equipment purchase, reduction and exemption Effects of interconnected processes and improved productivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

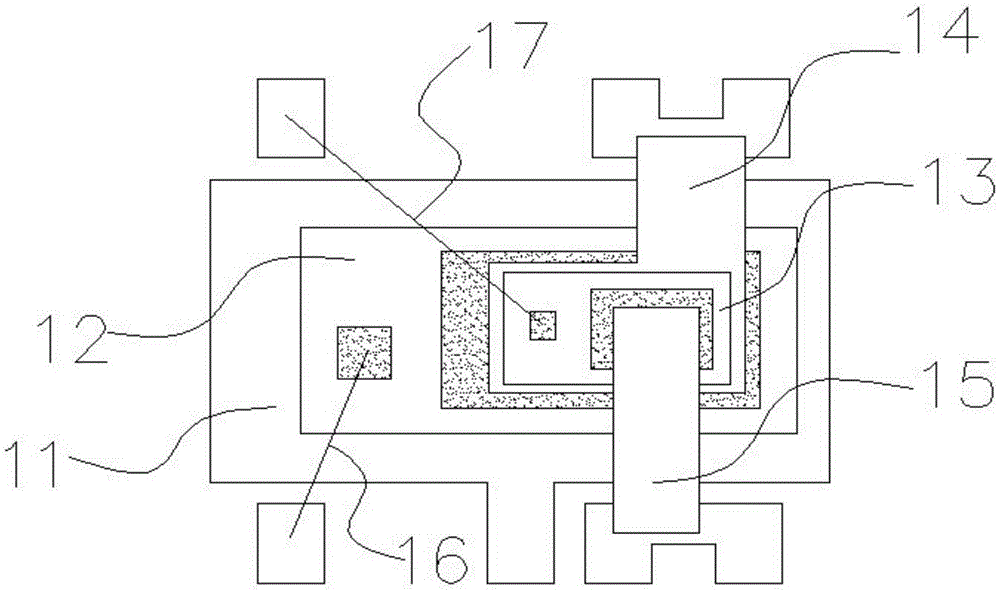

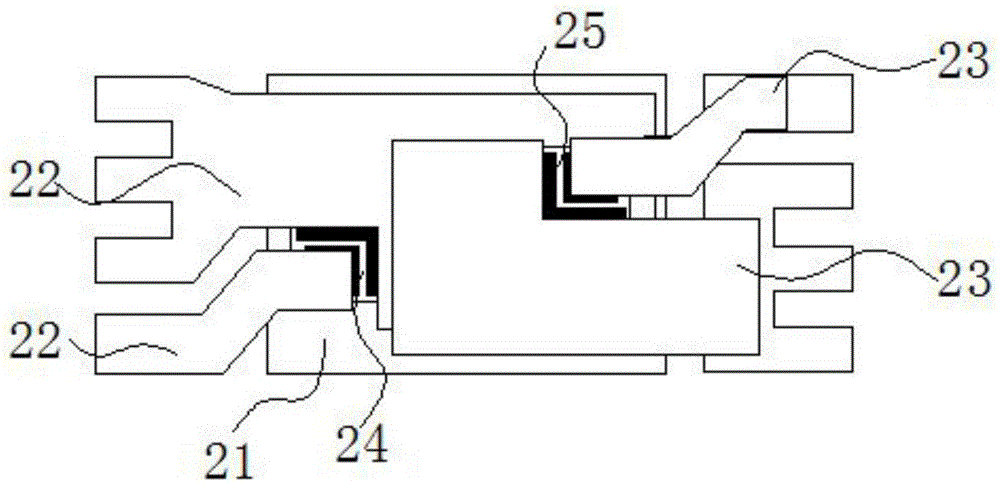

[0068] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0069] As shown in Fig. 7(a) to Fig. 7(m), a process method of a frame-exposed multi-chip single-lap stacked sandwich packaging structure in this embodiment, the specific process steps are as follows:

[0070] Step 1, see Figure 7(a), provide the first lead frame, the material of the first lead frame is alloy copper material, pure copper material, aluminum copper plated material, zinc plated copper material, nickel-iron alloy material, or other CTE The range is 8*10^-6 / ℃~25*10^-6 / ℃ conductive material;

[0071] Step 2. Referring to Figure 7(b), apply solder paste on the base island area of the first lead frame by screen printing. The purpose is to realize the bonding with the base island after the first chip is implanted. Thickness and opening area can precisely control the thickness, area and position of solder paste;

[0072] Step 3, ref...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com