an etching method

A technology of lithography and trenching, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of inability to form contact holes, difficulty in lithography and etching of contact holes, etc., and solve the problem of difficulty in lithography and etching. Large, well-filled, reduced-impact effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

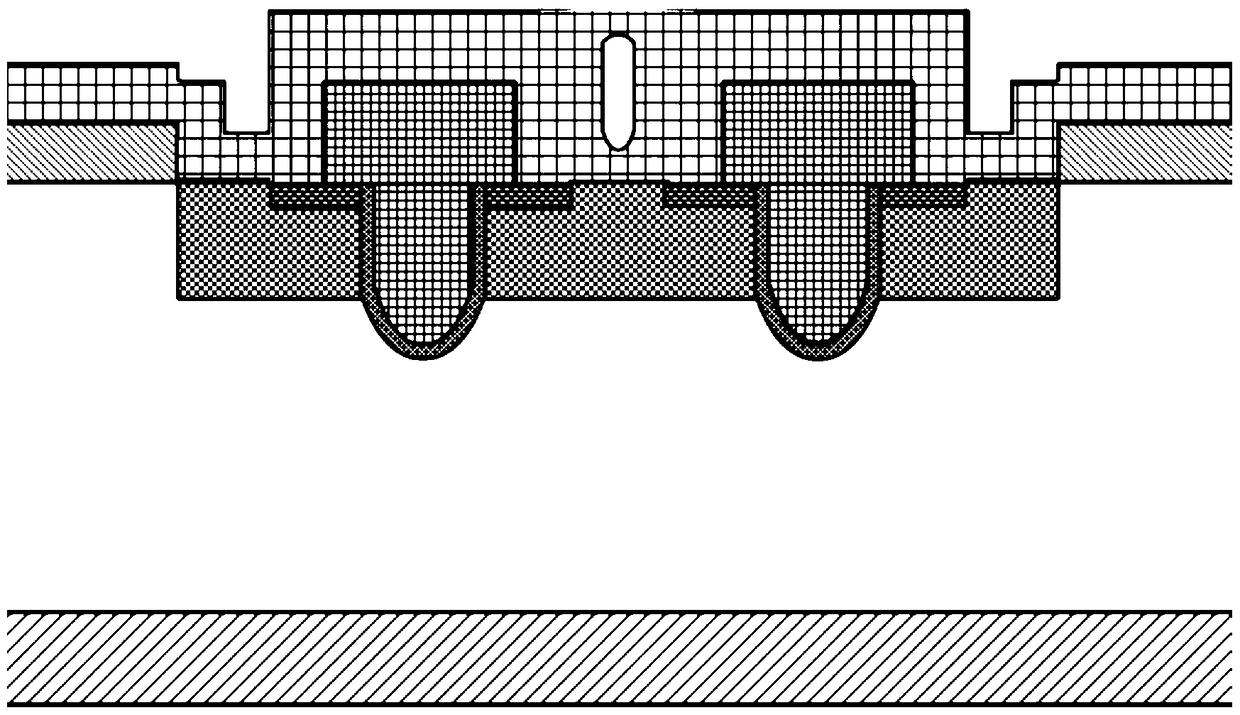

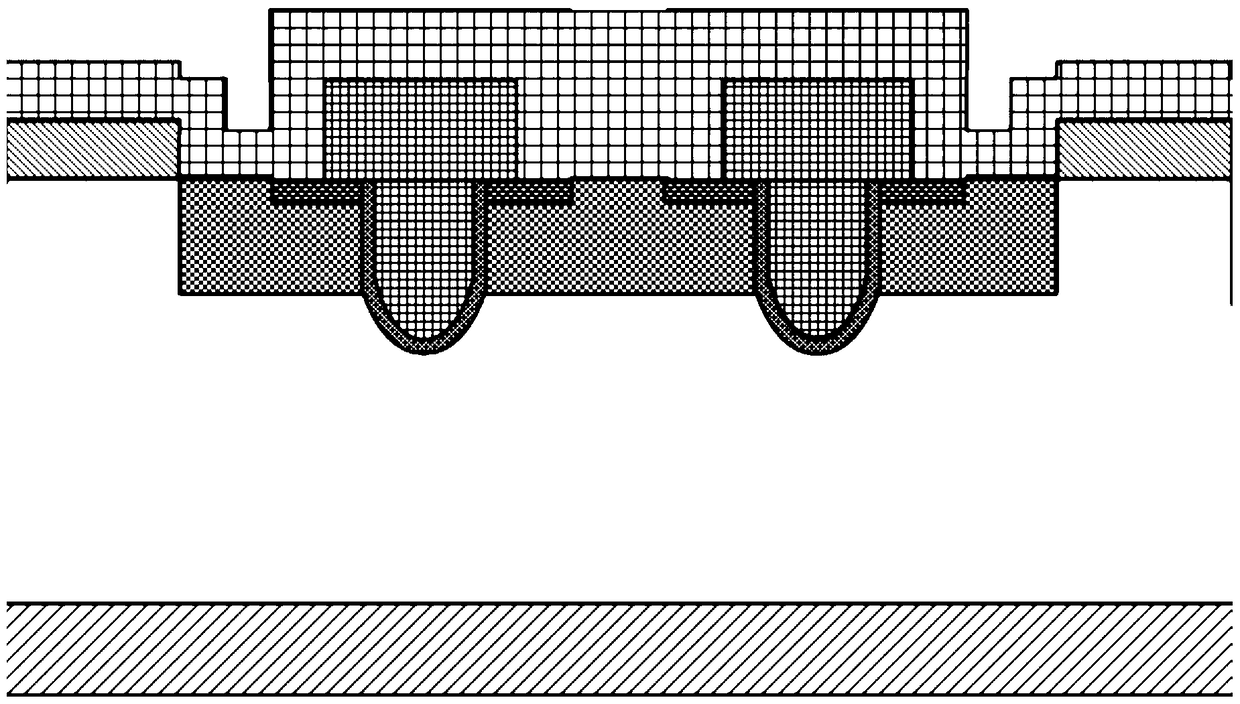

[0027] An embodiment of the present invention provides an etching method for processing a first semi-finished product used to manufacture a trench VDMOS device, the first semi-finished product includes a first substrate, and forming an epitaxial layer, in which at least a first body region is formed, in which at least a first source region and a second source region adjacent to the first source region are formed, And a first trench formed by etching down in the first source region and a second trench formed by etching down in the second source region.

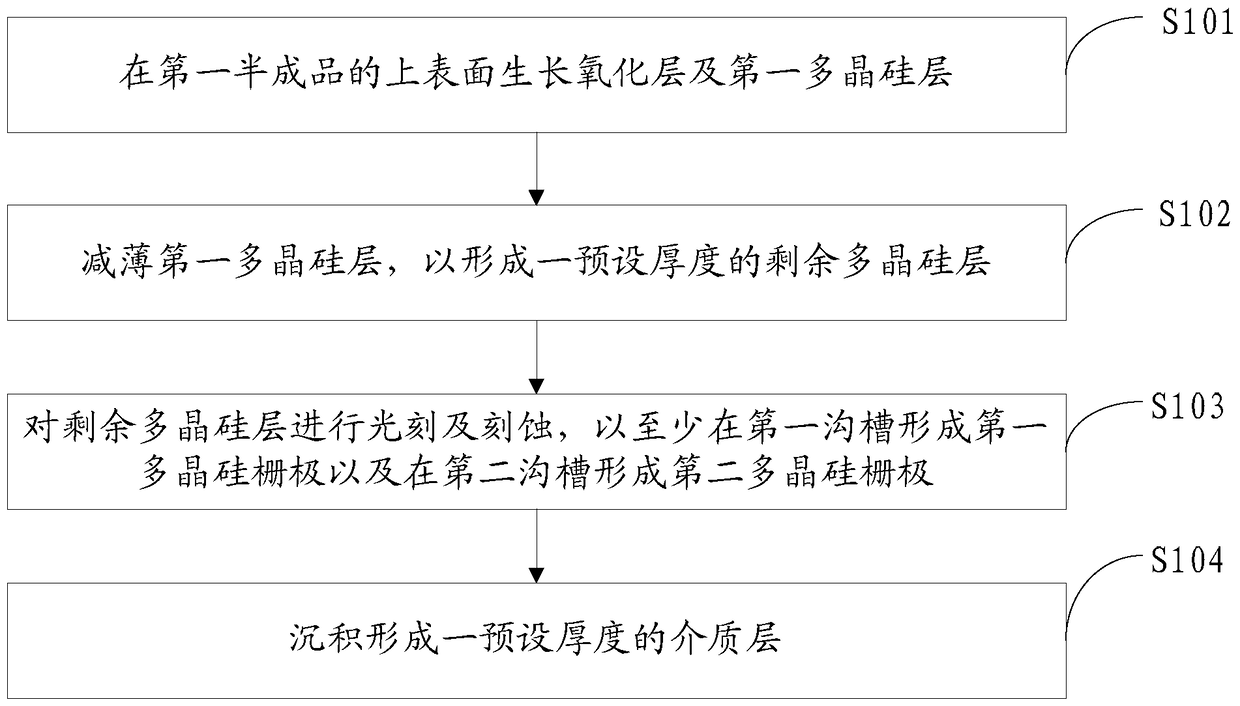

[0028] In the technical solution in the embodiment of the present invention, after growing the gate oxide layer and the first multi-silicon layer, etch the first polysilicon layer to a predetermined thickness of the remaining polysilicon layer, and then perform photolithography and etching on the remaining polysilicon layer eclipse. Because the growth thickness of polysilicon is related to the trench size, therefore, for VDMOS...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com