Static random memory unit having anti-single event effect

An anti-single event effect, memory unit technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of complex manufacturing process and large device area, and achieve extended feedback time, small parasitic capacitance, and low power consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

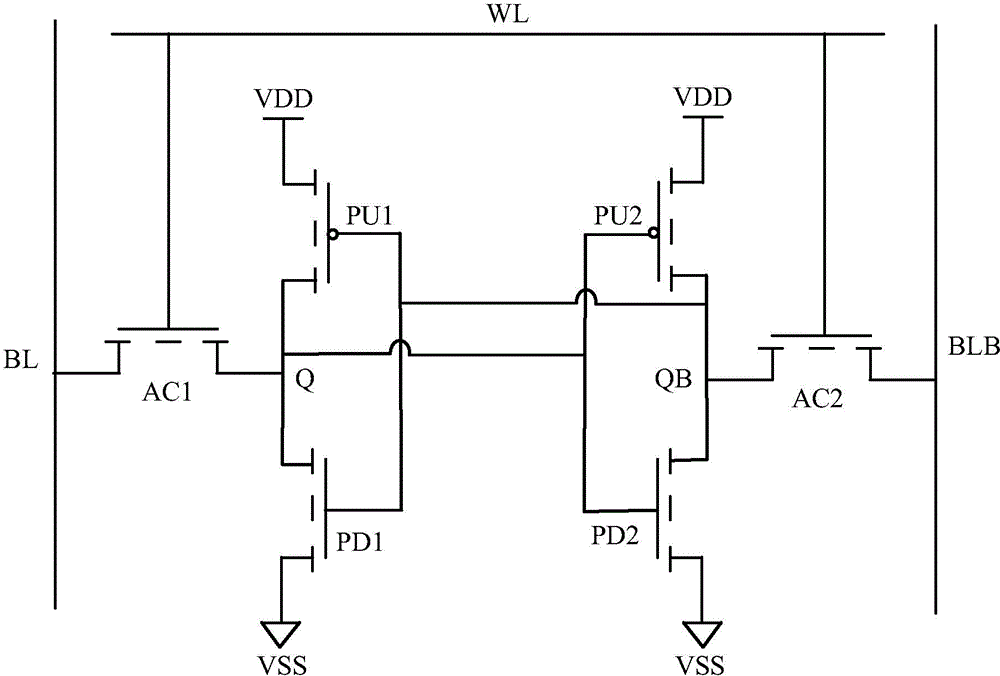

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] Such as image 3 As shown, the present invention provides a single-event-resistant SRAM unit, which at least includes: a first cross-coupled inverter 10 , a second cross-coupled inverter 20 and a transmission tube.

[0041] The first cross-coupled inverter 10 is composed of a first pull-up transistor and a second pull-up transistor. As an example, both the first pull-up transistor and the second pull-up transistor are PMOS transistors, which are denoted as PU1 and PU2 respectively. The dimensions of the two pull-up tubes are strictly matched to increase the stability of the storage unit.

[0042] The second cross-coupled inverter 20 is composed of a first pull-down transistor and a second pull-down transistor. As an example, both the first pull-down transistor and the second pull-down transistor are NMOS transistors, which are denoted as PD1 and PD2 respectively. The dimensions of the two pull down tubes are strictly matched to increase the stability of the storage uni...

Embodiment 2

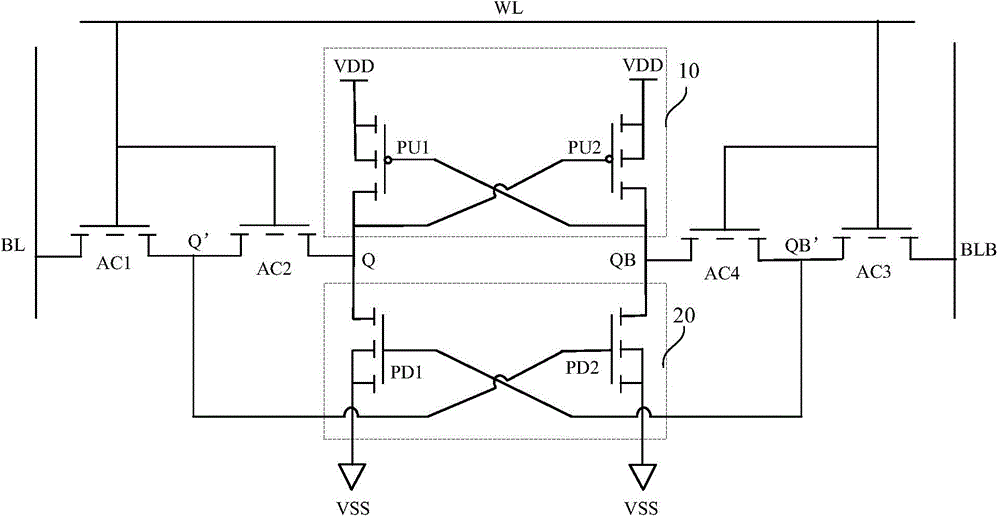

[0053] Such as Figure 4 As shown, the present invention provides another anti-single event effect SRAM unit, the memory unit at least includes: a first cross-coupled inverter 10 , a second cross-coupled inverter 20 and a transmission tube.

[0054] The first cross-coupled inverter 10 is composed of a first pull-up transistor and a second pull-up transistor. As an example, both the first pull-up transistor and the second pull-up transistor are PMOS transistors, which are denoted as PU1 and PU2 respectively. The dimensions of the two pull-up tubes are strictly matched to increase the stability of the storage unit.

[0055] The second cross-coupled inverter 20 is composed of a first pull-down transistor and a second pull-down transistor. As an example, both the first pull-down transistor and the second pull-down transistor are NMOS transistors, which are denoted as PD1 and PD2 respectively. The dimensions of the two pull down tubes are strictly matched to increase the stabili...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com