Through silicon via forming method and alignment structure of semiconductor device

A semiconductor and through-silicon via technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as metal diffusion, adverse effects on semiconductor device performance, and difficult alignment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

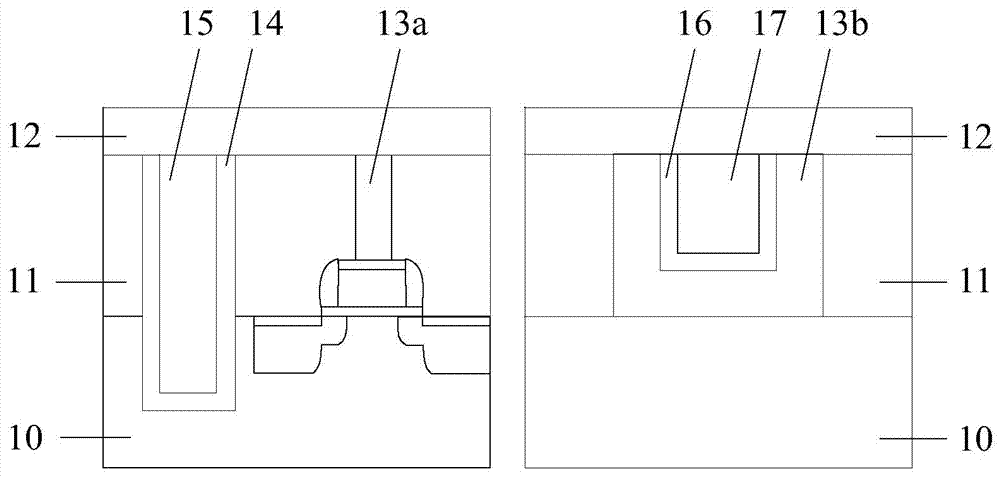

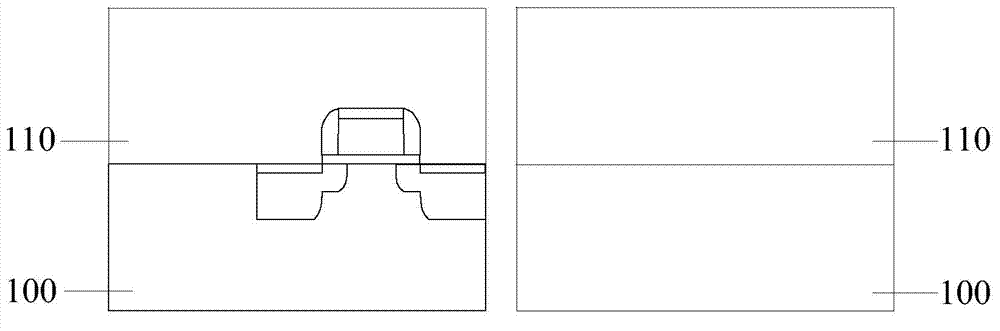

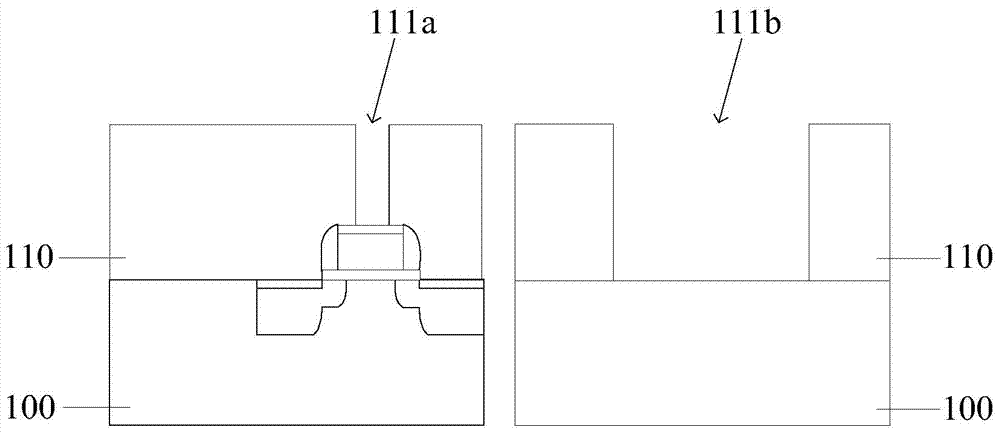

[0051]As mentioned in the background technology, in the existing through-silicon via formation method, the metal interconnection layer and the interlayer dielectric layer are directly stacked, which easily causes the metal in the metal interconnection layer to diffuse into the interlayer dielectric layer, which affects the performance of the semiconductor device. Cause adverse effects; it needs to be planarized to expose the surface of the interlayer dielectric layer to expose the conductive column, the interlayer dielectric layer is easy to be flatly removed during the planarization process and it is difficult to stop accurately; in the alignment structure, the metal layer, nitride layer and insulation The layers have flush surfaces, making quick and precise alignment difficult.

[0052] Therefore, the present invention provides a new method for forming TSVs. In the process of forming TSVs, a sacrificial layer is firstly formed to fill the grooves, thereby preventing the subse...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com