Longitudinal conduction GaN (gallium nitride) normally-off MISFET (metal-insulator-semiconductor field effect transistor) device and manufacturing method thereof

A normally-off, on-state technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as deteriorating the quality of the electron blocking layer, cleaning the mask layer, and degrading device performance. control capability, improved device performance, reduced on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

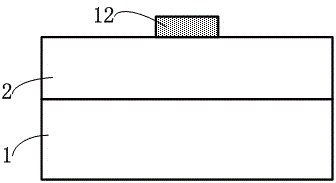

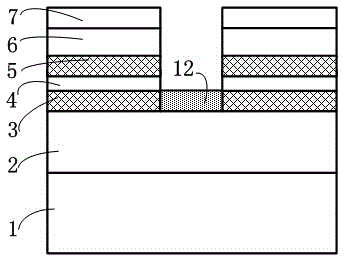

Embodiment 1

[0039] Such as Figure 9 Shown is a schematic diagram of the device structure of this embodiment, the device includes a gate, a source, a drain, an insulating layer, a conductive GaN substrate and an epitaxial layer thereon, and the epitaxial layer includes an n-type lightly doped A doped GaN layer and a secondary epitaxial layer grown on it in a selective region, the secondary epitaxial layer is an impurity filter layer 1, an electron blocking layer, an impurity filter layer 2, a non-doped epitaxial GaN layer and a heterostructure from bottom to top The barrier layer, the groove channel is formed after the second epitaxial growth, the surface of the groove channel and the heterostructure barrier layer is covered with an insulating layer, the gate is covered with the groove channel on the insulating layer, and the insulating layer is etched A source region is formed at both ends, and ohmic metal is evaporated on the source region to form a source in contact with the heterojunc...

Embodiment 2

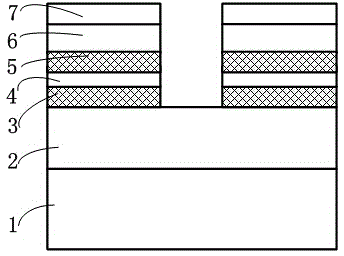

[0052] Such as Figure 10 Shown is a schematic diagram of the device structure of this embodiment, which is similar to the structure of Embodiment 1, the only difference being that an n-type heavily doped GaN layer 13 with a thickness of 10-100 nm is inserted on the n-type lightly doped GaN layer 2 . The n-type heavily doped GaN layer 13 is in direct contact with the gate channel, which can effectively diffuse the gate channel current and disperse the concentrated electric field near the gate, thereby increasing the maximum breakdown voltage of the device.

Embodiment 3

[0054] Such as Figure 11 Shown is a schematic diagram of the device structure of this embodiment, which is similar to the structure of Embodiment 1, the only difference is that an AlN layer 14 is inserted between the non-doped GaN layer 6 and the heterostructure barrier layer 7, and the AlN layer can improve heterogeneity. 2DEG mobility in the channel of the matrix structure.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com