Method for realizing server hardware acceleration by using FPGA (field programmable gate array)

A hardware acceleration and server technology, applied in the computer field, can solve problems such as low efficiency, large memory access delay, and consistency impact, and achieve the effects of strong practicability, high bus bandwidth, and improved computing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

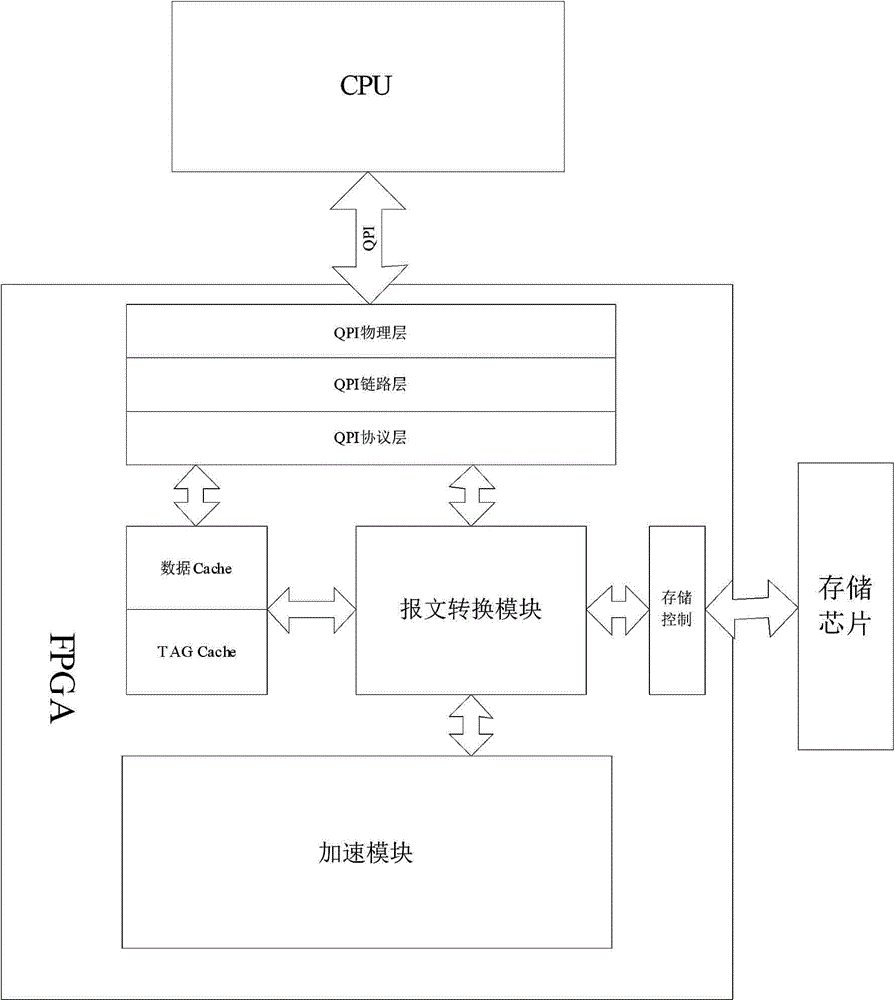

[0031] Taking the realization of an image processing accelerator as an example, first implement the image processing algorithm acceleration module in FPGA with hardware description language (HDL). Since the image data generally requires a large storage space, the memory controller can be instantiated in the FPGA and connected to the memory chip outside the FPGA as the private memory space of the FPGA. Then realize the QPI bus module, wherein the protocol table of the protocol layer can be simplified according to the system structure. Then realize the Cache module and the message forwarding module in the FPGA. The address decoding table is set in the message forwarding module, and the address that the FPGA image processing module needs to access is correctly mapped to the FPGA private memory space and the system memory space. Carry out logic synthesis, layout and routing of the hardware accelerator system described in HDL language, generate executable bit stream files and load...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com