Method for manufacturing oxide semiconductor thin film transistor array substrate

A technology of oxide semiconductor and thin film transistor, which is applied in semiconductor/solid-state device manufacturing, semiconductor device, photolithography process of patterned surface, etc., can solve the problems of rising production cost and complicated process, and achieve improved performance and low process temperature. , the effect of streamlining the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

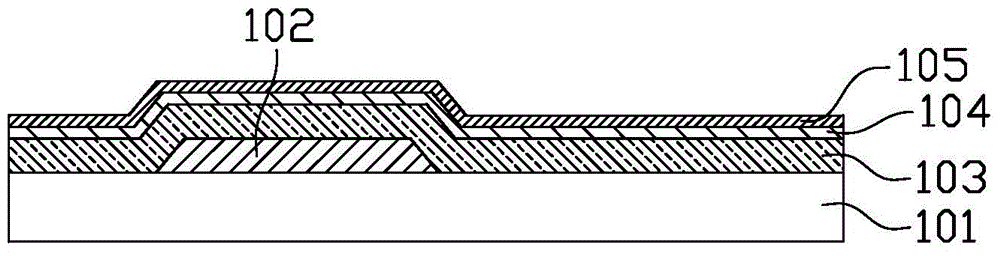

[0045] Figure 1 to Figure 8 It is a schematic cross-sectional view of the manufacturing process of the oxide semiconductor thin film transistor array substrate in the first embodiment of the present invention. The manufacturing method includes:

[0046] Such as figure 1 As shown, the gate 102 is first fabricated and formed on the base substrate 101. Specifically, the base substrate 101 is, for example, a transparent glass substrate. The gate 102 can be fabricated and formed on the base substrate 101 by a photolithography process. The photolithography process mainly includes film deposition, photoresist coating, exposure, development, and etching. Processes such as photoresist removal are well known to those skilled in the art and will not be repeated here.

[0047] Such as figure 1 As shown, a gate insulating layer 103, an oxide semiconductor layer 104, and a pixel electrode layer 105 are then deposited on the gate 102 in sequence. The material of the gate insulating layer 103 i...

no. 2 example

[0071] Figure 9 to Figure 11 This is the second embodiment of the present invention. The difference from the first embodiment is that the TFT device adopts an etching stop structure, that is, compared with the first embodiment, the oxide semiconductor layer 104 and the source electrode in the active layer region 201 111. An etch stopper layer (ESL) 115 is added between the drain electrode 112 to protect the semiconductor channel of the active layer from being damaged by the etching process of the source and drain metal layer. The process before the etching stop layer 115 is formed in this embodiment is the same as that of the first embodiment. For details, please refer to the description and description of the corresponding process in the first embodiment. Figure 1 to Figure 6 .

[0072] Before the etching stop layer 115 is formed, the oxide semiconductor layer 104 as the active layer is preferably subjected to etching damage repair treatment, such as adding O2 plasma treatment,...

no. 3 example

[0079] Figure 12 to Figure 18 This is the third embodiment of the present invention. The difference from the first embodiment lies in the process of semi-exposing the photoresist 106 coated on the pixel electrode layer 105 and the structure on the active layer.

[0080] Such as Picture 12 As shown, when the photoresist 106 is half-exposed, the half-exposed area changes from the entire active layer area 201 to the TFT back channel region, that is, only half exposure is performed on the TFT back channel region, which is equivalent to reducing the half exposure Area. In other words, the active layer region 201 can be divided into three sub-regions: the middle, the left and the right. The middle region corresponds to the TFT back channel region. In this embodiment, only the active layer region 201 is located in the middle. The photoresist 106 is half-exposed, and the photoresist 106 on the two sides (left and right) of the active layer region 201 is normally exposed (completely exp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com