Display device, array substrate, thin film transistor and fabricating method thereof

A technology of thin film transistor and manufacturing method, which is applied in the field of display devices and can solve problems such as reduction of on-state current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

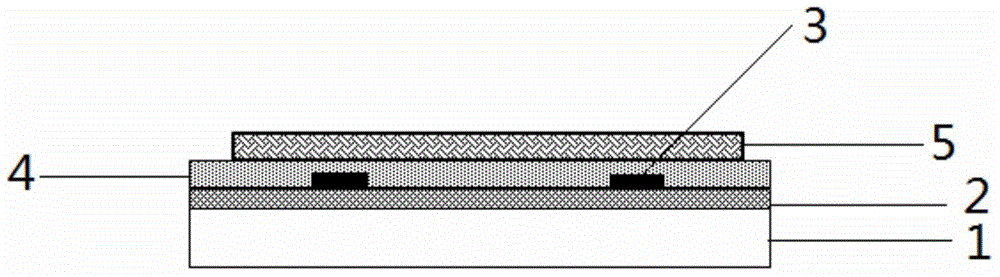

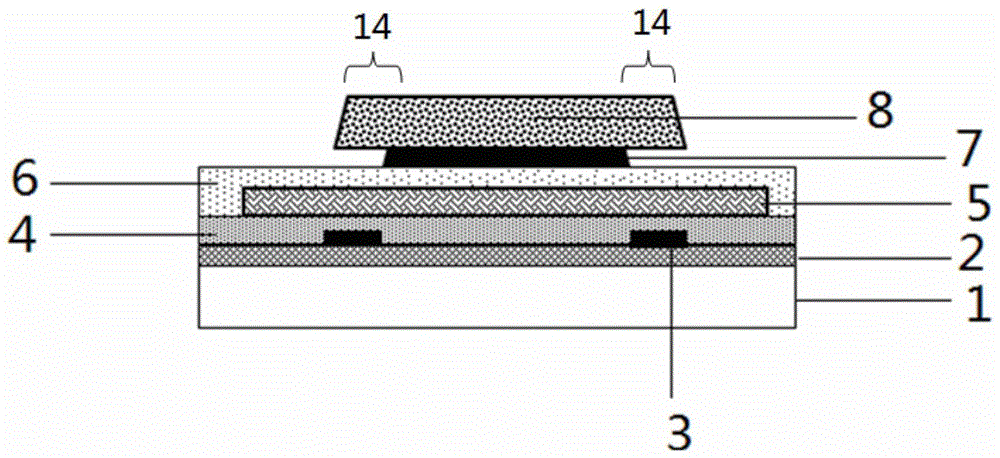

[0041] Such as Figure 6 As shown, the embodiment of the present invention provides an array substrate, including a substrate 1, on which a buffer layer 2, a first gate 3 (ie, a bottom gate) and a first gate insulating layer 4 are provided, and the first An active layer 5 is provided on the gate insulating layer 4, and a second gate insulating layer 6, a second gate 7 (i.e., a top gate), a third gate insulating layer 11, and source-drain electrodes are sequentially provided on the active layer 5. 12 , the source and drain electrodes 12 are on the third gate insulating layer 11 . The outer sides of the region of the active layer 5 corresponding to the second gate 7 are lightly doped source and drain regions 91 and 101 and heavily doped source and drain regions 92 and 102, wherein the lightly doped source region 91 The drain lightly doped region 101 is next to the second gate 7, the source heavily doped region 92 is next to the source lightly doped region 91 and the drain heavi...

Embodiment 2

[0048] Example 2 as Figure 7 As shown, the difference between this embodiment and Embodiment 1 is that there is only a part of the first gate 3 in this embodiment, and it only needs to be disposed under the lightly doped drain region 101 in the region corresponding to the drain electrode.

[0049]The first gate 3 and the second gate 7 also use the advantage of LDD to reduce the off-state current, combined with the working principle of the bottom gate structure, when the TFT is working, that is, when the top gate is applied with gate voltage, the bottom gate is also simultaneously Turn on, so that the LDD region also induces carriers, so that the LDD region can avoid the decrease of the on-state current Ion due to the light doping under the action of the bottom gate electric field and the carriers generated by light doping. Similarly, when the top gate electric field of the TFT is removed, it is in the off state, and the bottom gate also removes its electric field at this time...

Embodiment 3

[0052] Such as Figure 8 As shown, the embodiment of the present invention also provides a manufacturing method based on the array substrate in Embodiment 1, and the specific steps include:

[0053] Step S31, forming the pattern of the first gate on the substrate;

[0054] Step S32, forming a first gate insulating layer on the substrate after the above steps;

[0055] Step S33, forming an active layer on the substrate after the above steps,

[0056] Step S34, forming a second gate insulating layer on the substrate after the above steps;

[0057] Step S35, forming a second gate pattern on the substrate after the above steps;

[0058] Step S36, performing heavy source-drain doping and light source-drain doping on the outside of the region of the active layer corresponding to the second gate; the source lightly doped region and the drain lightly doped region are adjacent to the second gate In the corresponding active layer, the source heavily doped region is adjacent to the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com