Formation method for double-shallow trench isolator

A technology of double shallow trench isolation and shallow trench, which is applied in the field of formation of double shallow trench isolation, can solve the problems of silicon crystal lattice damage, poor device performance, leakage current image degradation, etc., and achieve good morphology, Improved dimensional uniformity and prevents shape instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] As mentioned in the background art, the shallow trench isolation used in the pixel area is inconsistent with the depth of the shallow trench isolation in the logic area.

[0030] In order to make the corresponding double shallow trench isolation, an existing method such as Figures 1 to 4 shown.

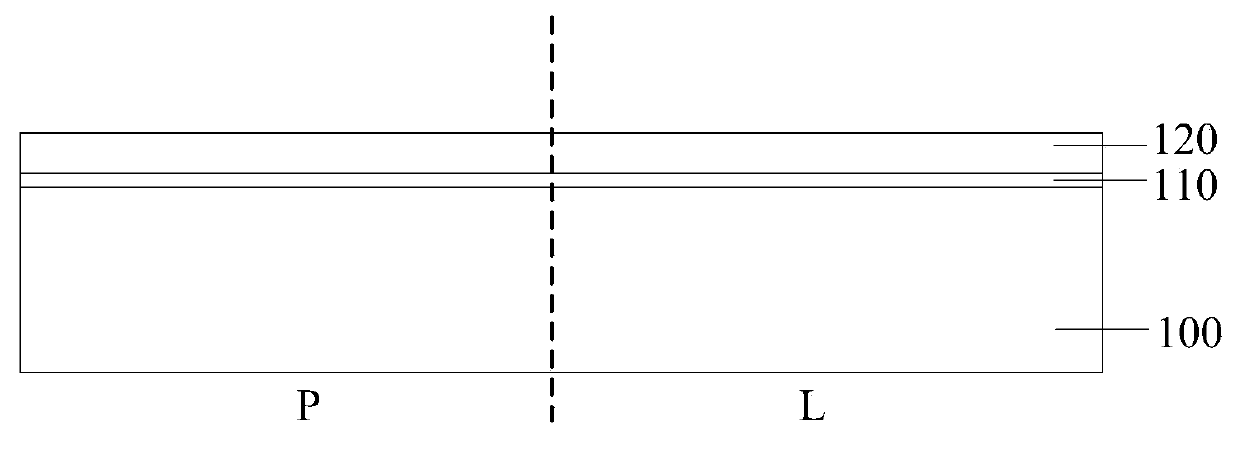

[0031] Please refer to figure 1 , a substrate 100 is provided, and the substrate 100 includes a pixel region P and a logic region L. A silicon oxide layer 110 is formed on the substrate 100 , and a silicon nitride layer 120 is formed on the silicon oxide layer 110 .

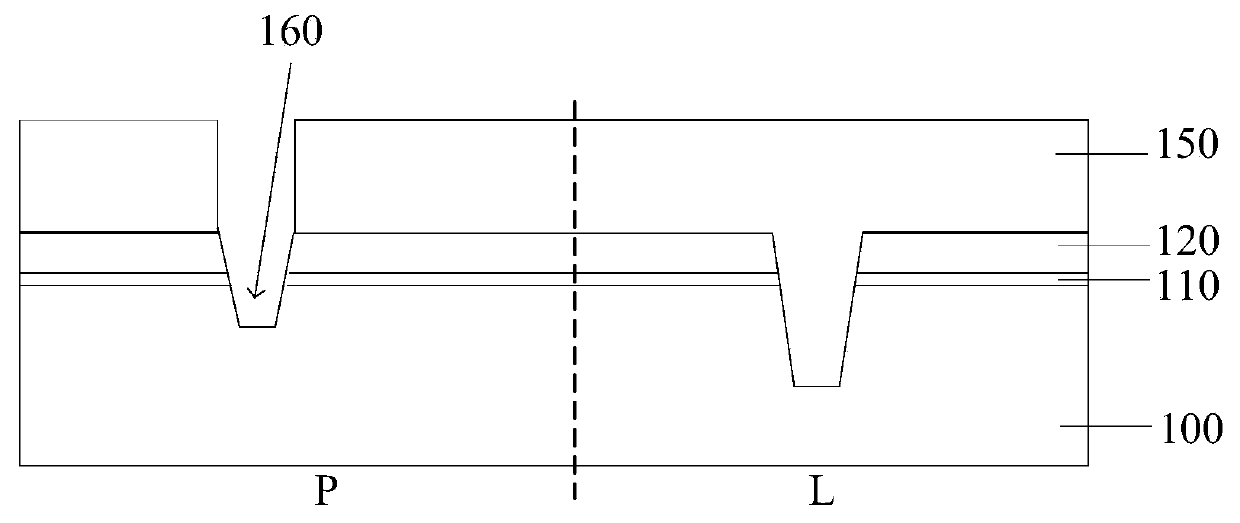

[0032] Please refer to figure 2 , forming a first photoresist layer 130 on the silicon nitride layer 120, performing processes such as exposure and development on the first photoresist layer 130 to form an opening (not marked) on the logic region L, and using the first photoresist layer 130 with the opening A photoresist layer 130 is used as a mask to etch the silicon nitride layer 120, silicon oxide layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com