Forming method of fin field effect transistor

A fin-type field effect and transistor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of different rectangular shapes, irregular shapes of embedded source/drain regions 104, easy contact, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

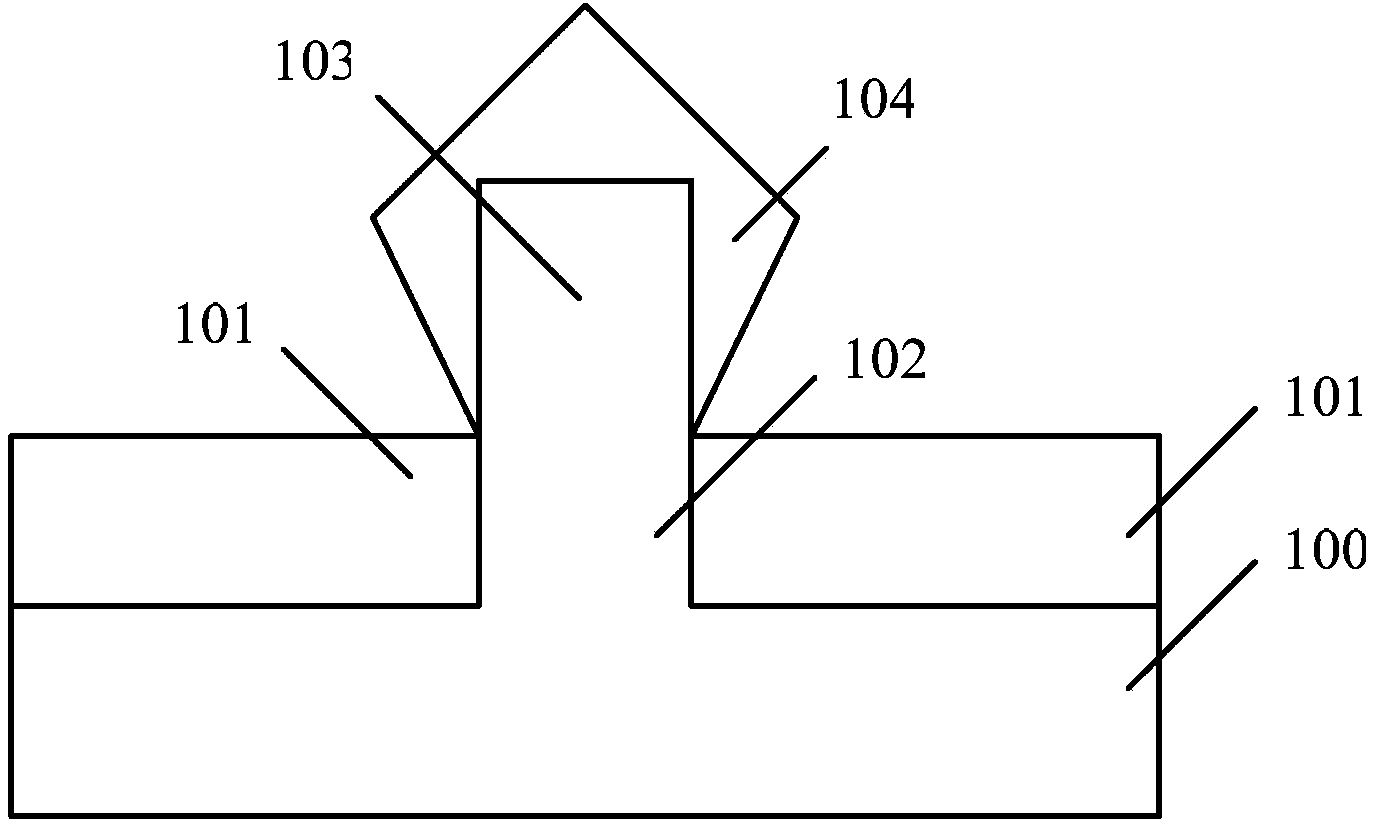

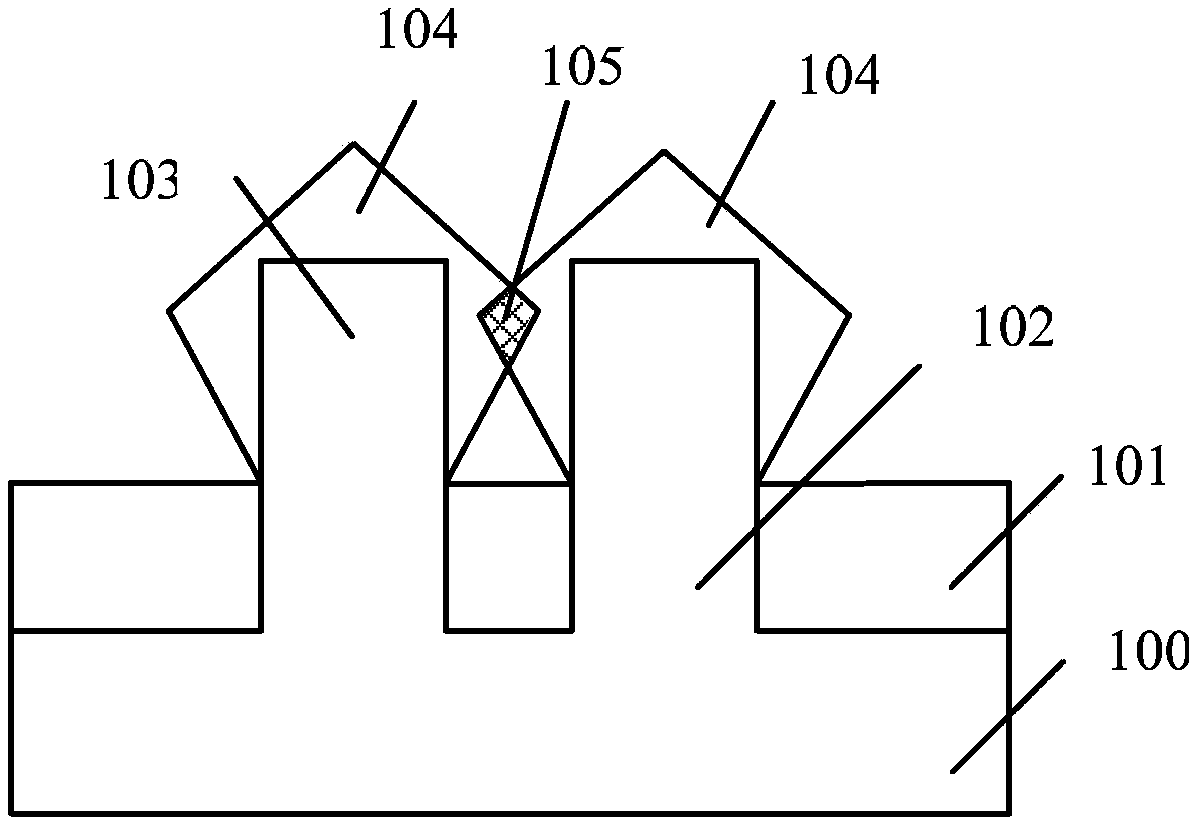

[0035] It can be seen from the background art that when forming FinFETs with embedded source and drain regions in the prior art, the embedded source / drain regions of two adjacent FinFETs are easily contacted, resulting in leakage current.

[0036] The inventors of the present invention have found that the gap between the embedded source / drain regions of two adjacent fin field effect transistors in the prior art is Therefore, it is easy to contact because when the epitaxial layer is formed, the growth rate of the semiconductor material on different crystal planes is different, resulting in an irregular shape of the formed epitaxial layer, with corners and protruding tips.

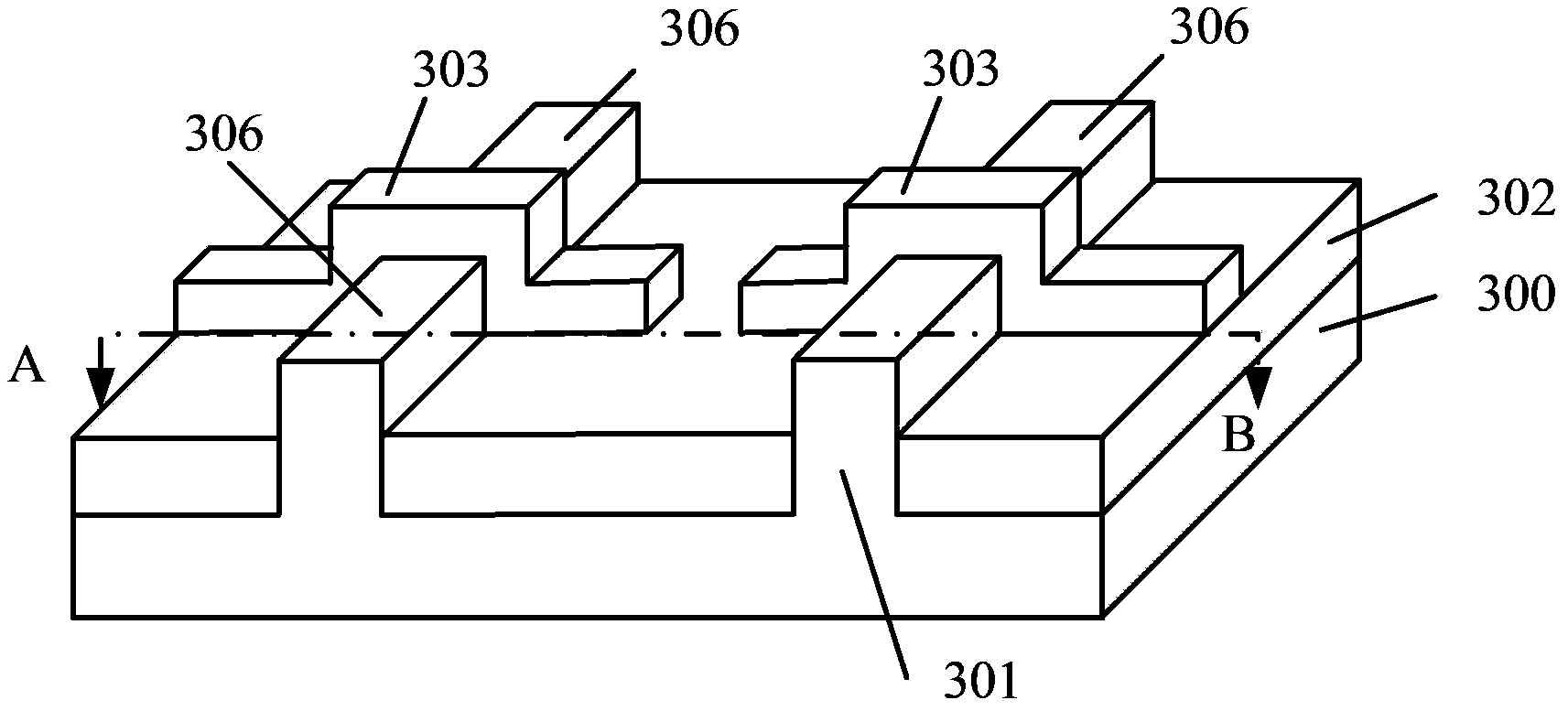

[0037] In order to solve the above problems, the inventors of the present invention provide a method for forming a fin field effect transistor. After selectively epitaxially forming a semiconductor layer on the source / drain region, and then forming a fin covering the semiconductor substrate, forming a sacrif...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com