A kind of tin oxide superlattice barrier semiconductor transistor

A superlattice and semiconductor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as inability to effectively reduce electronic potential energy fluctuations, uneven strain field distribution, and insufficient smoothness of the barrier layer surface, etc., to achieve smoothness Effects of HEMT morphology, low dislocation density, and high electrical conductivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

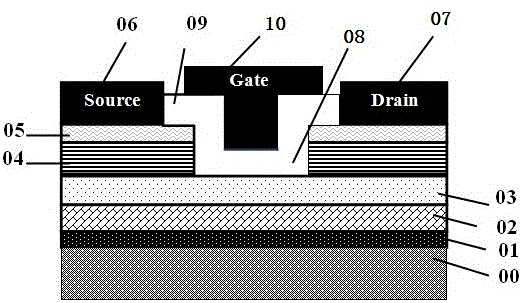

[0028] Such as figure 1 Shown, a kind of tin oxide superlattice barrier semiconductor transistor, its structure comprises:

[0029] High-purity single crystal substrate 00;

[0030] A thin layer of Au01 evaporated on the single crystal substrate 00;

[0031] A buffer layer 02 formed on a single crystal substrate 00 containing an Au-plated layer 01;

[0032] A high-mobility channel layer 03 formed on the buffer layer 02;

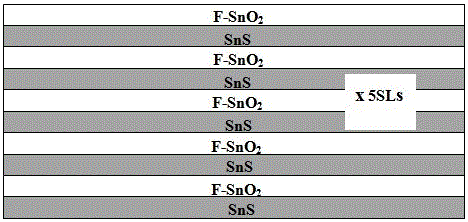

[0033] 5 periods of superlattice barrier layers 04 formed on the high-mobility channel layer 03;

[0034] A narrow bandgap ohmic contact layer 05 formed on the superlattice barrier layer 04;

[0035] A source metal electrode 06 and a drain metal electrode 07 formed on the narrow bandgap ohmic contact layer 05;

[0036] Between the source metal electrode 06 and the drain metal electrode 07, the five-period superlattice barrier layer 04 is etched, and etched to the surface of the high-mobility channel layer 03 to form a gate groove structure 08;

[0037]...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com