High-speed parallel OQPSK demodulation clock restoring system

A technology for recovering system and clock, applied in the field of communication, can solve problems such as large resource occupation, large number of parallel paths, complex implementation structure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

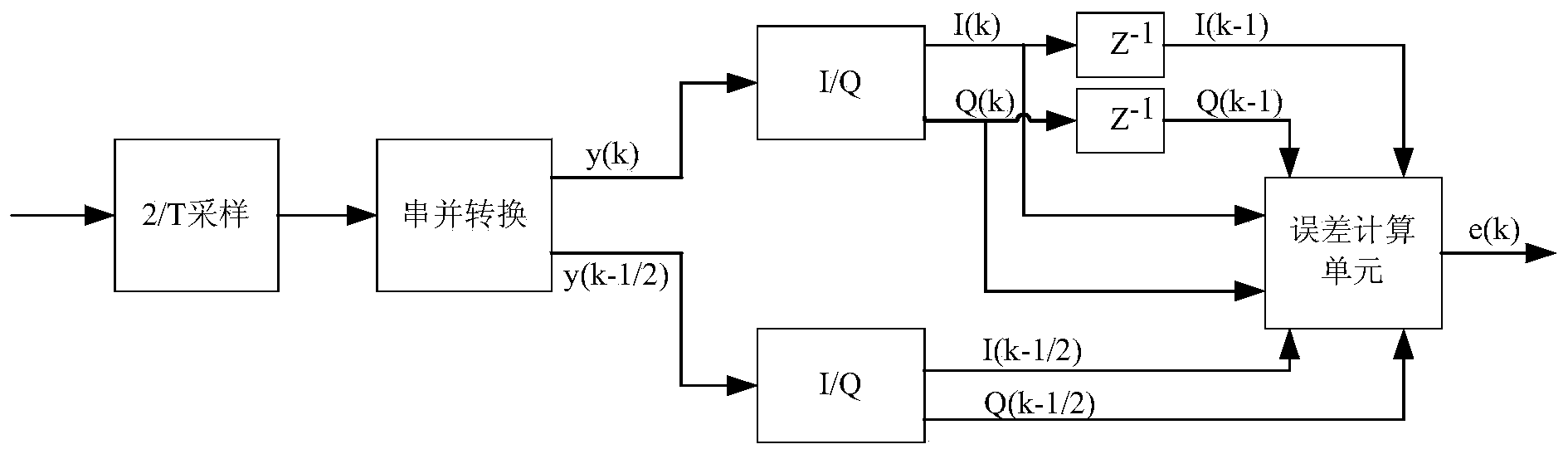

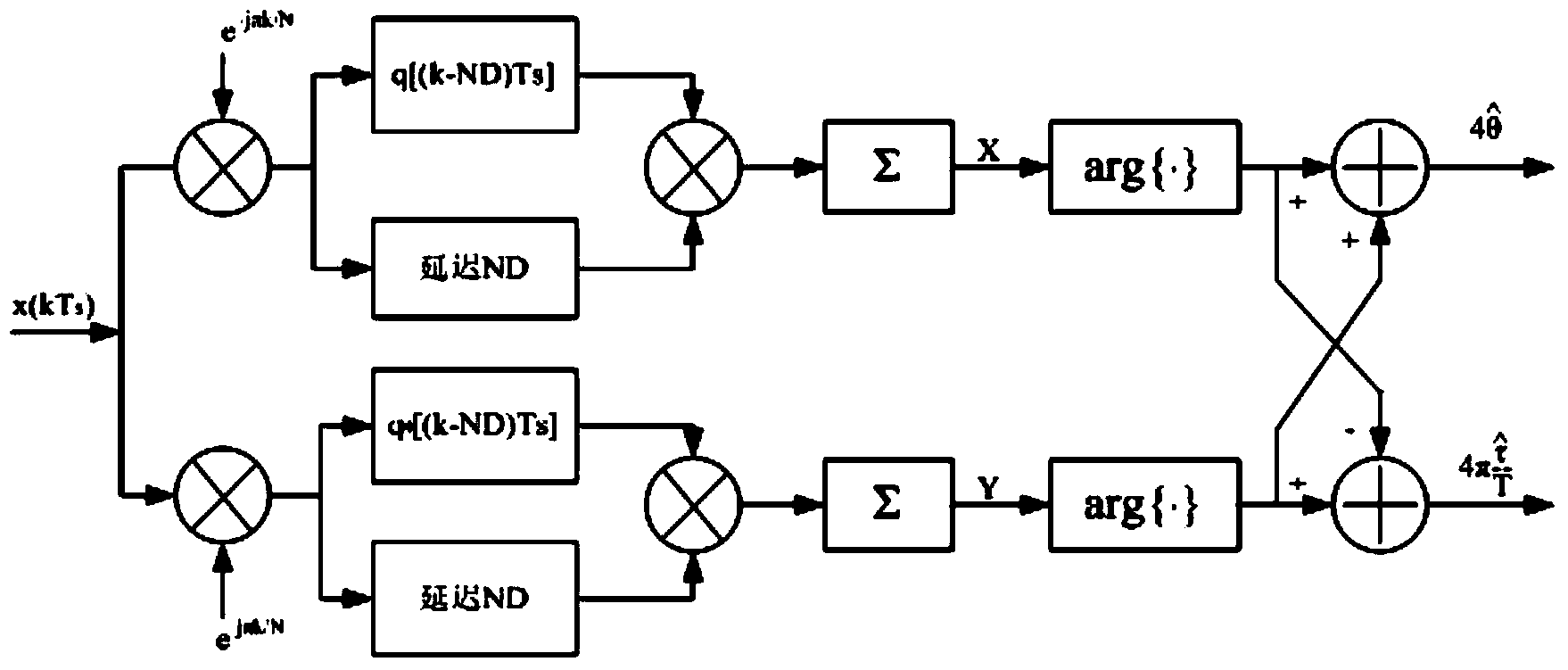

[0036] For the demodulation of high-speed OQPSK signals, limited by the internal processing clock of the device, a parallel clock recovery method is required. Under the condition that the highest frequency of the device remains unchanged, if the single-channel data is processed in N channels in parallel, the demodulation code rate can be increased by N times. Of course, the resources required by the parallel structure relative to the single channel are also correspondingly increased by N times. So this is actually a strategy of exchanging resources for speed.

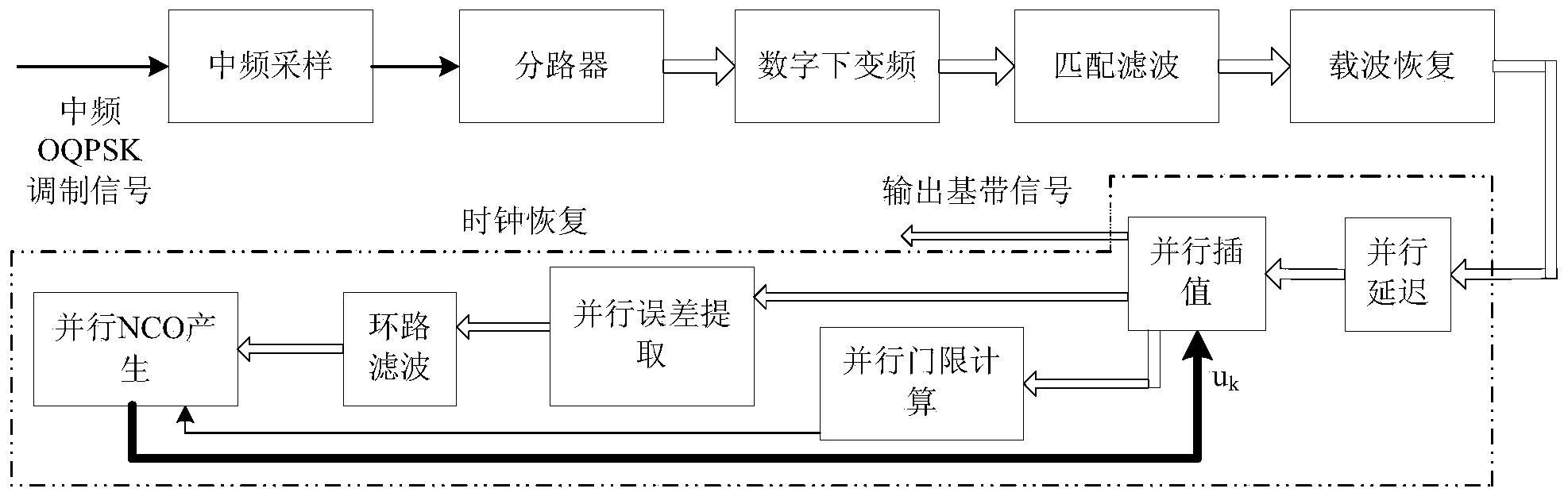

[0037] In the following, the structure of the parallel clock recovery system of the present invention will be introduced through the functional block diagram of the high-speed parallel digital receiver. Such as image 3 As shown, the intermediate frequency OQPSK modulated signal is demodulated and received by the method of coherent demodulation. First, the high-speed OQPSK modulation signal is converted to an intermed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com