A kind of flexible znO-based thin film transistor and preparation method thereof

A technology of thin film transistors and flexible substrates, applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of not using photolithographic patterns, poor surface flatness, and easy aging of devices, so as to enhance operability and use Reliability, enhanced water and oxygen barrier properties, and the effect of solving flexible bending shrinkage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

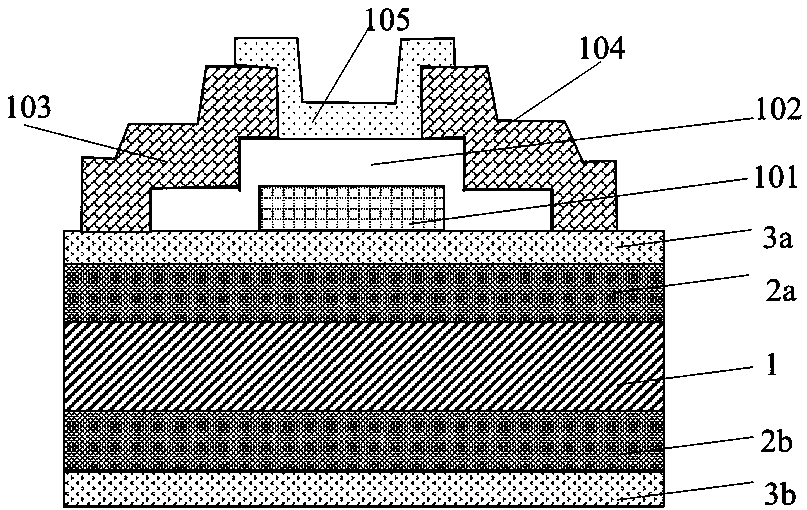

[0046] Such as figure 1 As shown, the manufacturing process of the bottom gate and bottom contact zinc oxide thin film transistor of the present invention includes the following steps:

[0047] a) Pretreatment of flexible substrate;

[0048] b) Lift-off process to deposit gate electrode film (101);

[0049] c) Depositing gate insulating material (102);

[0050] d) forming a gate insulating layer pattern by photolithography;

[0051] e) Source and drain electrodes (103,104) deposited by Lift-off process;

[0052] f) The ZnO semiconductor layer (105) is spin-coated from inorganic solution;

[0053] g) Obtaining the channel region pattern by wet etching by photolithography.

[0054] In step a), the pretreatment of the flexible substrate is the same as above.

[0055] In the step b), the lift-off process specifically includes adopting red positive glue, spin coating at 5000 rpm for 30 seconds, baking for 10 minutes before 95°C, exposure for 40 seconds, developing for 20-40 seconds, and baking f...

Embodiment 2

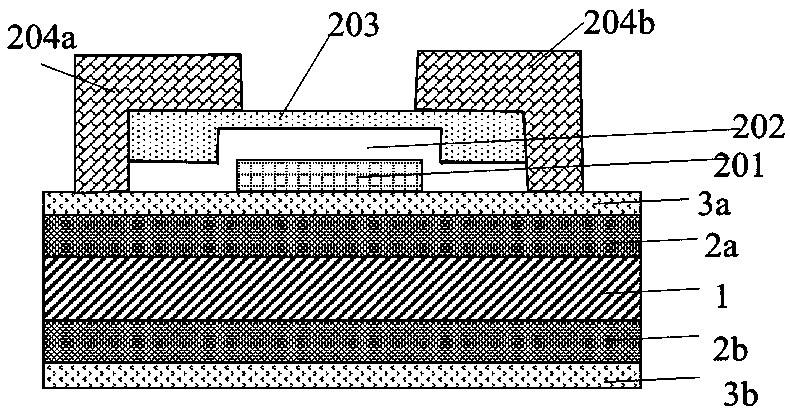

[0076] Bottom-gate and top-contact thin film transistor preparation methods: 1. Substrate pretreatment; 2. Deposition of gate electrode 201; 3. Deposition of gate insulating layer 202; 4. Deposition of ZnO semiconductor channel layer 203; 5. Deposition Product source and drain (204a, 204b). In this method, the gate insulating layer and the channel layer can be patterned by simultaneous photoetching with a set of lithography plates. The gate electrode and the source and drain electrodes are made by the Lift-off process. This structure can avoid the effect of the annealing process on the source and drain electrodes.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com