Semiconductor device comprising junction type filed effect transistor and manufacturing method thereof

A technology of field effect transistors and semiconductors, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as reducing the pinch-off voltage of JFET

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Exemplary embodiments of the present invention will be fully described below with reference to the accompanying drawings. In the various figures, the same elements are indicated with similar reference numerals. For clarity, various parts in the drawings are not drawn to scale, and detailed descriptions of some specific structures and functions are simplified. In addition, similar structures and functions that have been described in detail in some embodiments will not be repeated in other embodiments. Although terms of the present invention are described in conjunction with specific exemplary embodiments, these terms are applicable to any reasonable occasion in the art and should not be construed as being limited to the exemplary embodiments set forth herein.

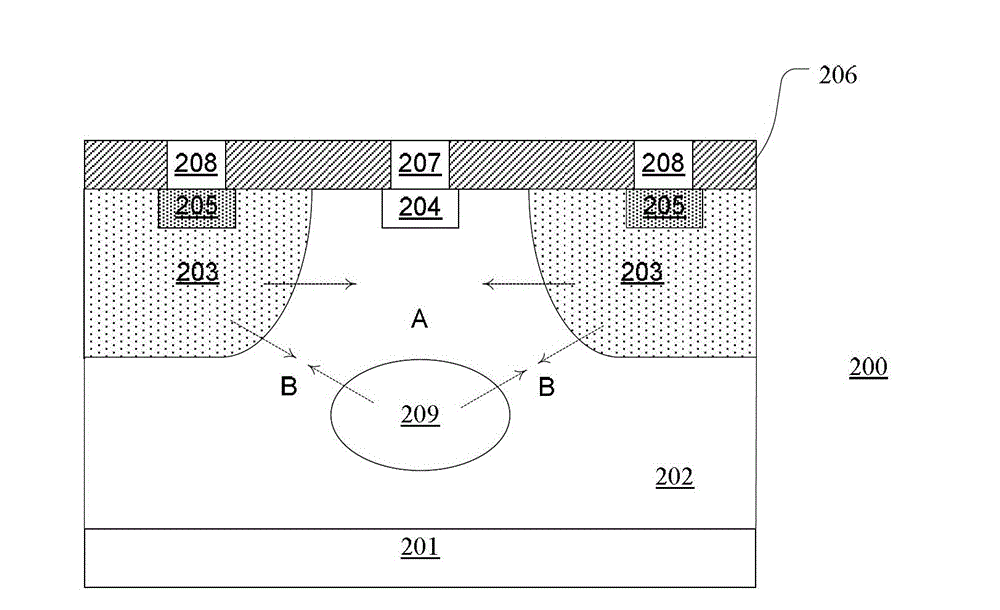

[0021] figure 2 is a cross-sectional view of a junction field effect transistor (JFET) 200 in accordance with one embodiment of the invention. exist figure 2 In, use with figure 1 Like reference numbers den...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com