Transistor forming method

A transistor and gate structure technology, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of unsatisfactory transistor performance, high junction capacitance and junction current, improve standard and reduce junction leakage current. , the effect of improving device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

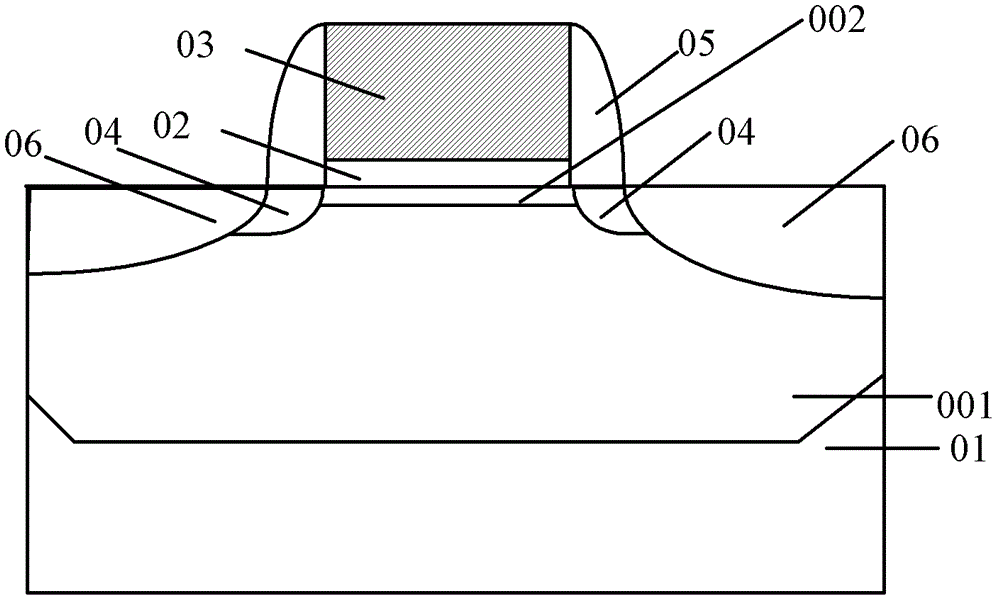

[0032] The inventors found that, in theory, the ions for adjusting the threshold voltage only need to be distributed near the substrate surface below the gate oxide layer, but the threshold voltage ion implantation of the prior art is very important in the process of forming the gate structure and the source and drain regions. However, there is a high-temperature environment or heat treatment process in the formation of the gate structure and the source and drain regions, which will strengthen the diffusion of ions that adjust the threshold voltage, making the ions diffuse into the substrate, increasing the source / drain region and the substrate. The junction capacitance between the bottoms increases the junction leakage current and reduces the operating speed and performance of the device.

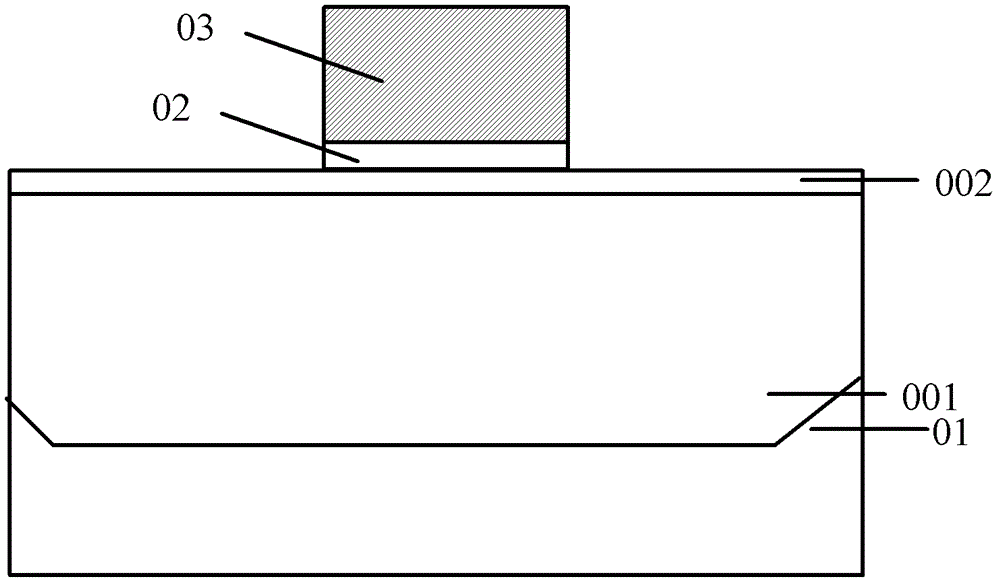

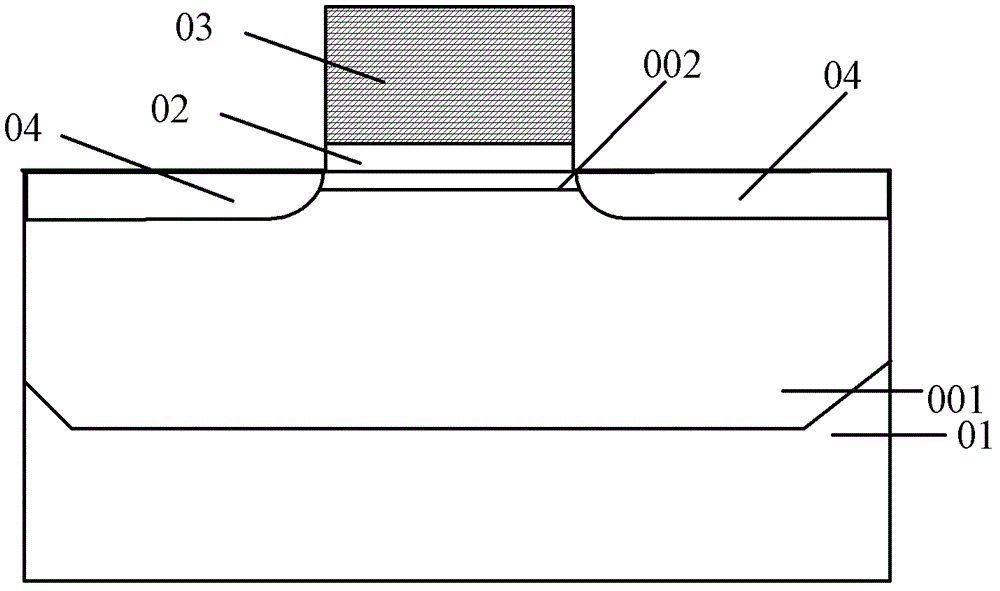

[0033] In order to solve the above problems, the inventor provides a method for forming a transistor, including: providing a substrate; forming a well region in the substrate; forming a gat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com