Method and system for design rule checking of integrated circuit layout

A technology of integrated circuit and layout design, applied in computing, electrical digital data processing, special data processing applications, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

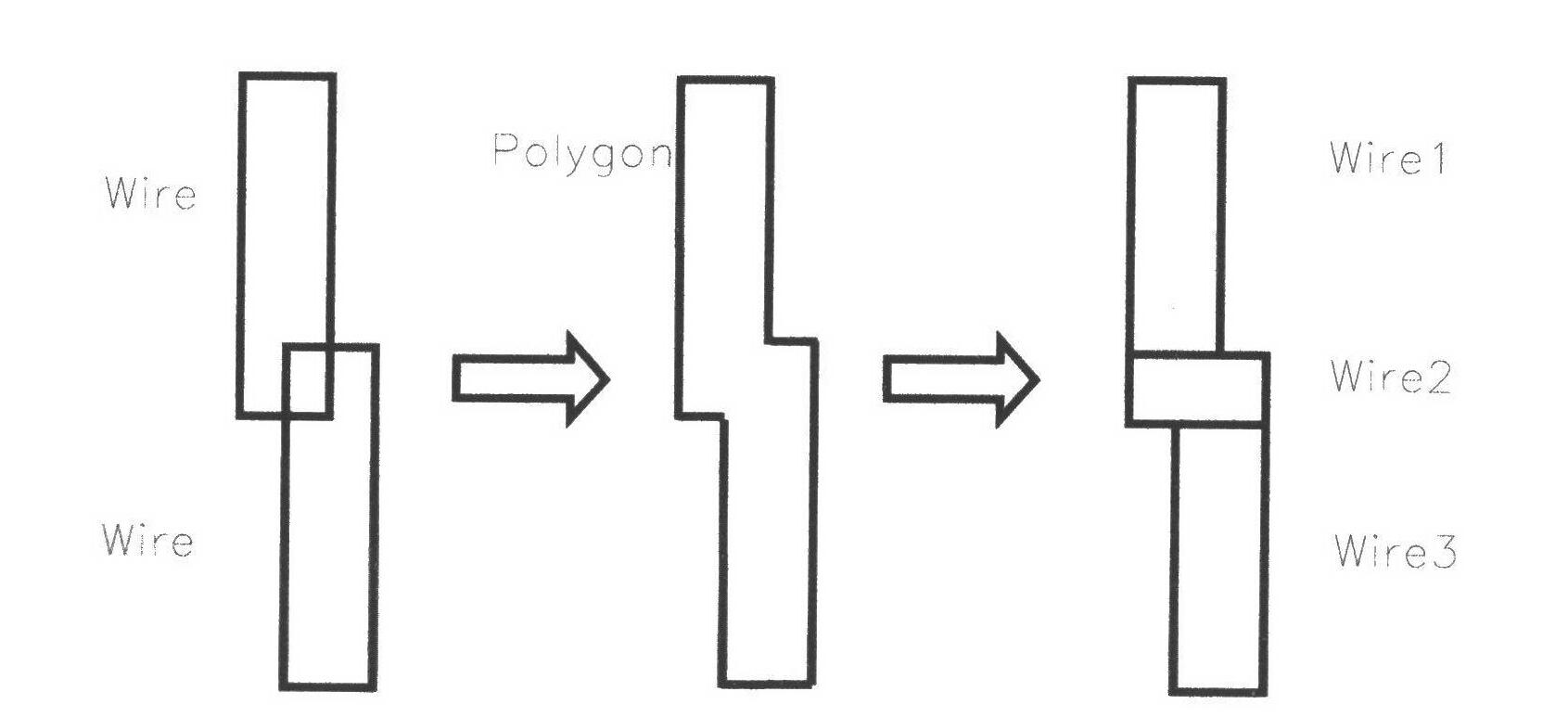

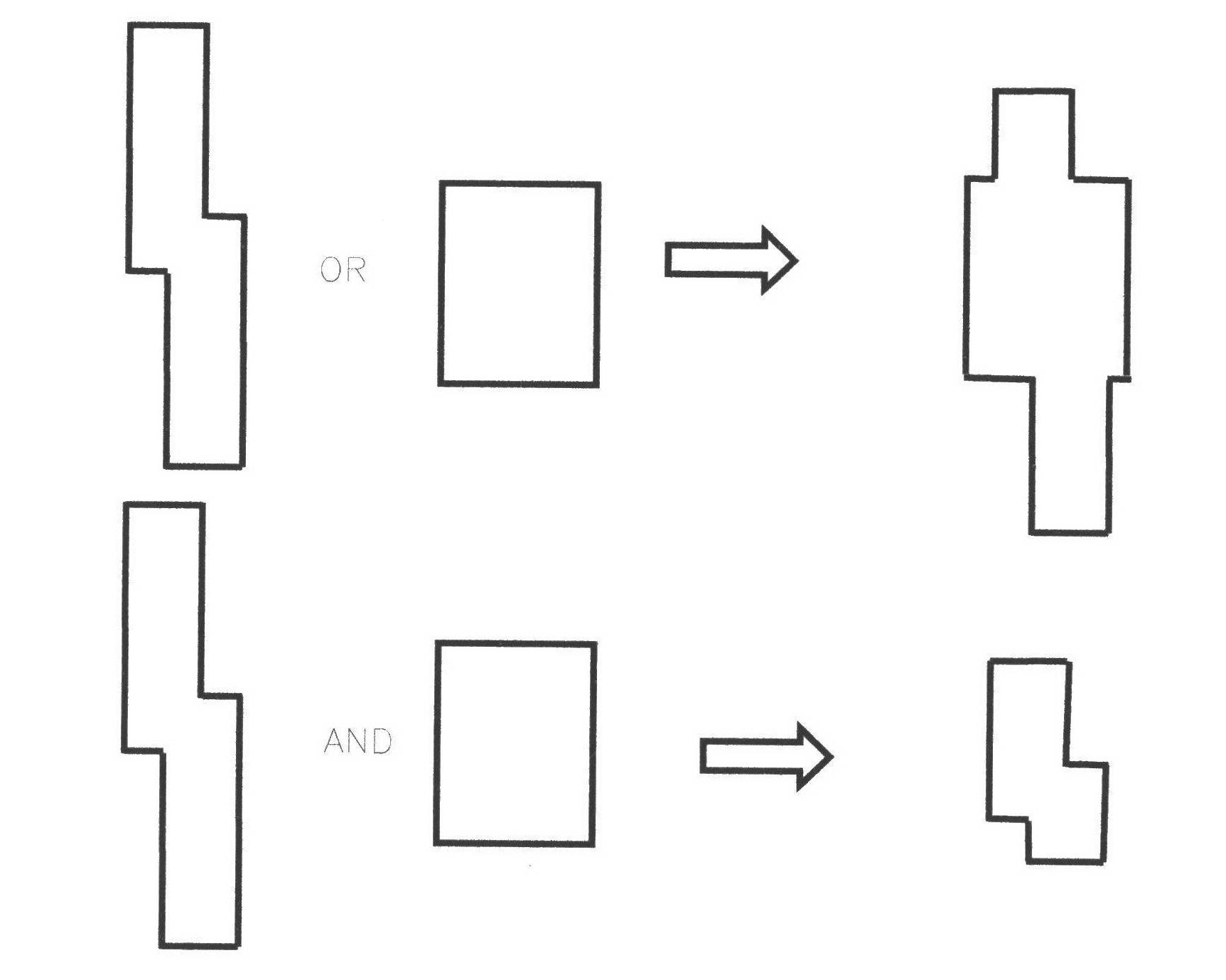

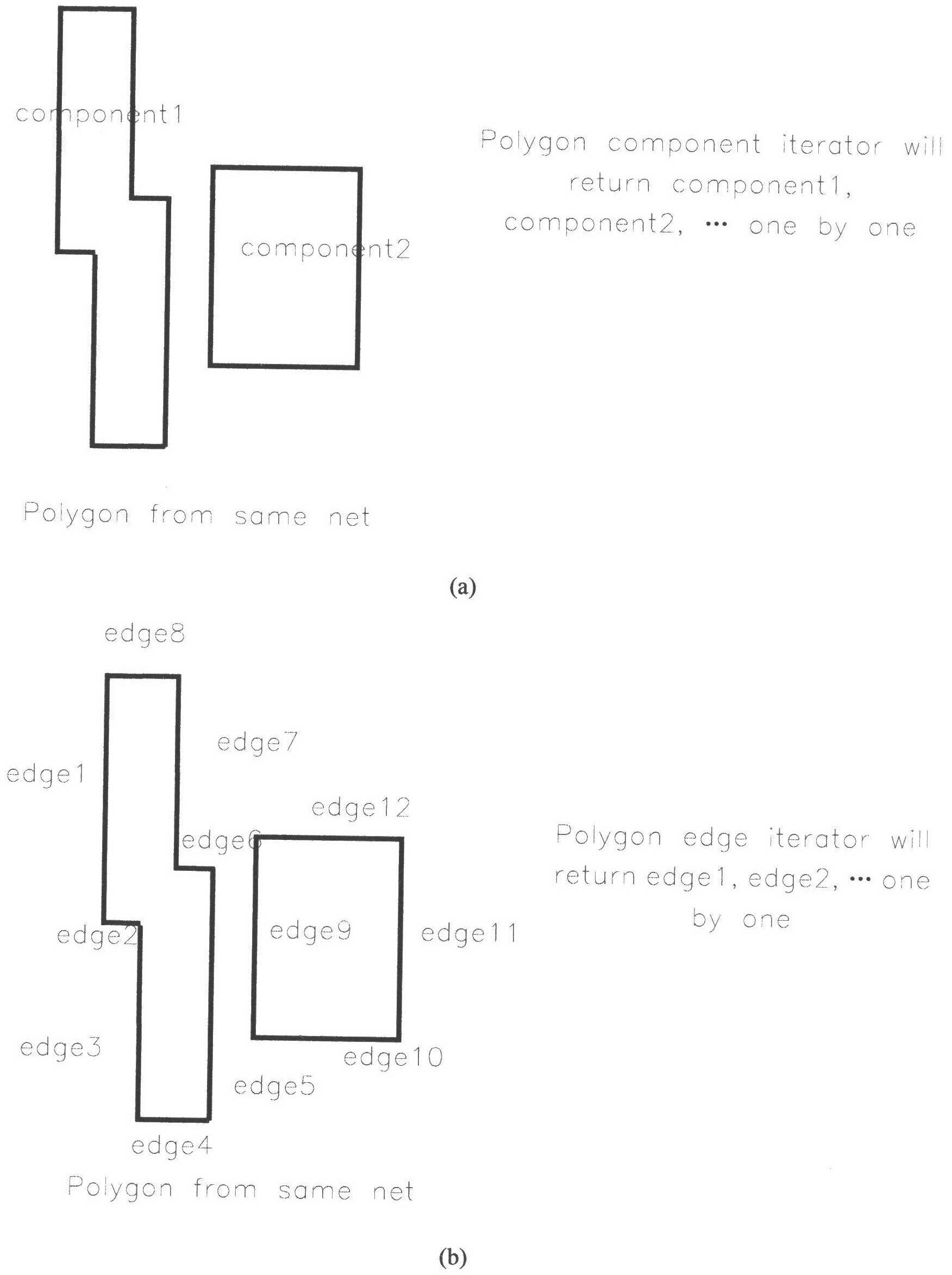

[0031] This embodiment designs a method for checking layout design rules of an integrated circuit based on polygon operations. For the input layout graph, this method abstracts it into a polygonal data representation defined by a series of horizontal boundaries, and provides an interface to convert between the rectangular traces generated by automatic routing and the layout polygons, such as figure 1 shown. At the same time, this method defines and implements the addition (UNION), subtraction (SUBSTRACT), and (AND) operation methods between polygons (see figure 2 ), and enumeration traversal operation methods for polygon connected regions and boundary edges, such as image 3 shown. On this basis, the routing tool can conveniently construct and delete layout polygons, and traverse polygon coverage rectangles and boundary edges according to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com