SCR (Silicon Controlled Rectifier) structure for providing ESD ( Electro-Static discharge) protection for I/O (Input/Output) port of integrated circuit under all modes

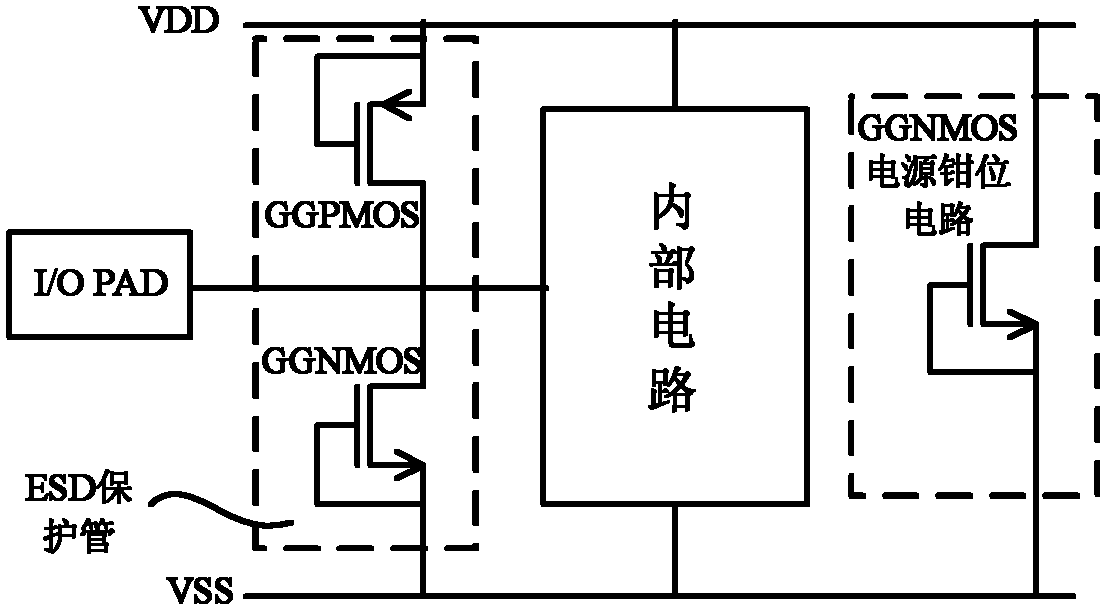

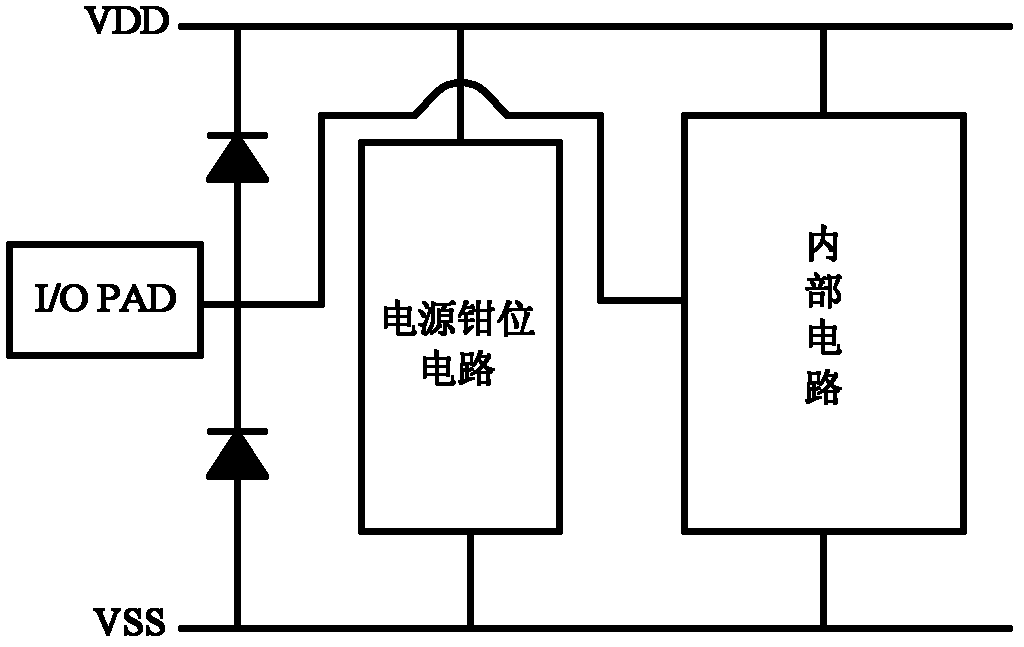

An ESD protection and integrated circuit technology, applied in the electronic field, can solve the problems of increased primary breakdown voltage, increased on-resistance, and increased voltage of devices, and achieves the effects of ESD protection, small parasitic capacitance, and high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

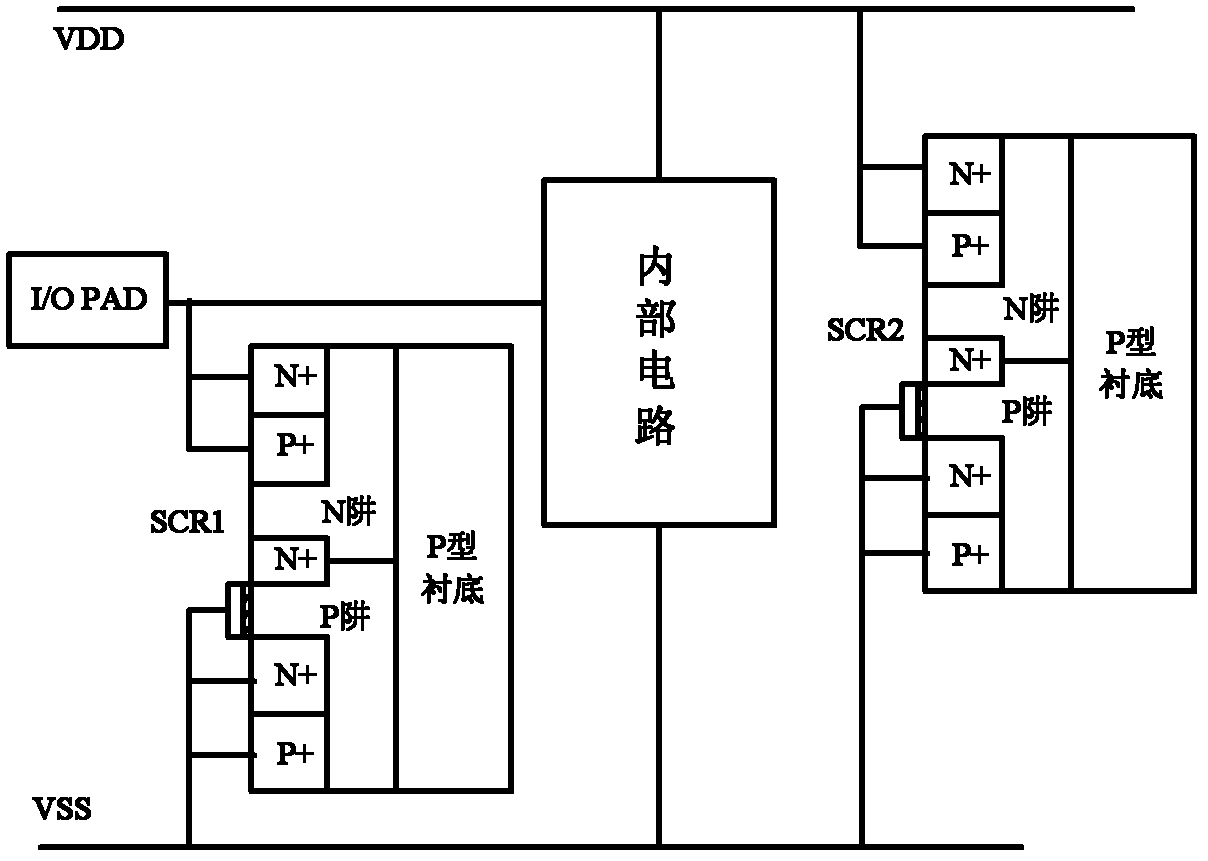

[0031] An SCR structure that provides full-mode ESD protection for integrated circuit I / O ports, such as Figure 4 As shown, it includes one P well region, two N well regions, three P+ regions and five N+ regions located on the substrate surface, and the P well region is sandwiched between two N well regions; the first N well region The middle of the top is the first P+ region, the top of the first N well region away from the P well region is the first N+ region; the middle of the top of the second N well region is the second P+ region, and the top of the second N well region is far away from the P well region One side of the top of the P well region is the second N+ region; the middle of the top of the P well region is the third N+ region on the side close to the first N well region, and the middle of the top of the P well region is the third P+ region on the side close to the second N well region; the fourth N+ The region is located in the region where the top of the first N...

specific Embodiment approach 2

[0032] Such as Figure 5 shown in Figure 4 On the basis of the technical solution shown, a sixth N+ region is added between the third P+ region and the second polysilicon region on the top of the P well region, which is close to the second N well region, and the first and second polysilicon regions are The crystal silicon region, the third and sixth N+ regions and the third P+ region are all connected to the VSS rail in the dual power rails of the protected integrated circuit chip through metal wires.

specific Embodiment approach 3

[0033] Such as Image 6 shown in Figure 4 On the basis of the technical solution shown, the third N+ region and the third P+ region are taken as a whole and rotated 90 degrees to the left or right in a manner parallel to the surface of the entire SCR structure, so that the third N+ region and the third P+ region are formed along the device The parallel arrangement in the length direction is changed to parallel and staggered arrangement along the width direction of the device (such as Image 6 (b) shown); and the first and second polysilicon regions, the third N+ region, and the third P+ region are all connected to the VSS rail in the power supply double rail of the protected integrated circuit chip through metal wires.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com