MOS transistor and manufacturing method thereof

A technology of a MOS transistor and a manufacturing method, which is applied to the field of MOS transistors and their manufacturing, can solve the problems of large leakage current of MOS transistors, slow device response speed, large junction capacitance, etc., so as to reduce the junction capacitance, improve the response speed, and reduce the size Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

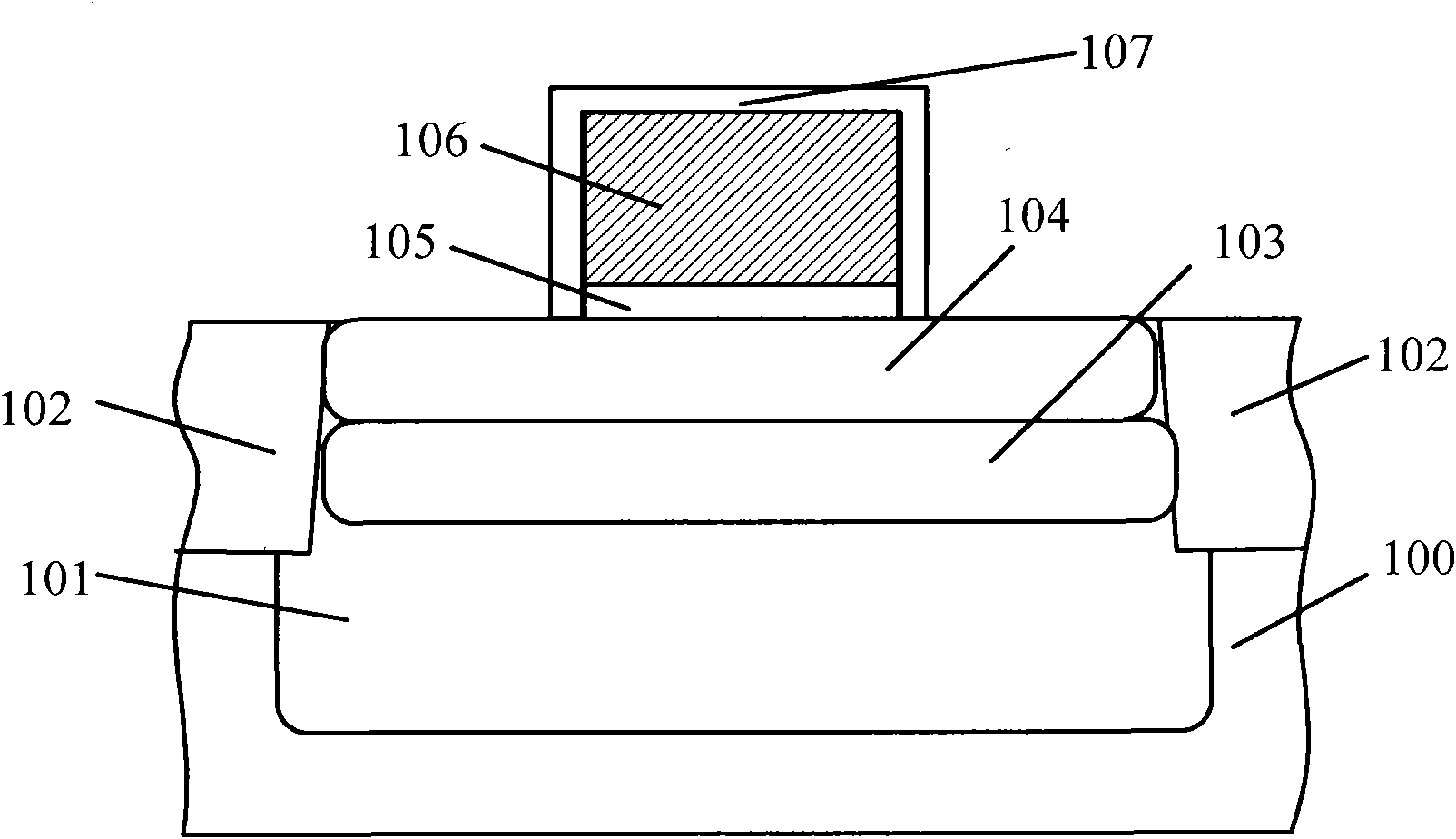

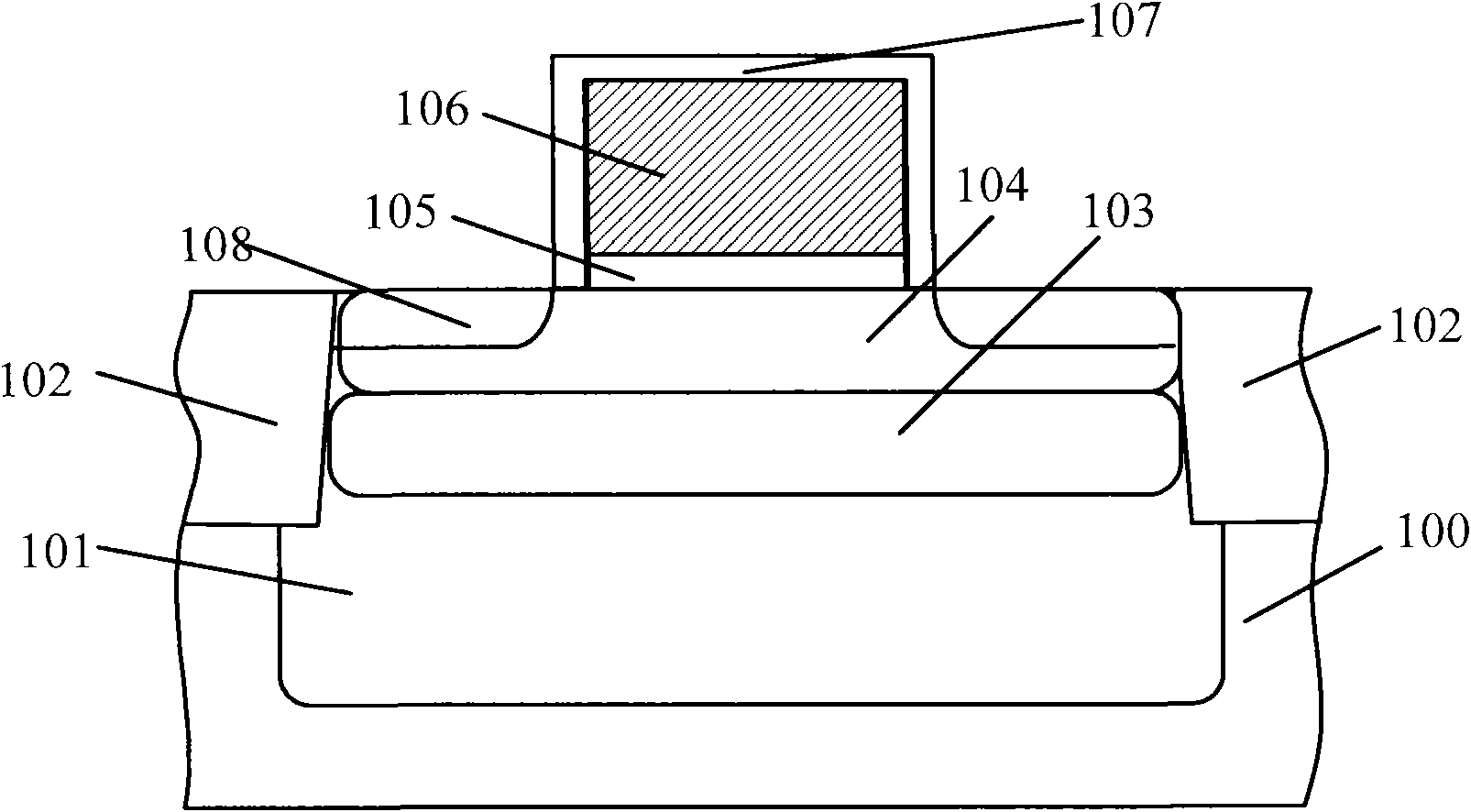

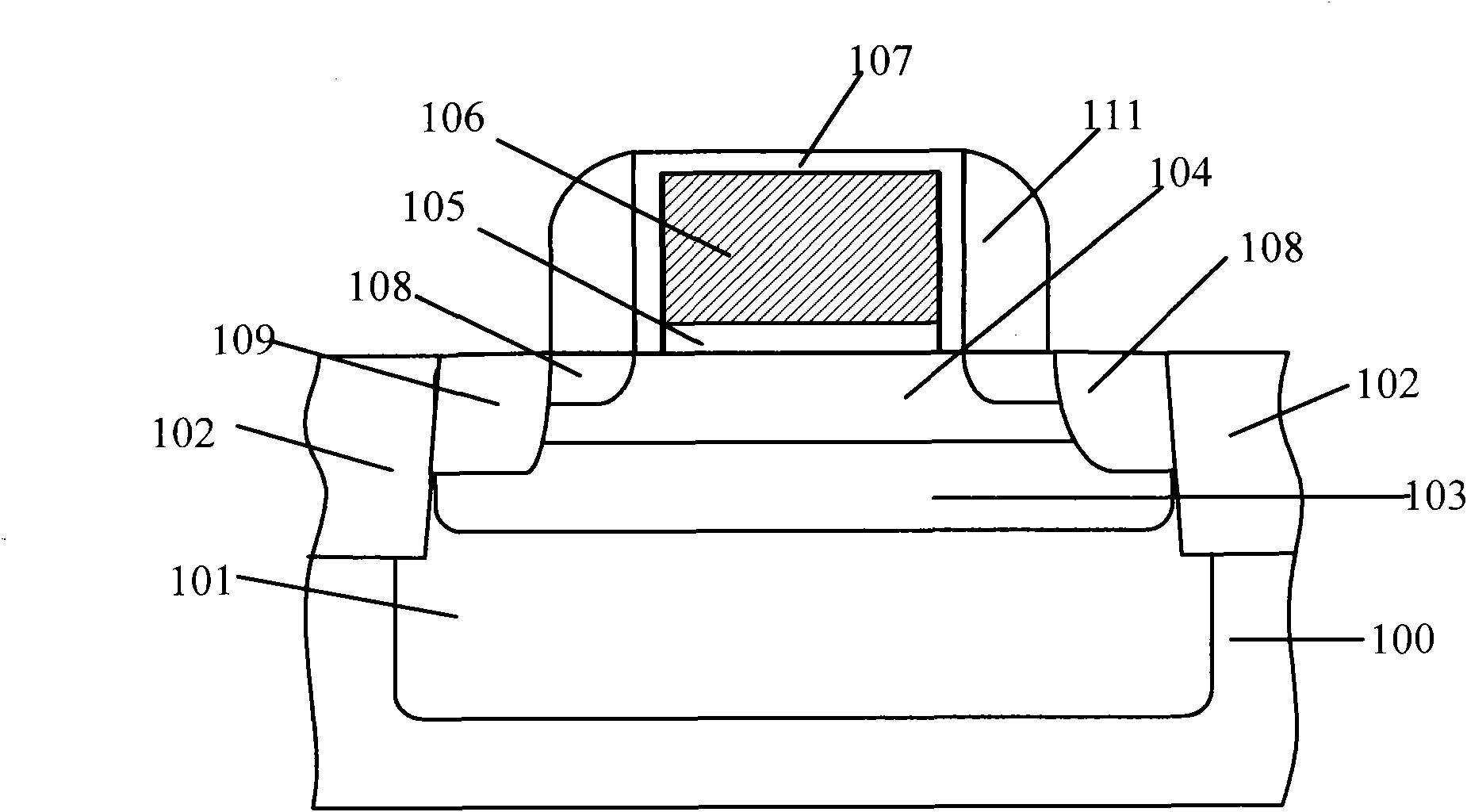

[0040] The inventors found that, in order to reduce the size of the device and suppress the short channel effect of the device, the prior art utilizes an ultra-shallow junction process to fabricate the source / drain regions of the MOS transistor. Since the depth of the source / drain region is reduced, the depth of the threshold voltage injection region in the prior art should also be correspondingly reduced. However, the depth of the threshold voltage implantation region is reduced, so that the activation rate of the dosage of the threshold voltage implantation is reduced, and the effect of the threshold voltage implantation on the threshold voltage adjustment of the transistor becomes worse. In order to obtain the same adjustment effect, the prior art increases the dose of threshold voltage implantation, but because the element of threshold voltage implantation is usually boron (for NMOS transistors) or phosphorus (for PMOS transistors), large doses of boron and phosphorus are p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com