A method for increasing back gate threshold voltage of soi-pmos device

A threshold voltage, back-gate technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of increasing process complexity, device damage, and increasing costs, and achieve back-gate threshold voltage and improve threshold voltage. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The technical solution of the present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

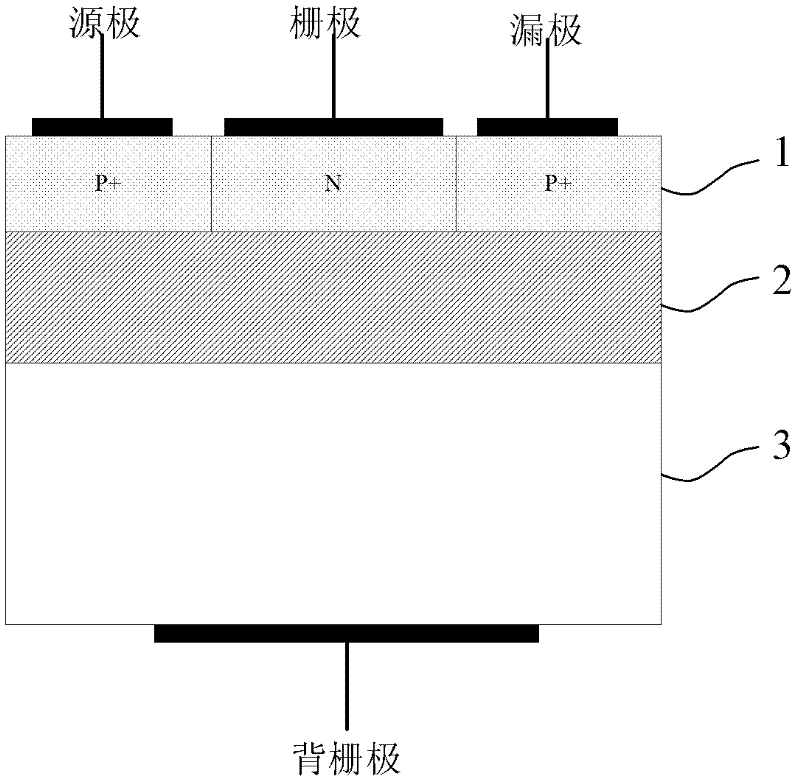

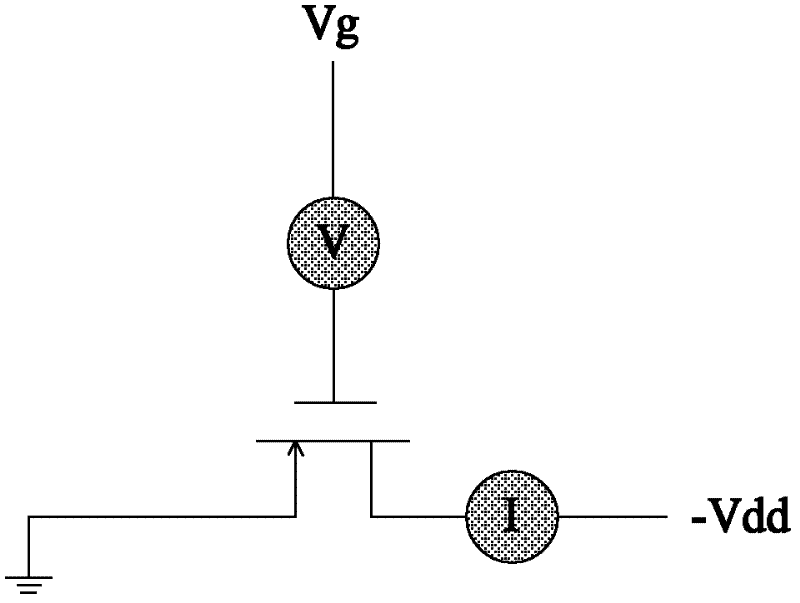

[0019] Such as figure 1 as shown, figure 1 It is an SOI-PMOS device that can be used in the present invention. The SOI silicon wafer comprises a top silicon film (1), an insulating oxide layer (2) and a silicon substrate (3), and an SOI-PMOS device is prepared on the top silicon film (1). The SOI material is a commercial conventional oxygen ion implantation isolation (SIMOX) sheet, and other thermal bonding and smart-cut (Smart-Cut) sheets can also be used. For a normal working SOI-PMOS device, the gate and drain are connected to the power supply potential (Vdd), and the source and back gate are connected to the ground potential (Vss).

[0020] Bulk silicon PMOS devices in the prior art generally have only three terminals, namely: gate, source and drain, and only focus on the threshold voltage of the gate. The general met...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com