Platform system for realizing circuit verification of Nandflash flash memory controller based on FPGA (Field Programmable Gate Array) and method thereof

A flash memory controller and controller technology, applied in static memory, instruments, etc., can solve the problems of low test efficiency, increased research and development costs, and inability to verify the logical function of Nandflash controller circuits, etc., to achieve stable and reliable work performance and a high degree of automation , the effect of shortening the R & D cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] In order to understand the technical content of the present invention more clearly, the following examples are given in detail.

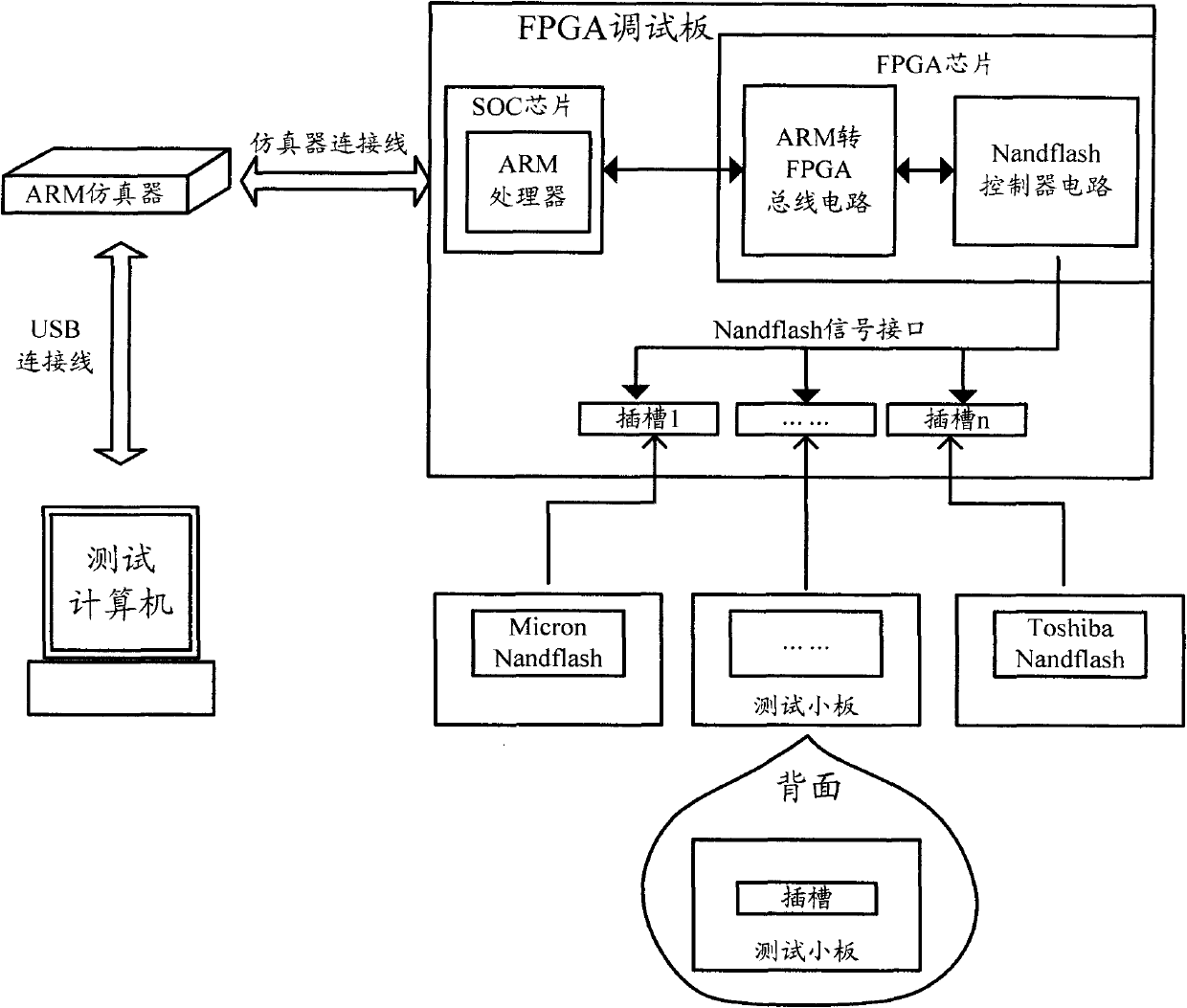

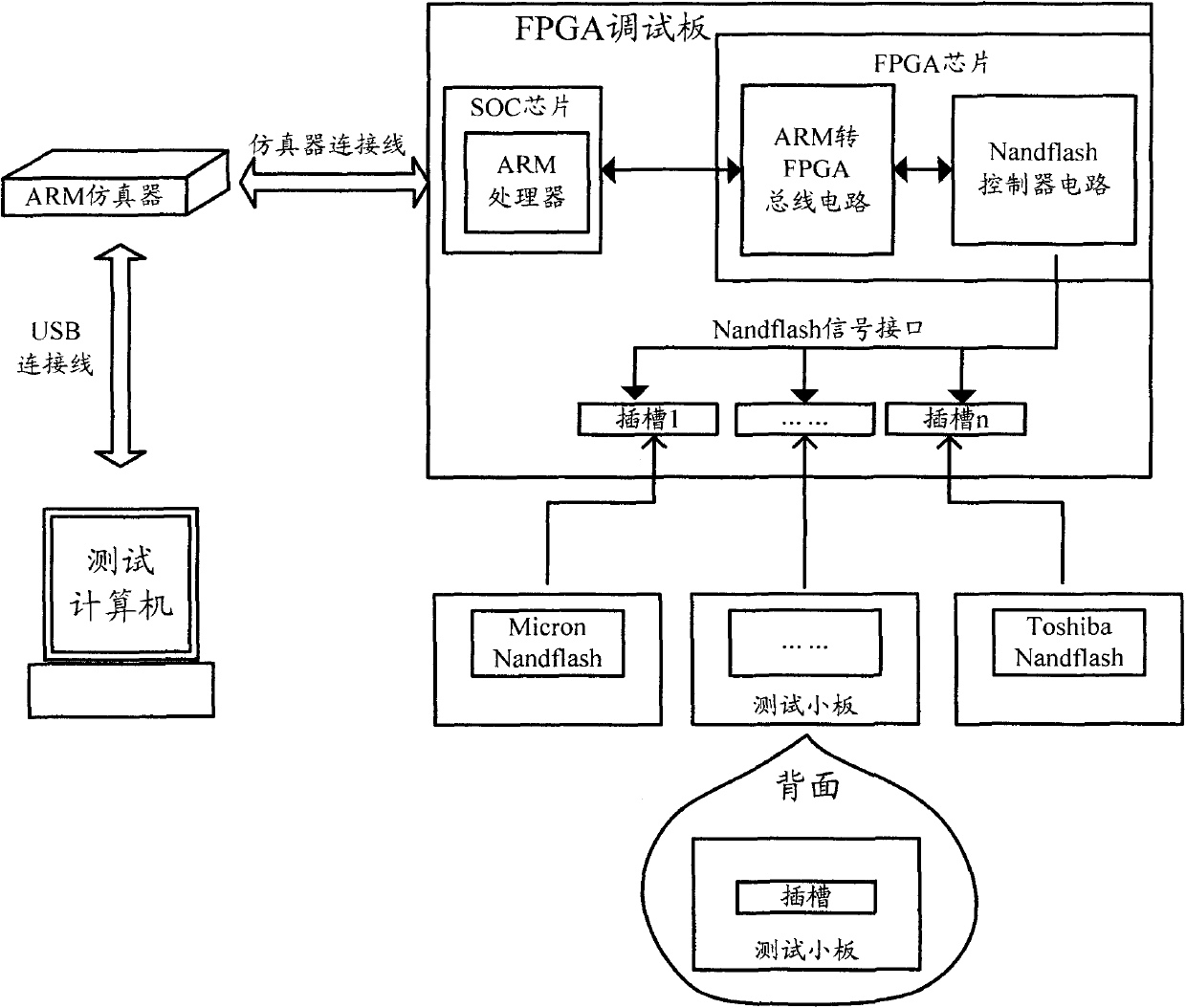

[0051] see figure 1 Shown, this platform system that realizes Nandflash flash memory controller circuit verification based on FPGA includes test computer and the test board that carries Nandflash flash memory chip, wherein, also includes test emulator and FPGA debugging board in the described platform system, described SOC chip, FPGA chip and several Nandflash signal interface modules are carried on the FPGA debugging board, bus conversion circuit module and Nandflash controller circuit module are arranged in the described FPGA chip, and described test computer passes through described test successively The emulator, the SOC chip, the bus conversion circuit module and the Nandflash controller circuit module are respectively connected with each of the Nandflash signal interface modules, and each Nandflash signal interface module is connected ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com