High-voltage LDMOS (landscape diffusion metal oxide semiconductor) device

A device and high-voltage technology, which is applied in the field of semiconductor high-voltage and low-resistance devices, can solve the problems of reduced reverse withstand voltage of LDMOS devices and the concentration cannot be made too high, and achieves the effect of improving reverse withstand voltage and reducing forward on-resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

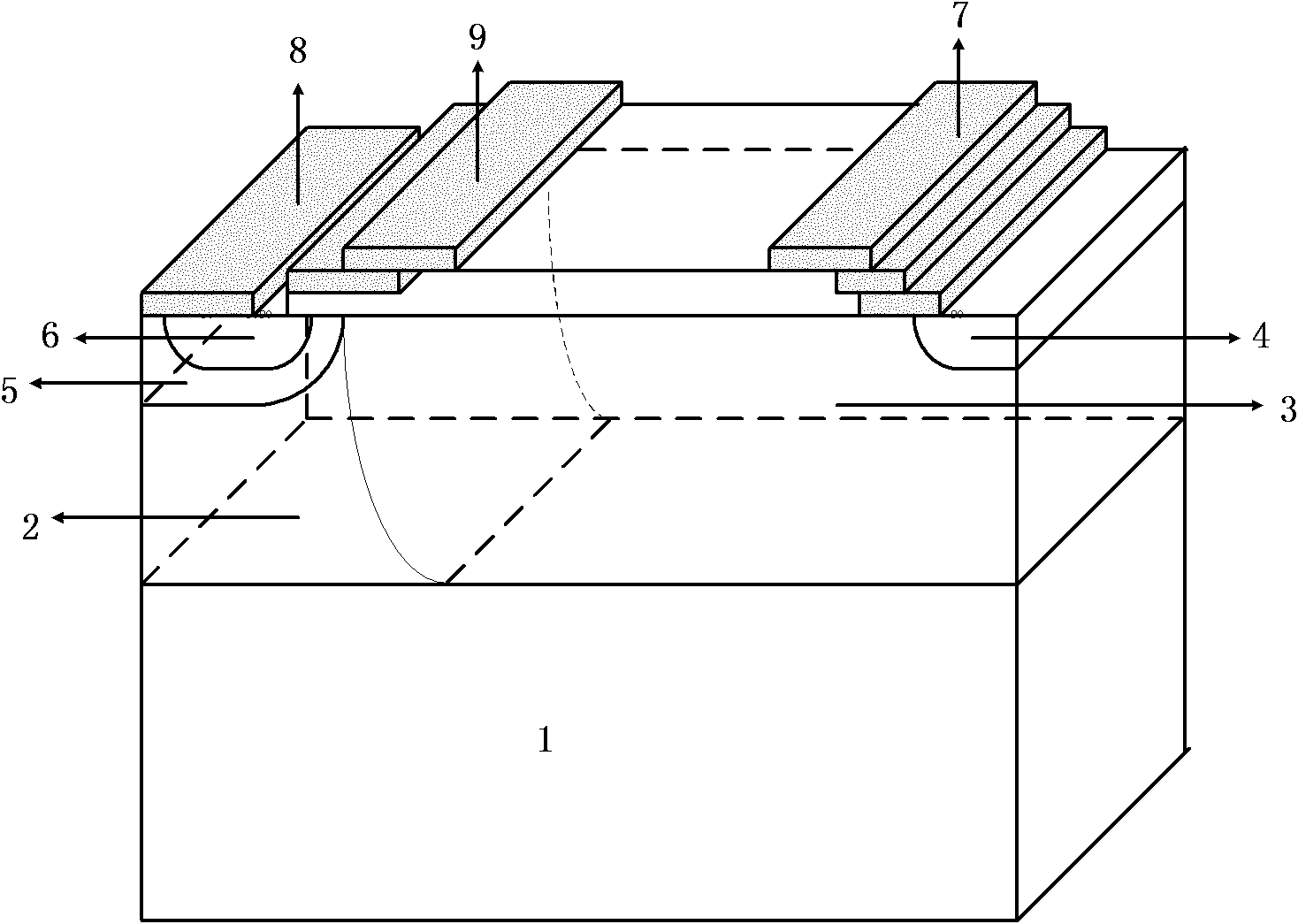

[0022] Embodiment one: if Figure 4 As shown, the LDMOS device includes a substrate 1, an epitaxial layer 2, a drift region 3, a drain region 4, a source region 6, a drain 7, a source 8, and a gate 9. In this embodiment, the LDMOS device is a P epitaxial N-channel LDMOS device, so the substrate 1 and the epitaxial layer 2 are p-type, and the drift region 3 is n - type, the drain region 4 and the source region 6 are n + type, the epitaxial layer 2 is located on the substrate 1, the drift region 3 is located on the side of the epitaxial layer 2 close to the drain region 4 and the lower surface spans the lower surface of the epitaxial layer 2, the drain region 4 and the source region 6 are located at both ends of the LDMOS device, There are two pairs of n-type semiconductor regions 10 and p-type semiconductor regions 11 alternately arranged across the lower surface of the epitaxial layer 2 on the interface between the substrate 1 and the epitaxial layer 2, the n-type semiconduct...

Embodiment 2

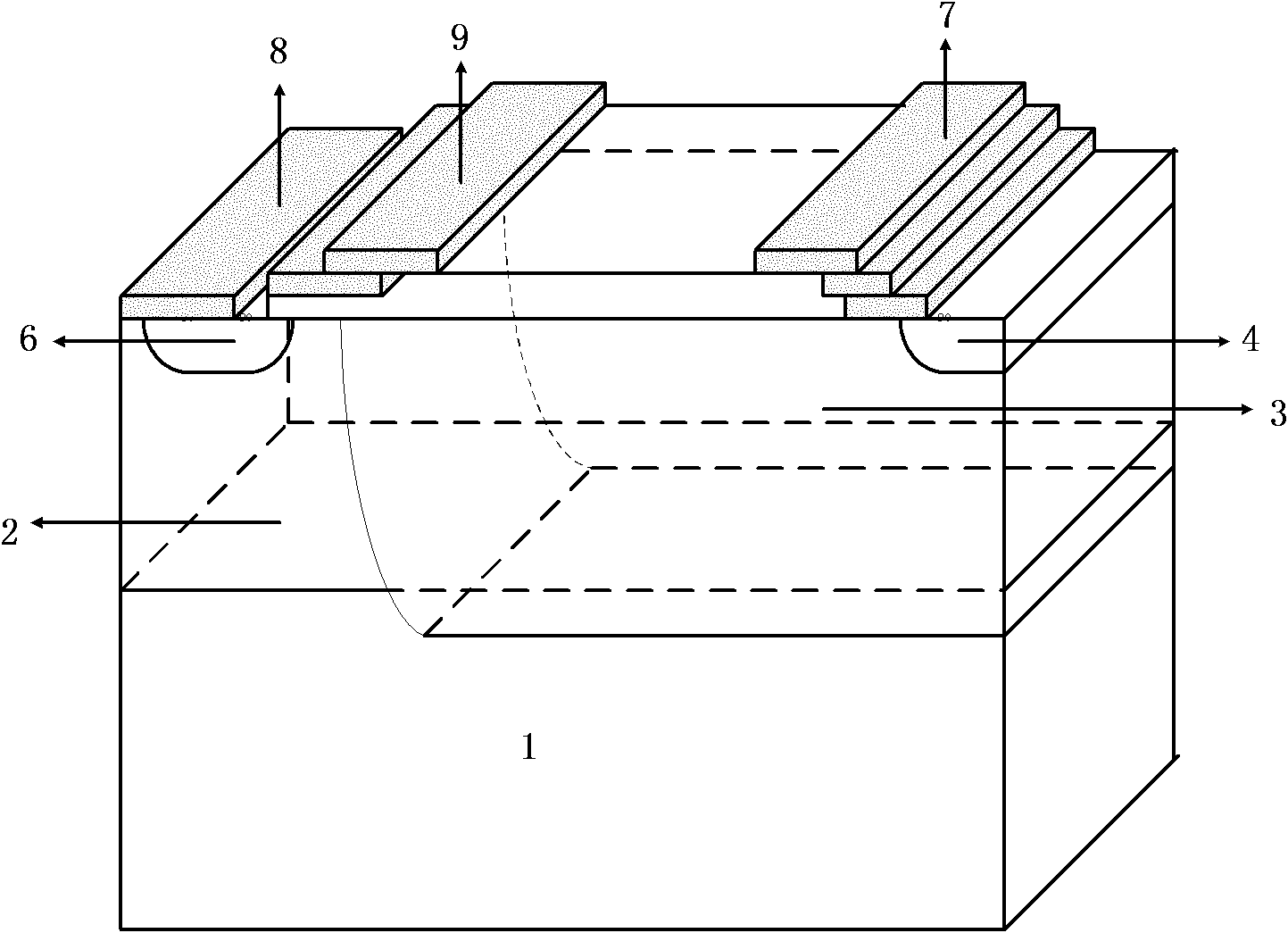

[0027] Embodiment two: if Figure 5 As shown, on the basis of Embodiment 1, in order to prevent the PN junction formed by the n-type semiconductor region 10 and the p-type semiconductor region 11 from affecting the electric field of the drain region 4, the length of the n-type semiconductor region 10 and the p-type semiconductor region 11 can be shortened To the interface between the drain region 4 toward the center and the drift region 3 .

Embodiment 3

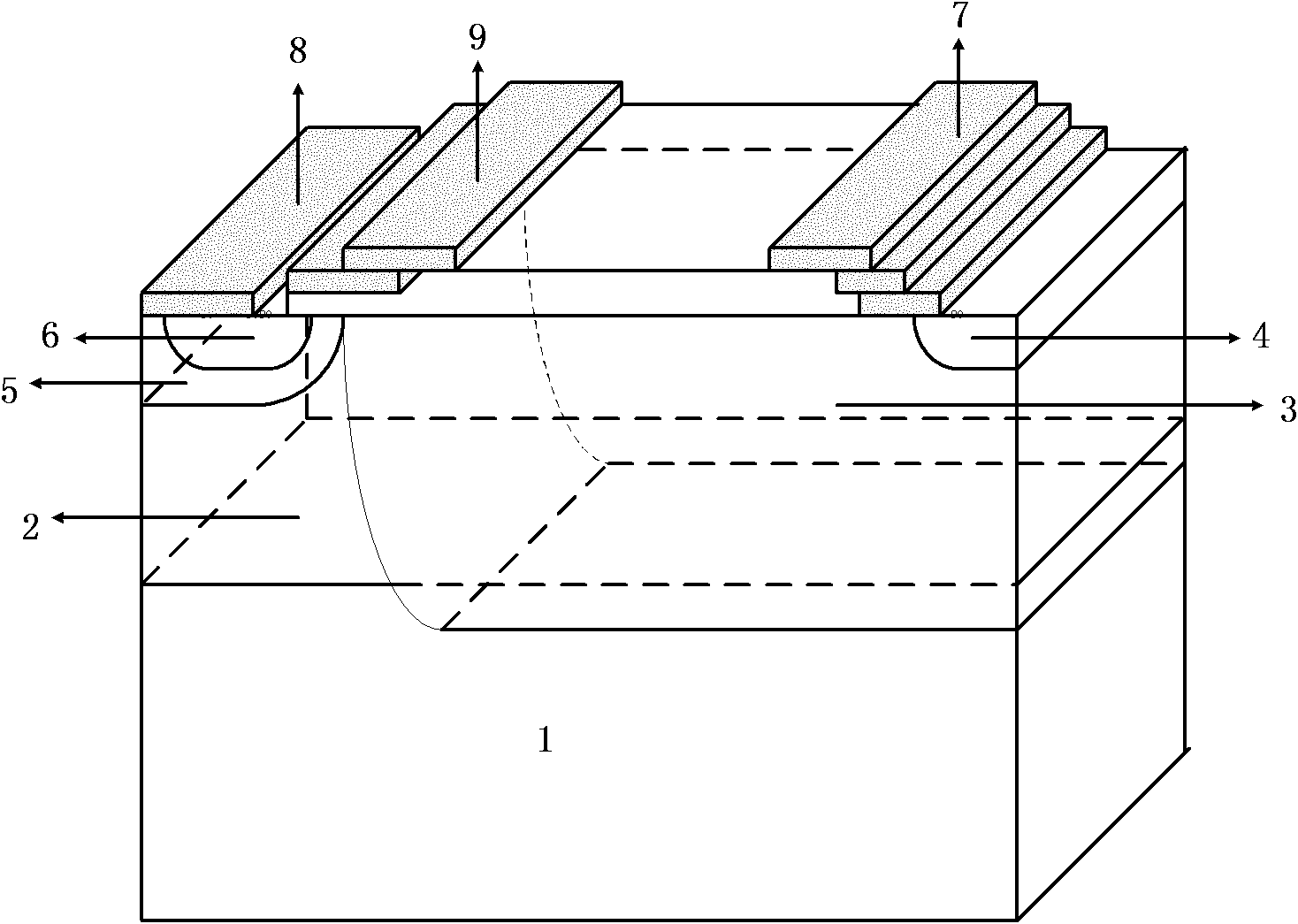

[0028] Embodiment three: as Figure 6 As shown, on the basis of Embodiment 1 or Embodiment 2, in order to prevent the n-type semiconductor region 10 and the p-type semiconductor region 11 from affecting the source region 6, the lengths of the n-type semiconductor region 10 and the p-type semiconductor region 11 can be adjusted to The shortening is not connected to the interface between the drift region 3 facing the source region 6 and the epitaxial layer 2 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com