LDMOS device and manufacturing method thereof

A technology of devices and drift regions, applied in the field of laterally diffused metal oxide semiconductor devices and their preparation, to achieve the effects of reducing forward conduction resistance, improving and reducing depth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0079] The technical solution of the LDMOS device of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0080] In this embodiment, the direction from the source to the drain or from the drain to the source is defined as the width direction, and the direction from the upper surface of the substrate to the lower surface or from the lower surface of the substrate to the upper surface is defined as the depth direction.

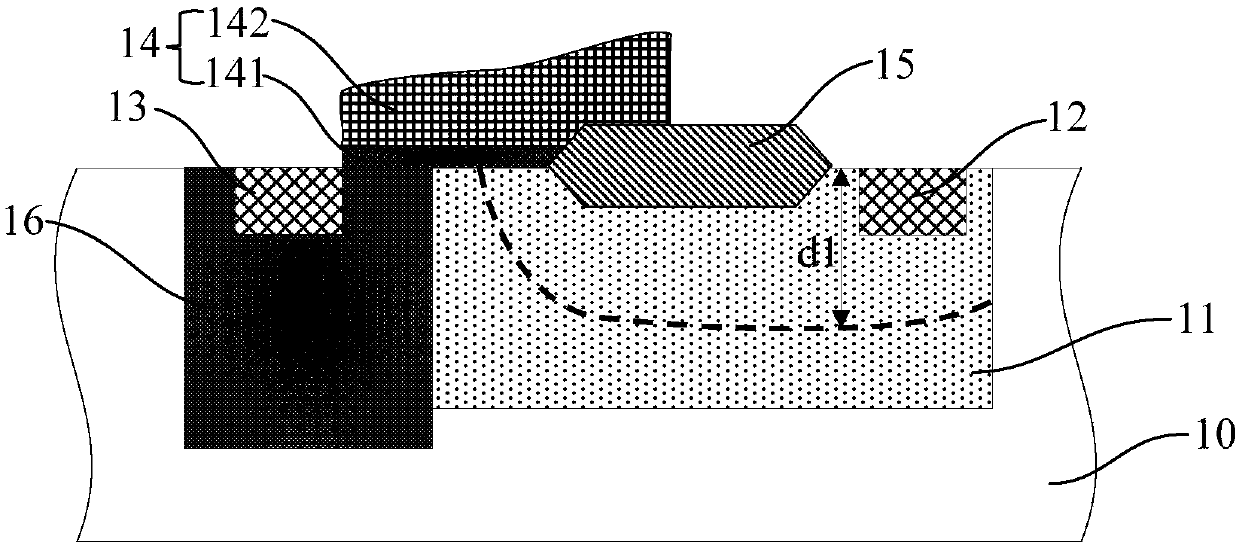

[0081] Such as figure 2 As shown, a schematic cross-sectional structure diagram of the LDMOS device of this embodiment is shown. Please note that in this embodiment, the N-type LDMOS device is used as an example for illustration, but those skilled in the art can understand that the present invention is also fully applicable to the P-type LDMOS device, only the conductivity type of each doped region Just reverse it.

[0082] Please refer to figure 2 , this embodiment provides an LDMOS device, the LDMOS devi...

Embodiment 2

[0107] The technical solution of the manufacturing method of the LDMOS device of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0108] As described in Example 1, in this embodiment, the preparation method of an N-type LDMOS device is used as an example for illustration, but those skilled in the art can understand that the present invention is also fully applicable to the preparation method of a P-type LDMOS device. It is only necessary to invert the conductivity type of each doped region.

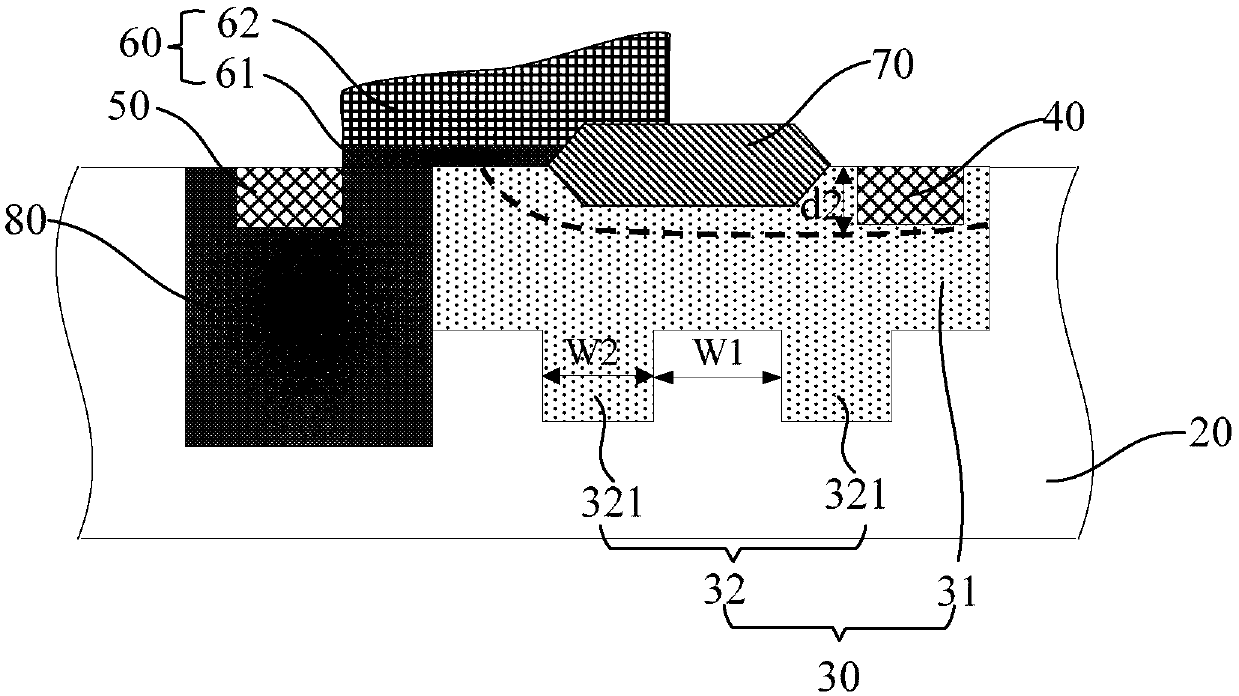

[0109] see Figure 4 and Figure 5 , first proceed to step S1), providing a P-type substrate 20.

[0110] see Figure 4 and Figure 7b , followed by step S2), forming an N-type drift region 30 in the P-type substrate 20, and the N-type drift region 30 includes a first drift region 31 and a second drift region located on the lower surface of the first drift region 31. A drift region 32, wherein the width of the second drift regio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com