Method for manufacturing gate oxide

A technology of gate oxide layer and fabrication method, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problems of product reliability, increase in surface roughness of semiconductor substrates, etc., to ensure device performance and process. simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

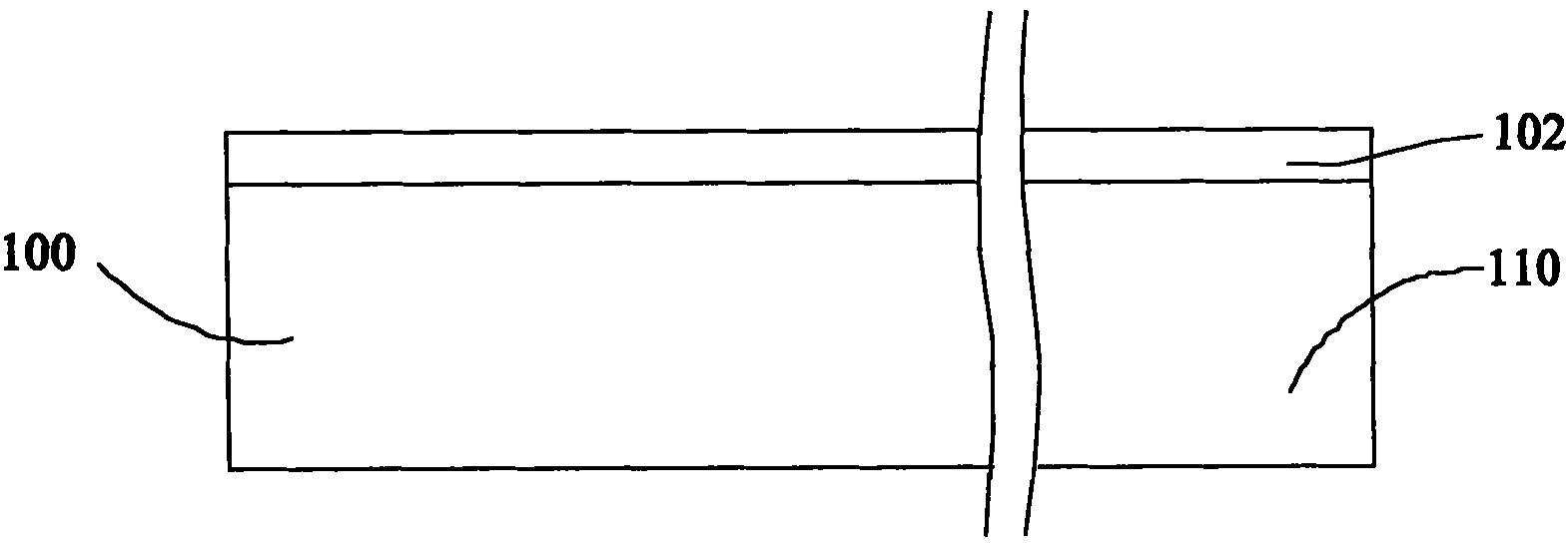

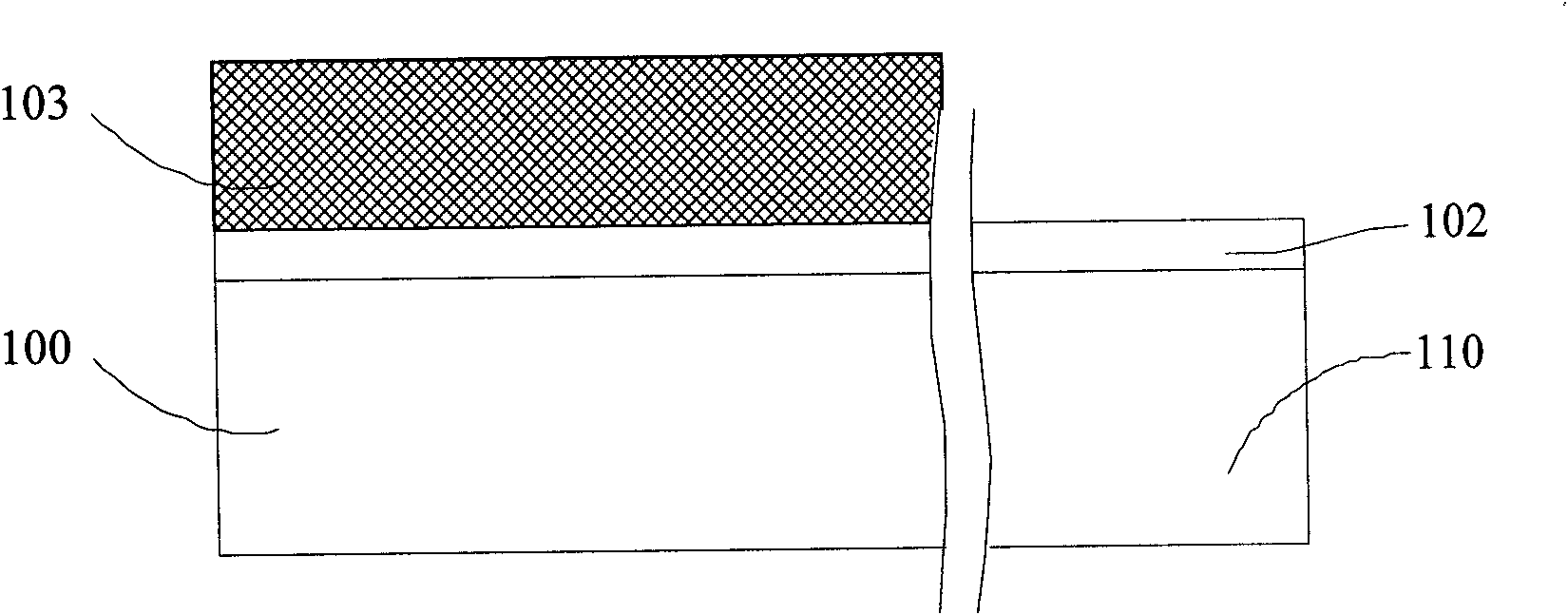

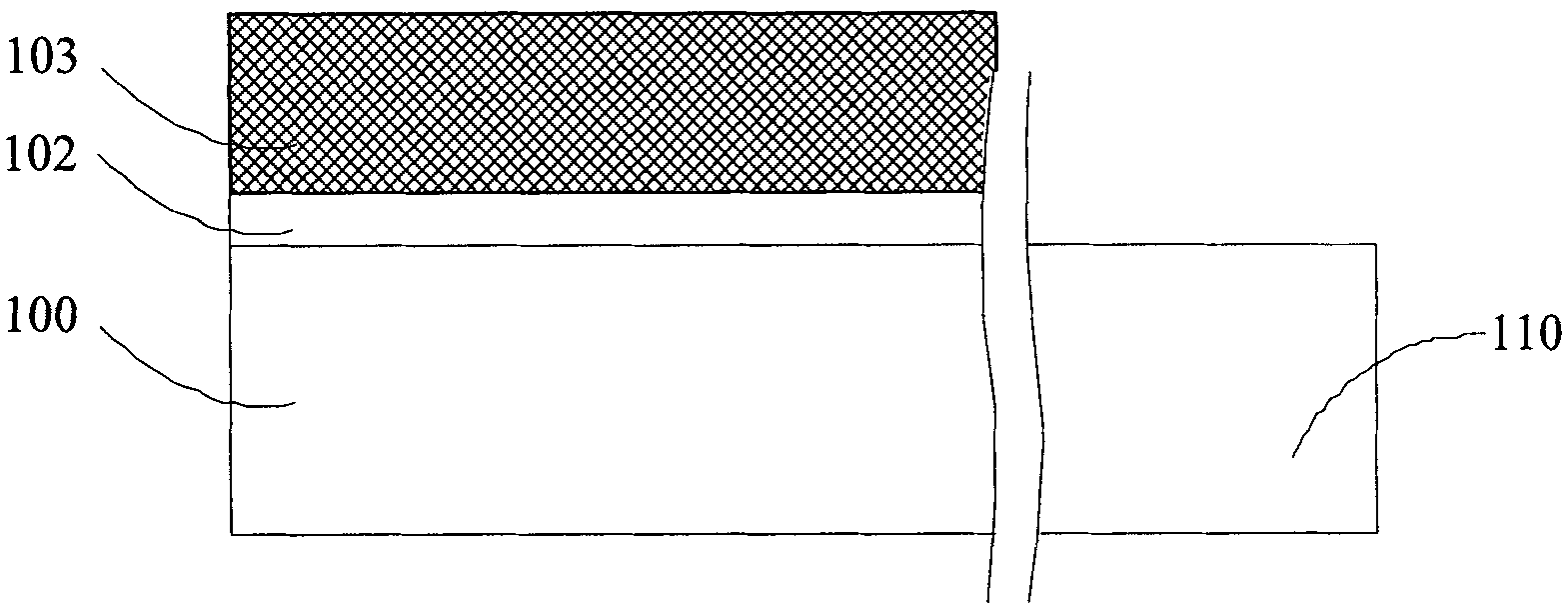

[0016] A method for controlling the thickness of a gate oxide layer in a logic region according to the present invention, as shown in FIG. 16 , includes: step S101, providing a semiconductor substrate including a first region and a second region, and forming a ratio of A first gate oxide layer with a predetermined thickness of 10 angstroms to 100 angstroms; step S102, forming a photoresist layer on the first gate oxide layer in the first region, using the photoresist layer as a mask, and using a pH value at 2 to 8 wet etching reagents to remove part of the first gate oxide layer on the semiconductor substrate in the second region, and the remaining first gate oxide layer in the second region after etching has a thickness in the range of 10 to 20 angstroms; step S103 , removing the photoresist layer; step S104, using a wet etchant with a pH value of 2 to 6, to remove the remaining first gate oxide layer in the second region; step S105, forming a first gate oxide layer on the fir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com