Method for making shallow groove insolation structure

A technology of isolation structure and shallow trench, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of unfavorable electrical properties of devices, poor trench shape, and uneven trench sidewalls, etc., to improve leakage The effect of current and other electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

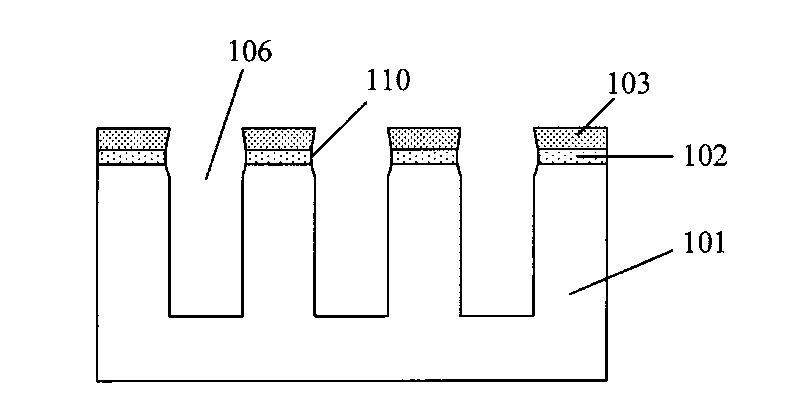

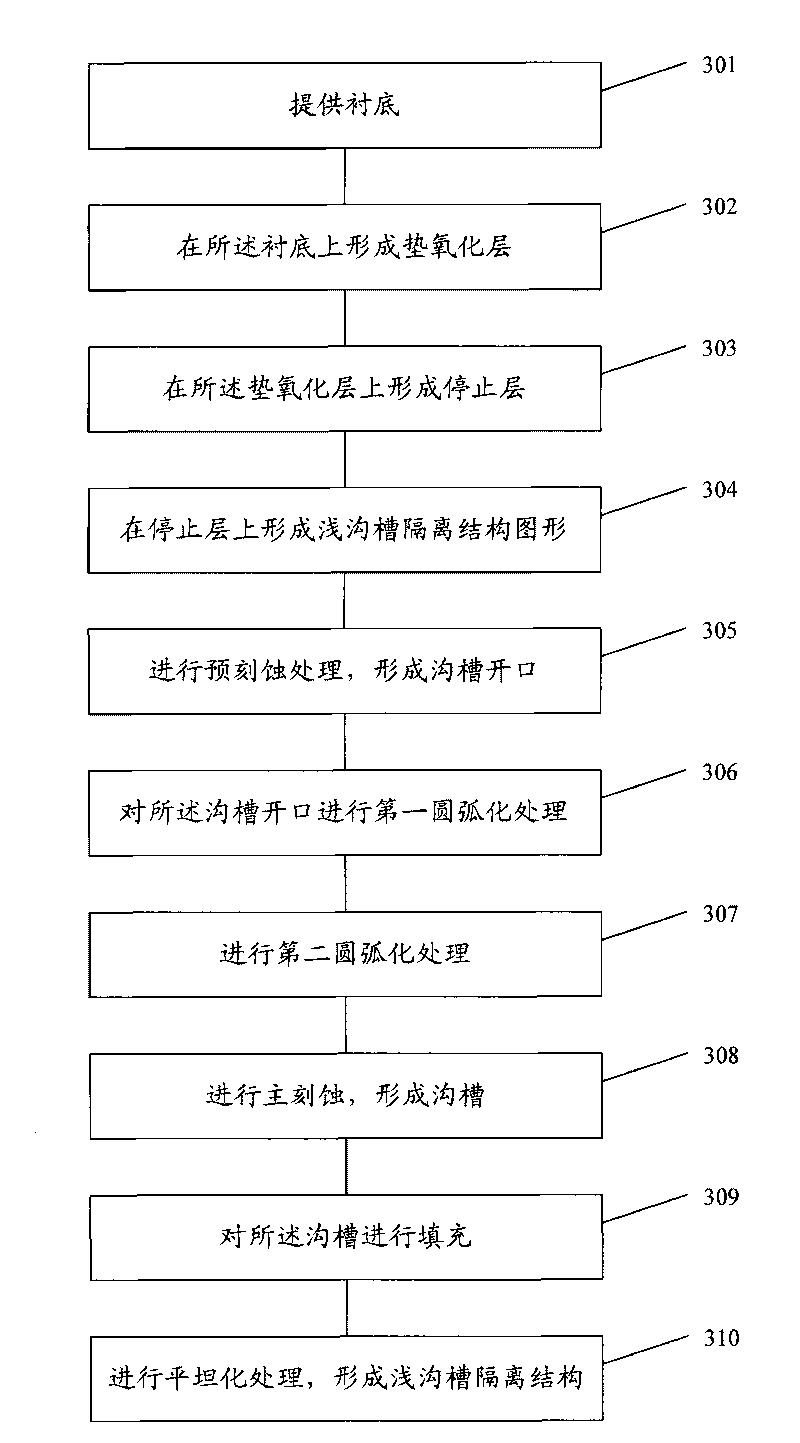

[0034] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0035] The processing method of the present invention can be widely used in various fields, and can utilize many suitable materials to make, and the following is to illustrate by specific embodiment, certainly the present invention is not limited to this specific embodiment, in this field Common replacements known to those of ordinary skill undoubtedly fall within the protection scope of the present invention.

[0036] Secondly, the present invention is described in detail using schematic diagrams. When describing the embodiments of the present invention in detail, for the convenience of explanation, the cross-sectional view showing the device structure will not be partially enlarged according to the general scale, which should not be u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com