Room temperature ultrasonic soldering method for area array encapsulated electronic components

An electronic component, ultrasonic technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of residual stress solder joints of welding structures, metallization layers that are easy to inductively heat the surrounding, thermal shock of heat-sensitive materials, etc. Improve reliability and electrical performance, inhibit nucleation and grain growth, eliminate the effects of thermal stress formation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

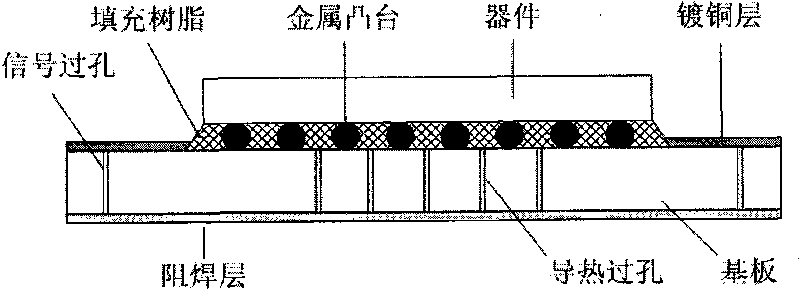

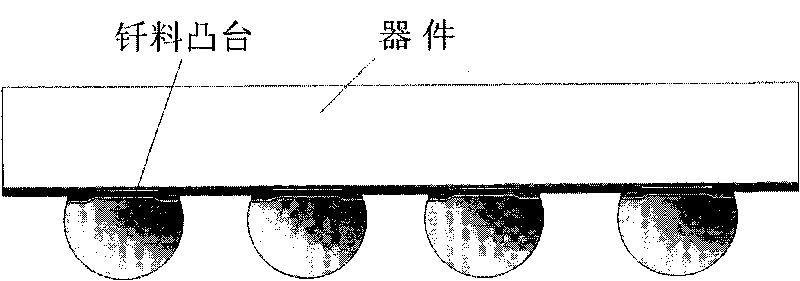

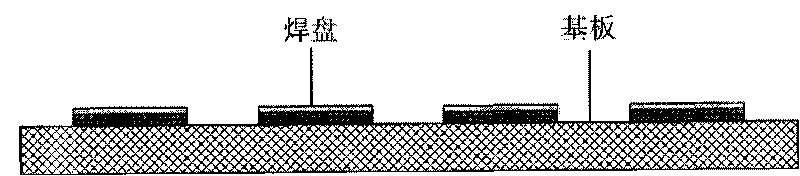

[0027] Embodiment 1: prepare 4×4BGA packaged devices, the diameter of the boss is φ10μm~φ500μm, and the pitch is 10μm~500μm; prepare 4×4BGA corresponding pads, the pad materials are Au / Ni / Cu, and their thicknesses are (10nm~5μm) / (1μm~5μm) / (10μm~100μm); align the interconnection pads of the electronic devices with solder bosses with the pads on the printed circuit board for placement; use a cutting frequency with a fixed frequency of 20~100kHz Weld to a vibration ultrasonic welder. After setting the welding pressure (0.1-6.5bar), welding time (0.1-6s), and input energy (10-900ws), start the ultrasonic welding machine, and the upper sonotrode is pressed tightly on the lower sonotrode under the bonding pressure F driven by the cylinder. On the surface of the upper weldment, the ultrasonic wave is triggered to connect the solder boss and the pad material of the printed circuit board, and finally the upper acoustic pole is retracted, and the process is completed.

Embodiment approach 2

[0028] Embodiment 2: In the second step of Embodiment 1, the Au / Ni / Cu pad is changed to Sn / Cu pad, and its size is (1 μm-10 μm) / (10 μm-100 μm), and the rest of the steps are the same as Embodiment 1 ;

Embodiment approach 3

[0029] Embodiment 3: In the second step of Embodiment 1, the Au / Ni / Cu pad is changed to a Sn-based intermetallic compound layer / Cu pad, and its size is (0.1 μm-10 μm) / (10 μm-100 μm), and the rest The steps are the same as method 1;

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com