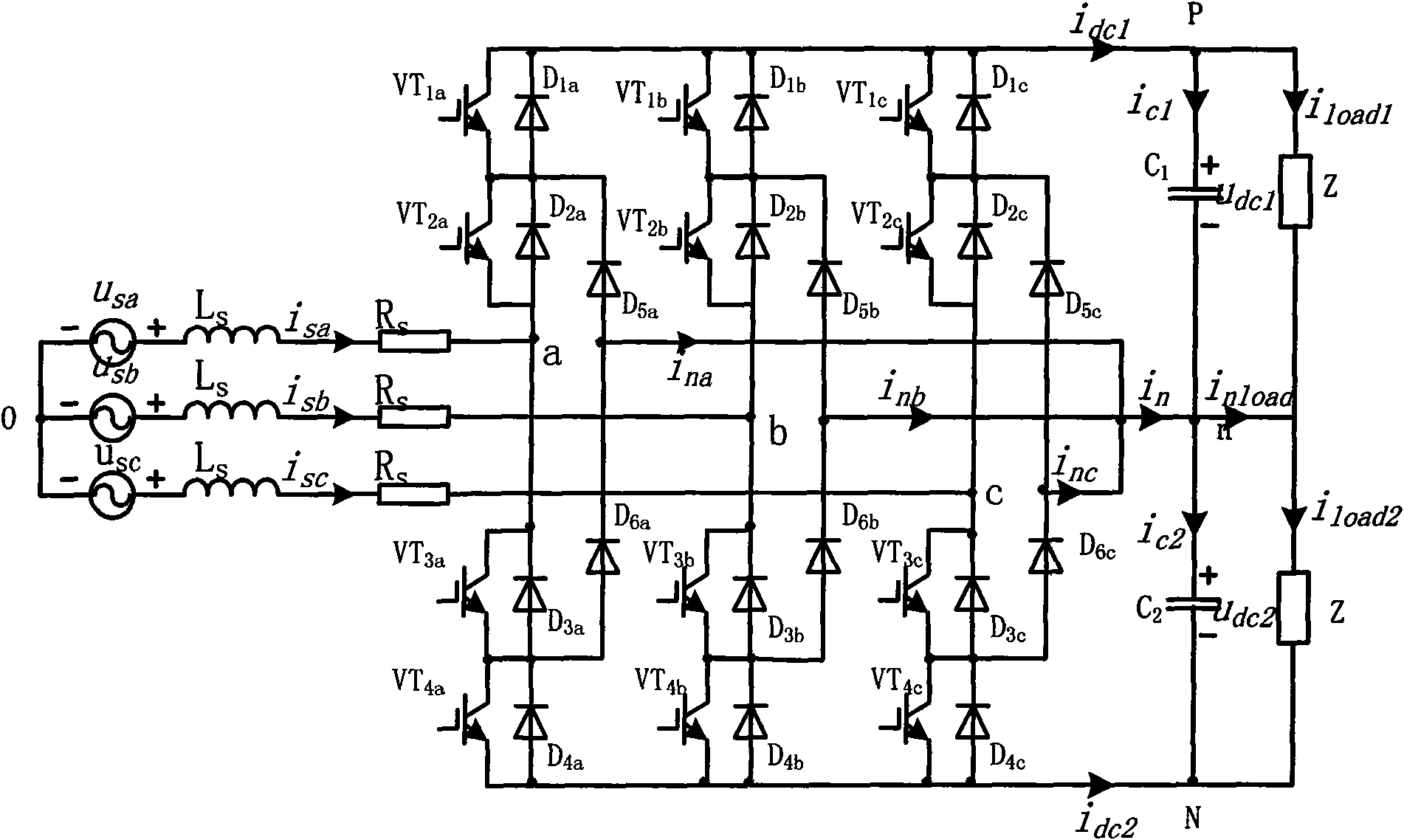

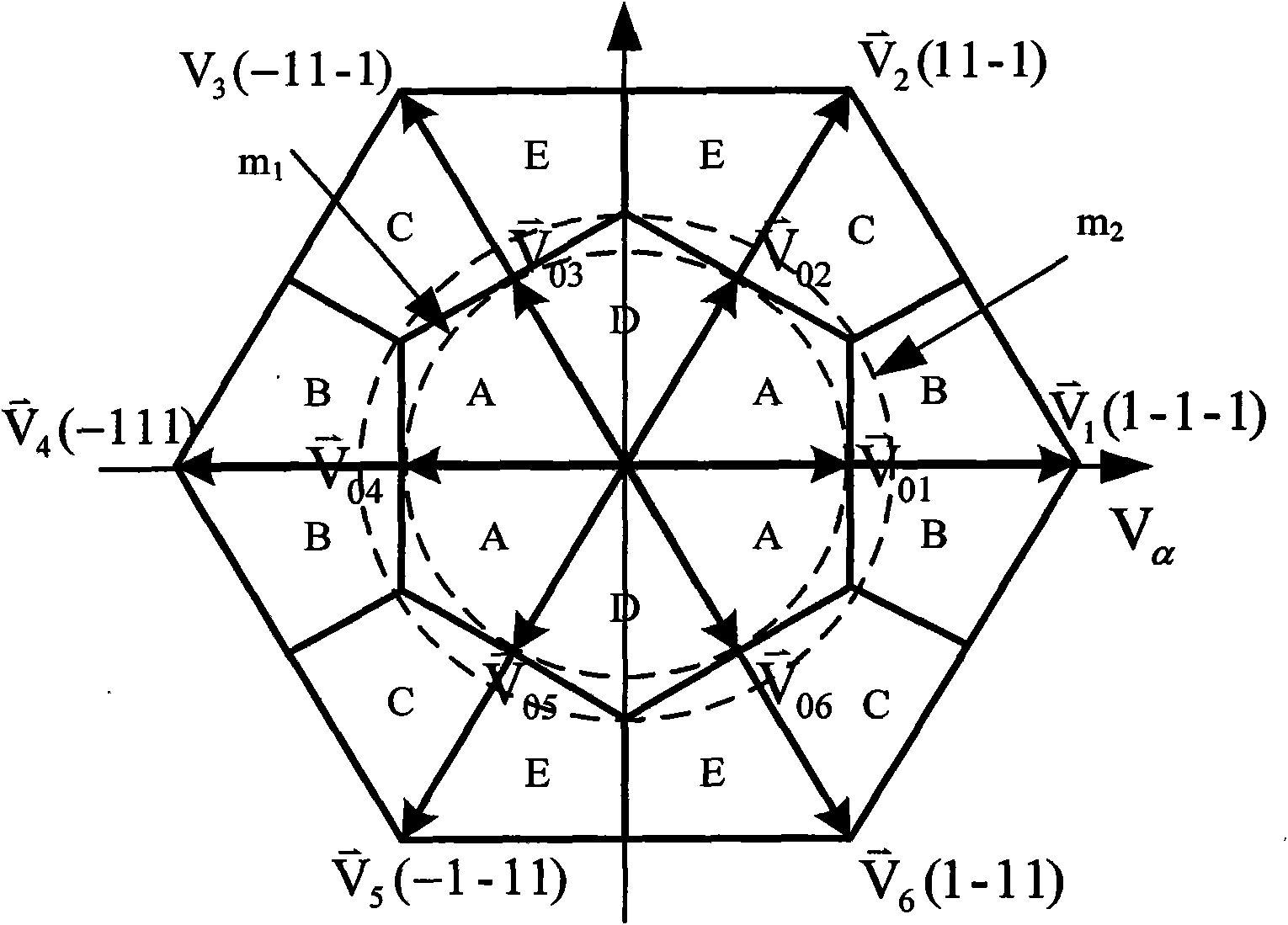

Symmetrical three-section voltage vector pulse width modulation method for three-level PWM rectifier

A voltage vector, pulse width modulation technology, applied in electrical components, output power conversion devices, AC power input into DC power output and other directions, can solve the problem of DC side midpoint potential imbalance and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0127] Embodiment: DSP adopts TMS320×LF2407A of TI Company. CPLD adopts the MAXII EPM1270 144C5N chip of ALTERA Company, which has 1270 logic units and 144 pins, including 116 I / O ports, clock frequency is 10MHz, and gate-level delay is less than 10ns, which can meet the requirements of three-level PWM rectifier system real-time requirements. The simulation software adopts Quartus II of ALTERA Company, and the hardware description language is Verilog HDL, which automatically generates modules and evaluation reports.

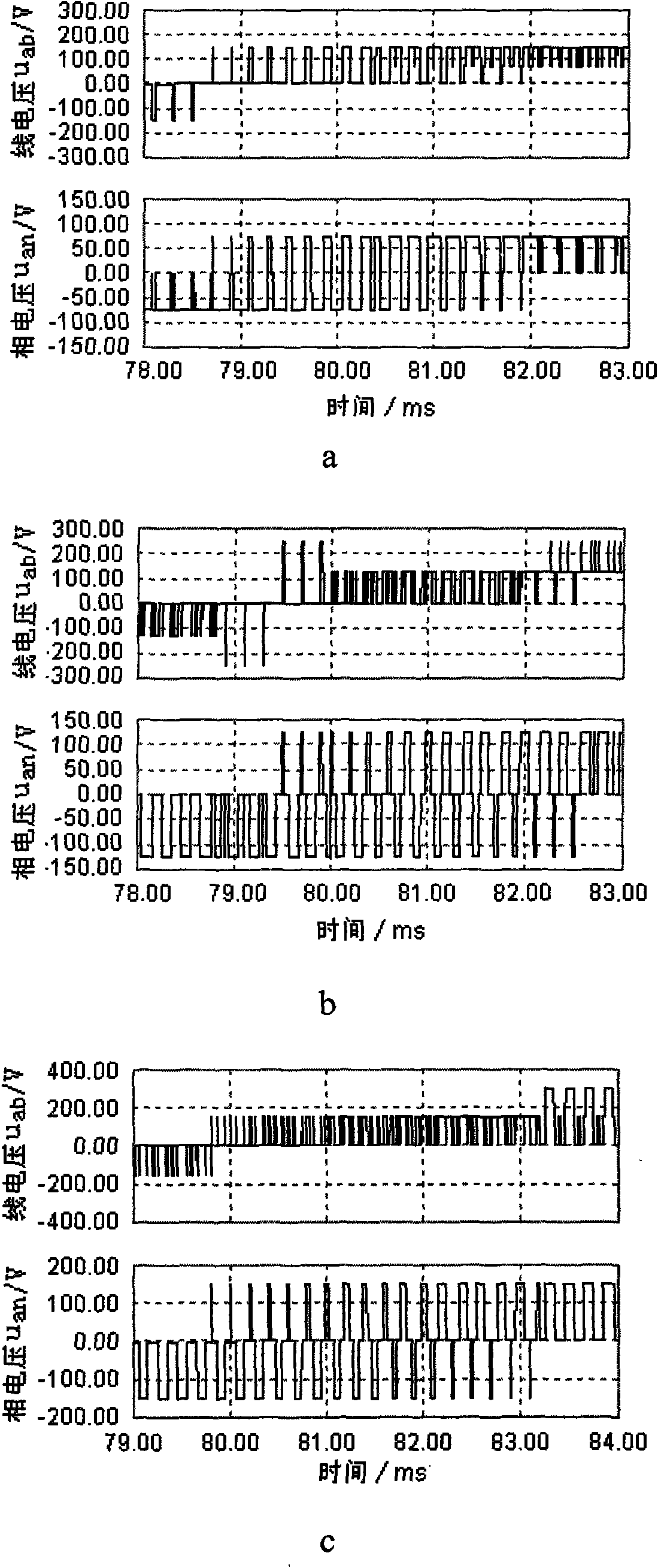

[0128] Rectifier parameters: grid phase voltage U 2 =30V, frequency f=50Hz; series reactance L s =10mH; DC output filter capacitor C 1 =C 2 =2000μF, load R=62Ω, inductance L=55mH, DC side given voltage U dc =110V, switching frequency f=2kHz.

[0129] Figure 10 a. Figure 10 b. Figure 10 c are the waveform diagrams under the symmetrical three-zone voltage vector pulse width modulation method, where Figure 10 a is the supply voltage u of the three-le...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com