Making method for silicon germanium extension layer

A technology of silicon germanium epitaxy and manufacturing method, applied in semiconductor/solid-state device manufacturing, coating, metal material coating process and other directions, can solve the problems of pattern loading effect, low yield, small margin of silicon germanium epitaxial layer, etc. Fast growth, low impact, high yield effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

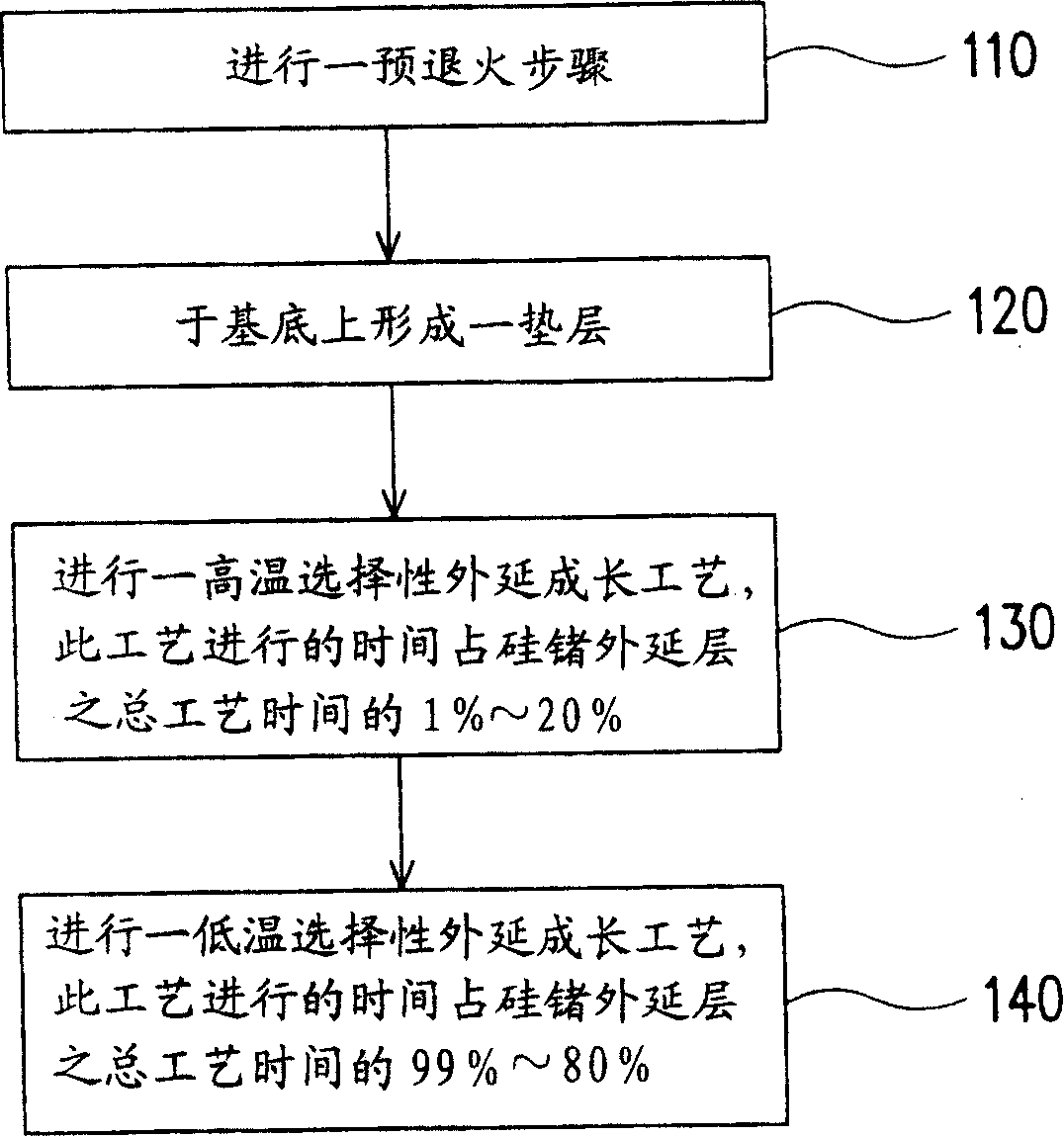

[0047] figure 1 It is a flow chart of manufacturing a silicon germanium epitaxial layer according to an embodiment of the present invention.

[0048] Please refer to figure 1 , a pre-annealing (pre-annealing) step 110 is performed first, and the temperature thereof is, for example, about 800° C. Then, a pad layer is formed on the substrate (step 120). The material of the underlayer is the same as that of the substrate, such as silicon.

[0049] Next, a high-temperature selective epitaxial growth process is performed, and the high-temperature selective epitaxial growth process takes 1% to 20% of the total process time of the SiGe epitaxial layer (step 130 ). In one embodiment, the time for the high temperature selective epitaxial growth process is, for example, 1%-15% of the total process time of the SiGe epitaxial layer, preferably 1%-10%, more preferably 3%-6%. In one embodiment, the high temperature selective epitaxial growth process is performed for about 30 seconds, fo...

no. 2 example

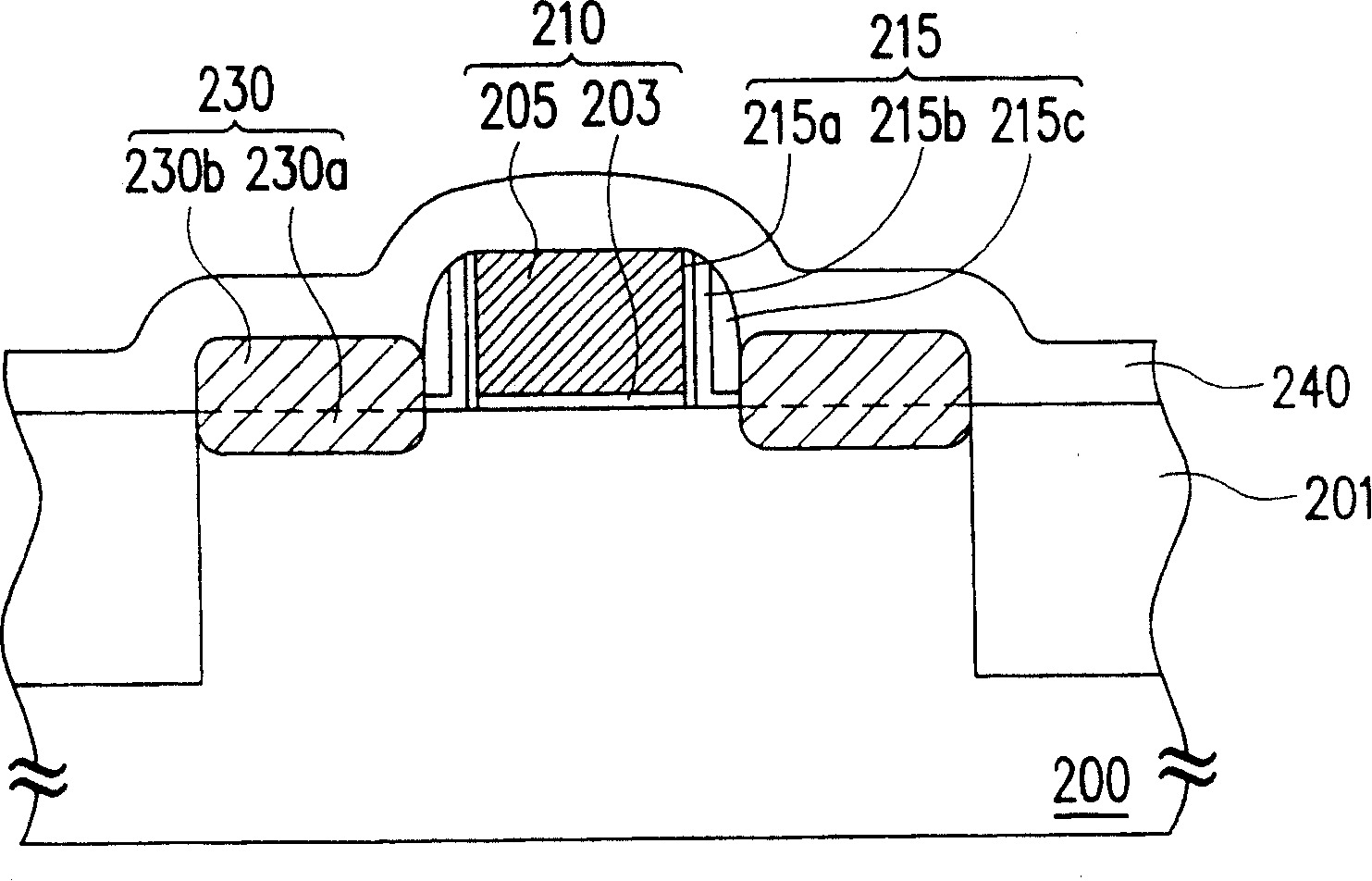

[0062] Figure 2A to Figure 2B It is a sectional view showing a manufacturing process of a silicon germanium epitaxial layer according to another embodiment of the present invention.

[0063] Please refer to Figure 2A Therefore, the method for manufacturing the silicon germanium epitaxial layer proposed by the present invention can be applied to the process of PMOS transistors. An isolation structure 201 is formed in the substrate 200 , and a gate structure 210 is formed on the substrate 200 . Wherein, the substrate 200 is, for example, a silicon substrate, and the isolation structure 201 is, for example, a silicon oxide shallow trench isolation structure. The gate structure 210 includes, for example, a gate dielectric layer 203 and a gate 205 from bottom to top. The material of the gate dielectric layer 203 is, for example, silicon oxide, and the material of the gate 205 is, for example, doped polysilicon, metal, metal silicide or other conductors. The SiGe epitaxial lay...

no. 3 example

[0084] Figure 4 It is a step diagram showing the manufacturing process of a silicon germanium epitaxial layer according to another embodiment of the present invention.

[0085] Please refer to Figure 4 In this embodiment, the silicon germanium epitaxial layer is, for example, formed on a substrate. The substrate is first subjected to a surface treatment step (step 410), such as pre-cleaning or gas diffusion. Then, a pre-annealing step (step 420 ), the temperature of the pre-annealing is, for example, about 800° C. is performed.

[0086] Next, a high-voltage selective process is performed, and the time for the high-voltage selective epitaxial growth process accounts for 1%-20% of the total process time of the SiGe epitaxial layer (step 430 ), preferably for example 8%-17%.

[0087] The pressure of the high-pressure selective epitaxial growth process is, for example, greater than or equal to 10 Torr (torr), and the temperature is, for example, 650°C. The reaction gas used ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com