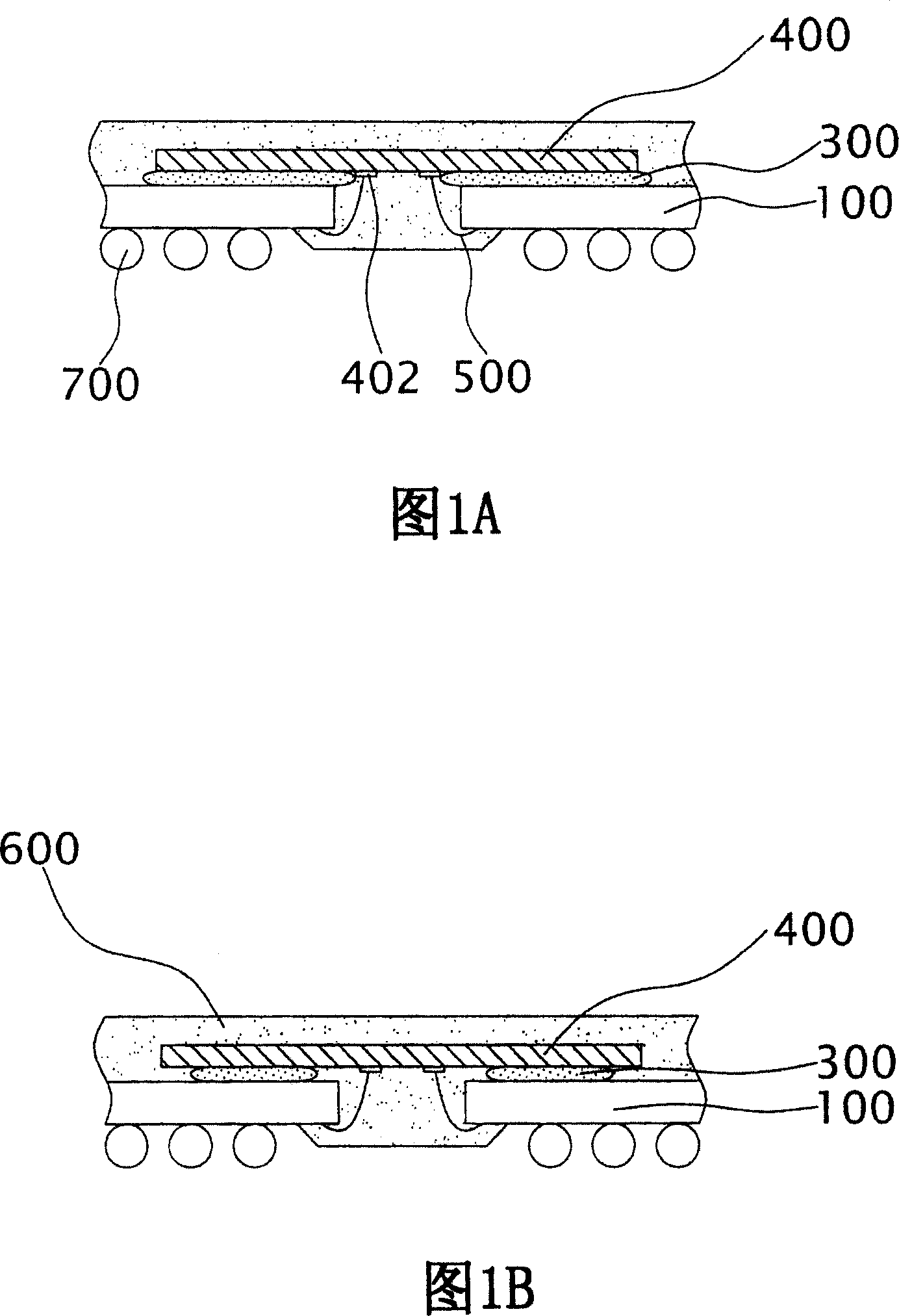

Chip packaging structure and method of producing the same

A technology of chip packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., and can solve problems such as polluting circuits and polluting pads due to overflow of crystal glue

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The detailed description is as follows, and the preferred embodiment is only for illustration and not intended to limit the present invention.

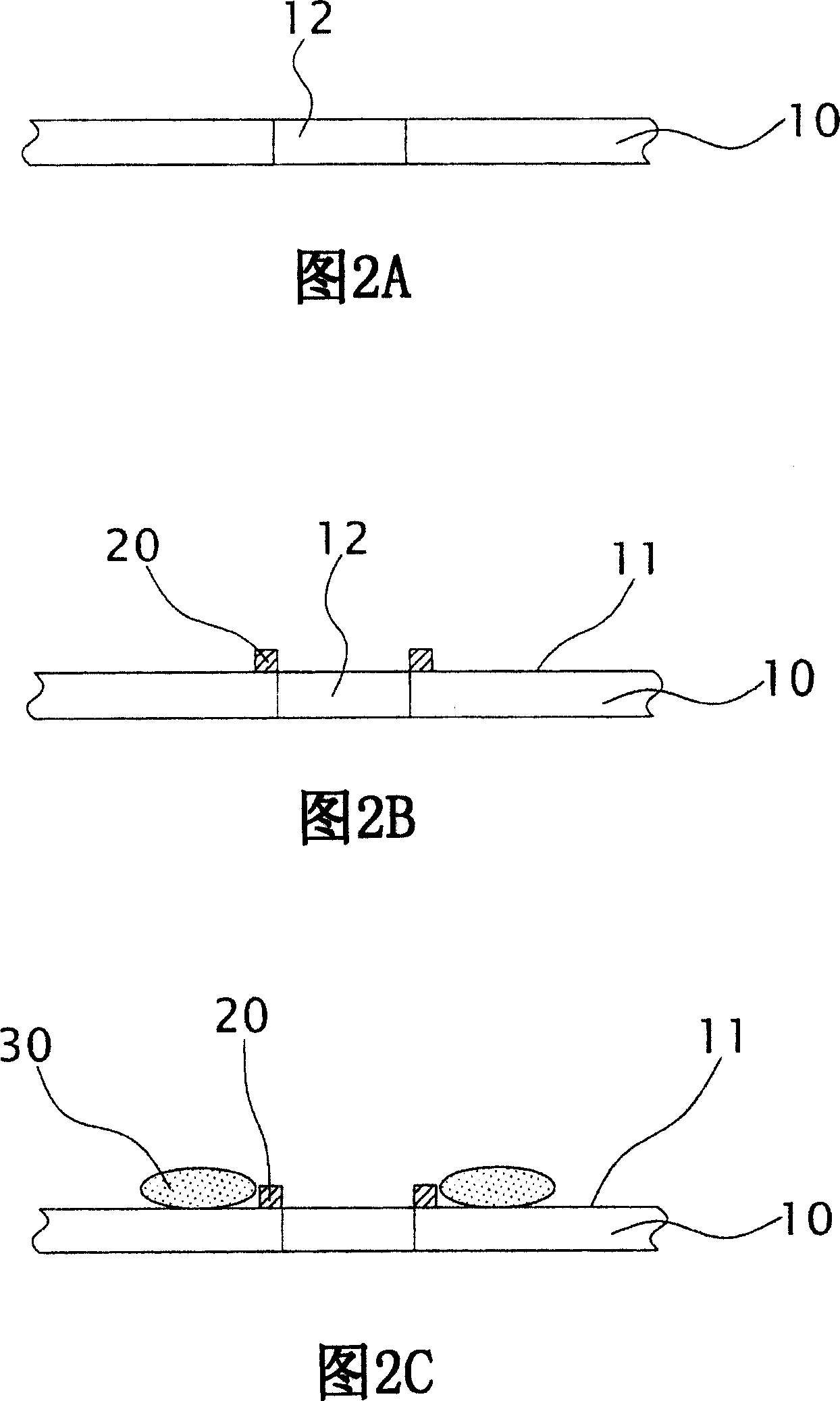

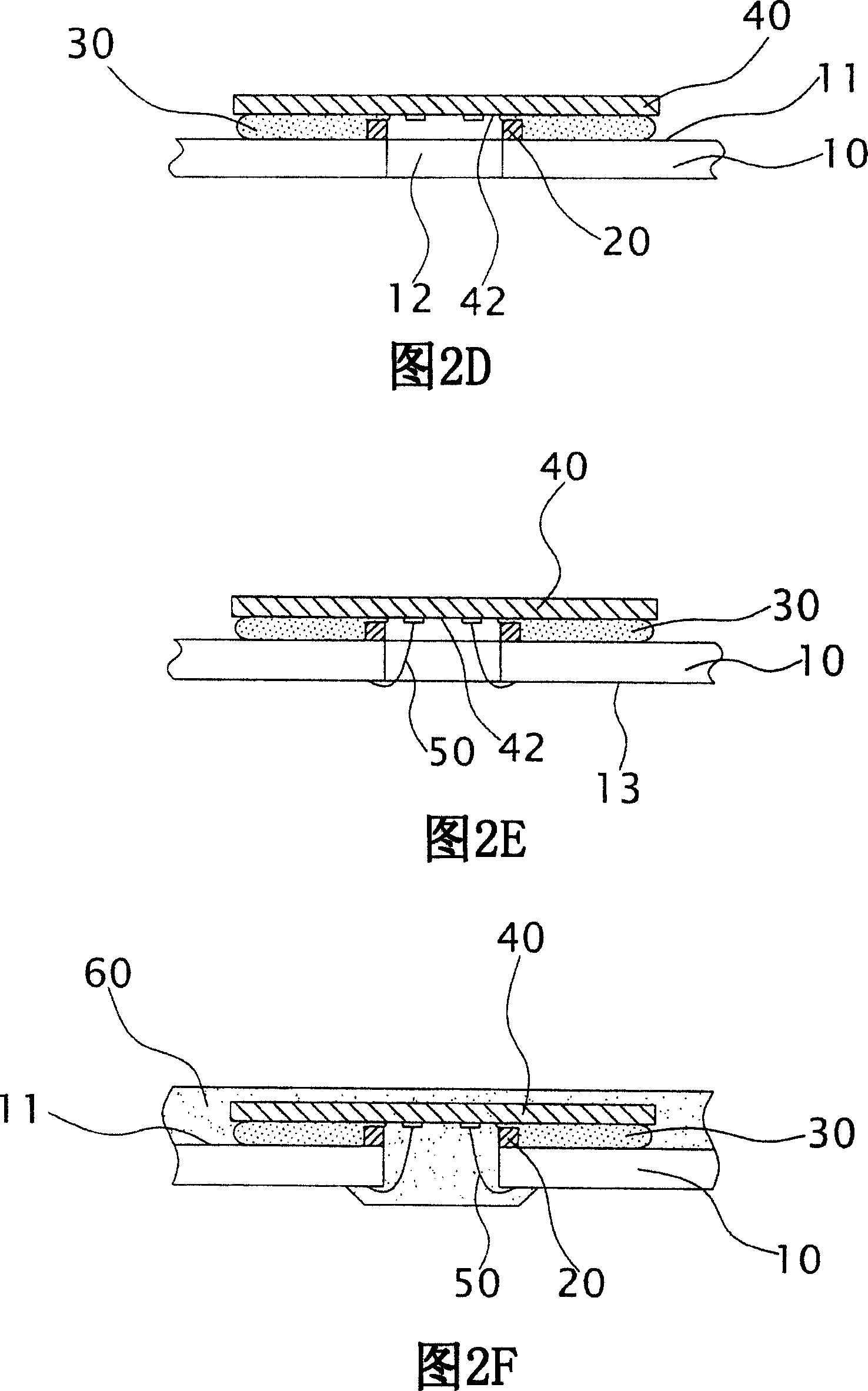

[0035] 2A , 2B, 2C, 2D, 2E, 2F, 2G-1 and 2G-2 are structural cross-sectional views of each step of the chip packaging structure manufacturing method according to an embodiment of the present invention. First, please refer to FIG. 2A, provide a substrate 10, its material is metal, glass, ceramics or polymer material, there is at least one opening 12 through the substrate 10, wherein the substrate 10 can be formed by using a suitable method to form the opening 12 through the substrate 10, or a commercialized structure having at least one opening 12.

[0036] Next, referring to FIG. 2B , a stopper element 20 is formed on the periphery of the opening 12 on the upper surface 11 of the substrate 100 . In one embodiment, the stop member 20 is formed by one of sputtering, vapor deposition, electroless plating and electroplating or by ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com