Multi-layer printed wiring board and manufacturing method thereof

A multi-layer printing, circuit board technology, applied in the directions of printed circuits, printed circuits, printed circuit manufacturing, etc., can solve the problems of peeling, easy cracking, poor ductility, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

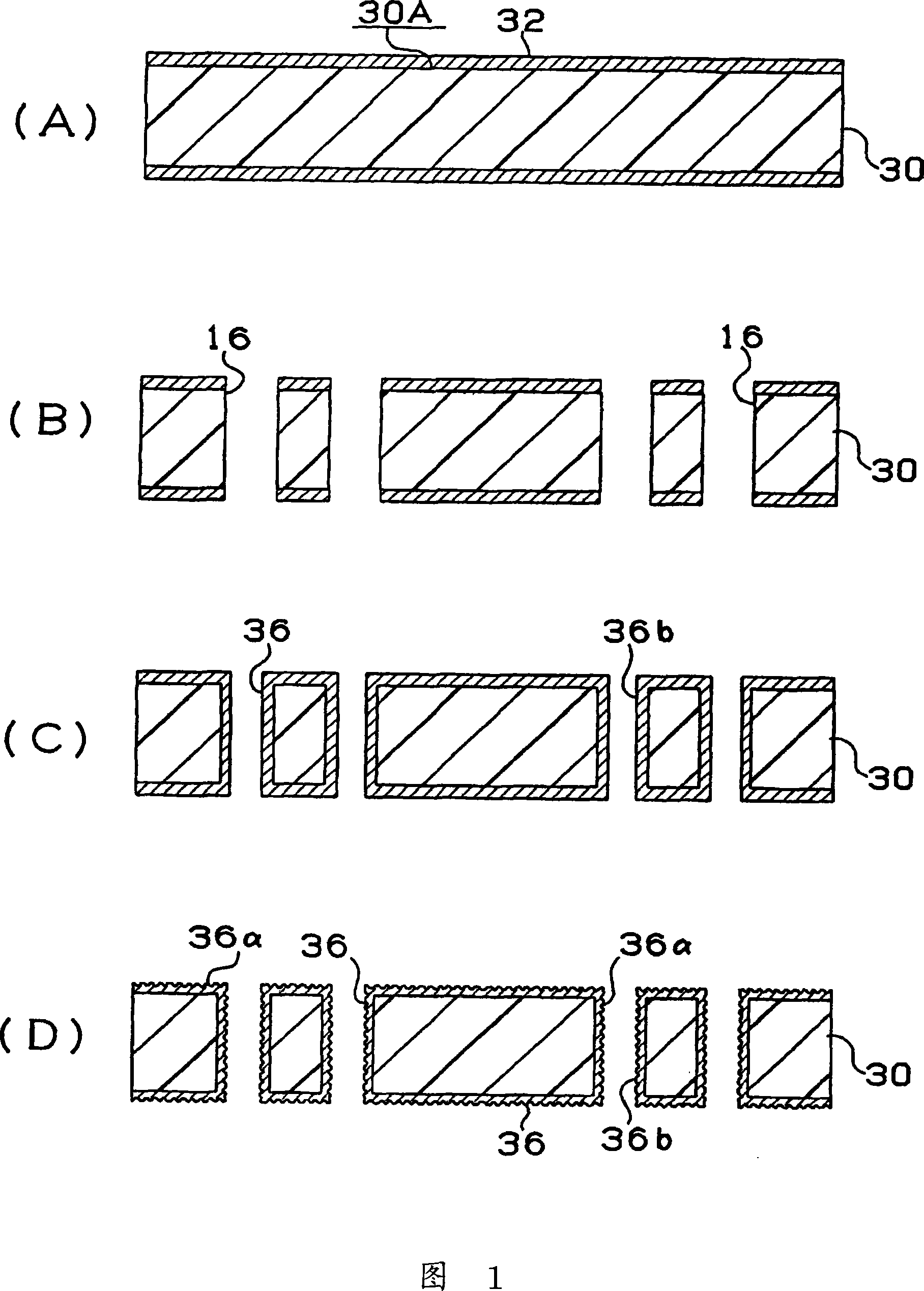

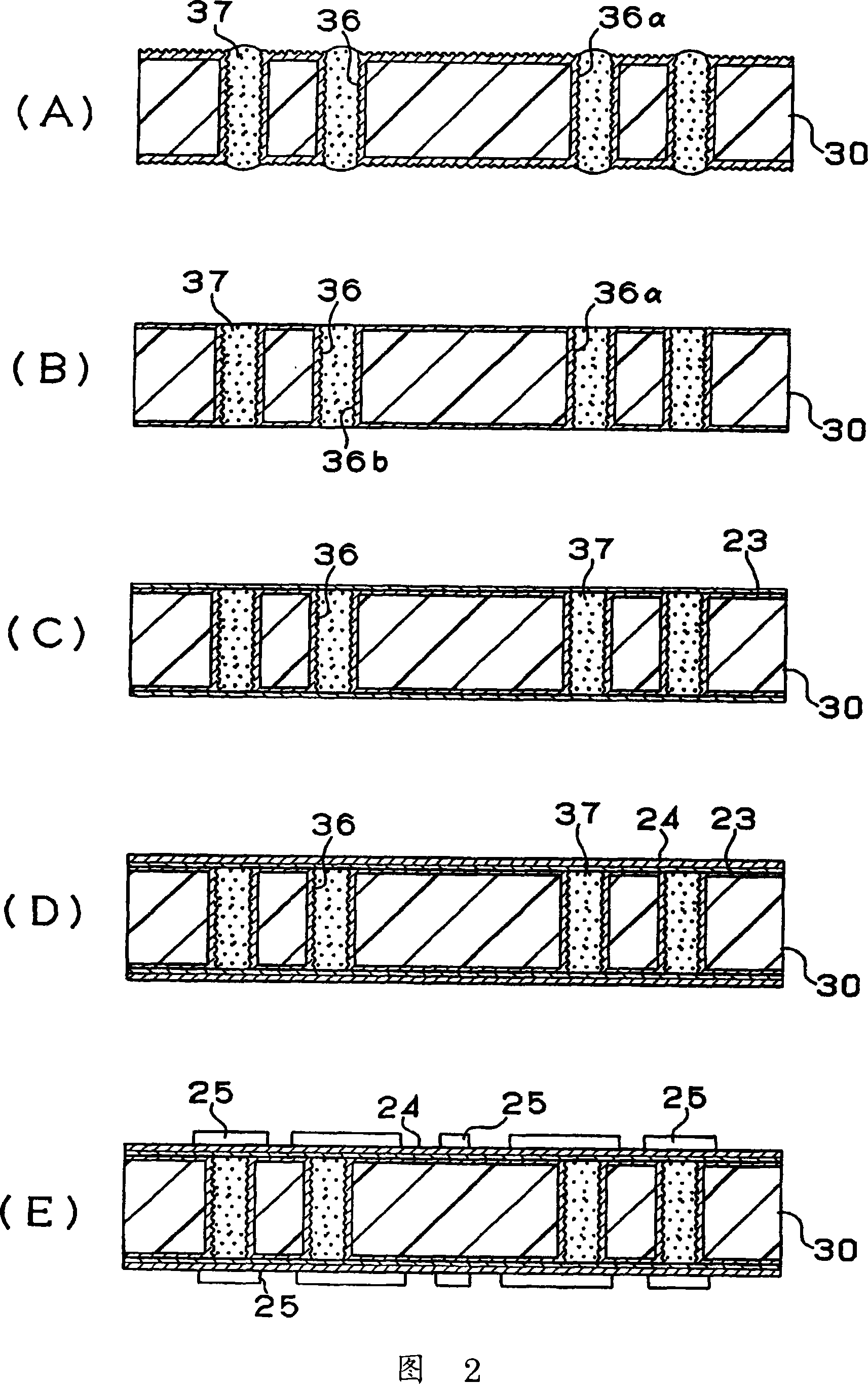

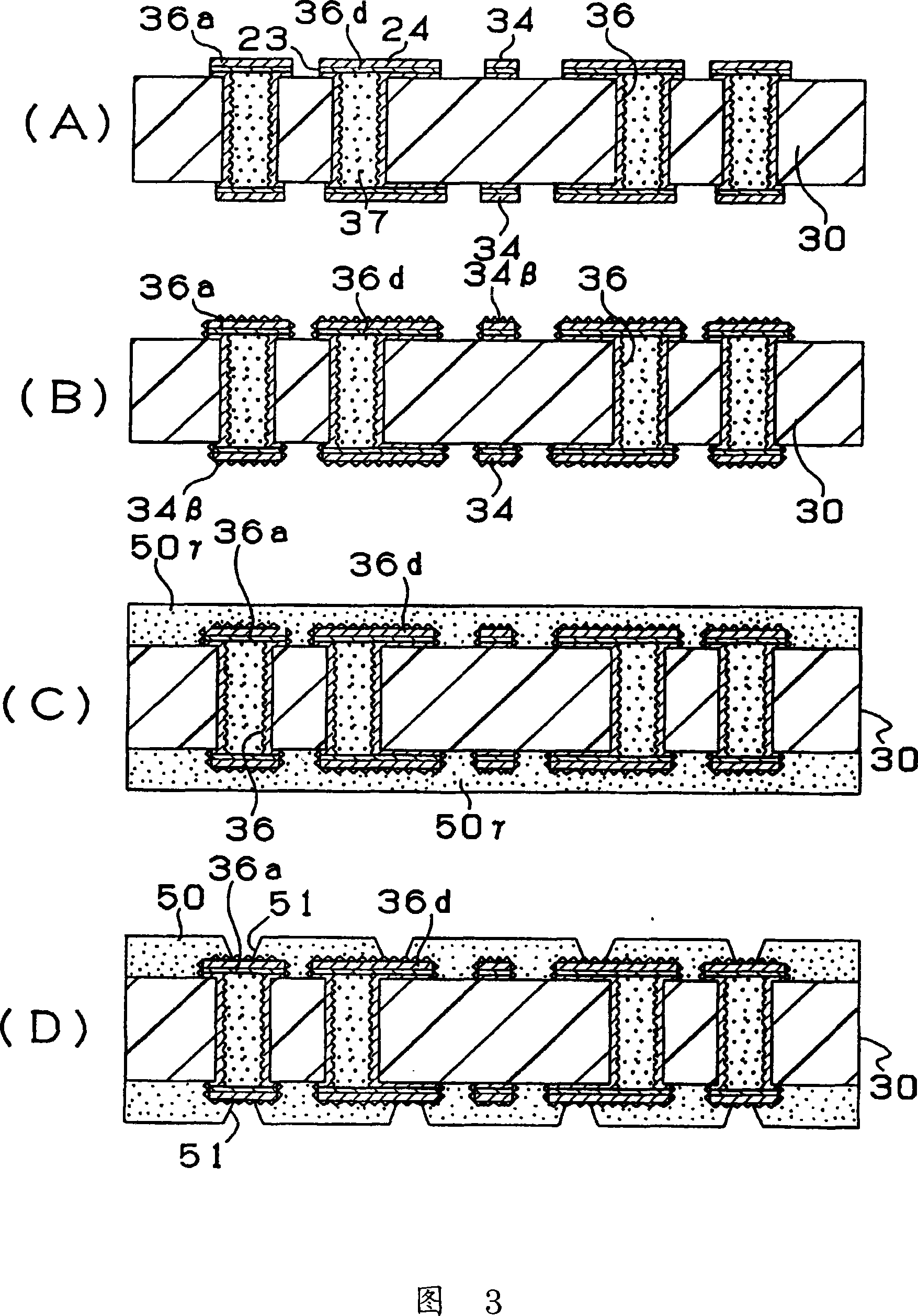

[0035] First, the structure of a multilayer printed wiring board 10 according to a first embodiment of the present invention will be described with reference to FIGS. 1 to 8 . FIG. 7 shows a cross-sectional view of the multilayer printed wiring board 10, and FIG. 8 shows a process of mounting an IC chip 90 on the multilayer printed wiring board 10 shown in FIG. state. As shown in FIG. 7 , in the multilayer printed wiring board 10 , a conductor circuit 34 is formed on the surface of the core substrate 30 . The front and back surfaces of the core substrate 30 are connected by through holes 36 . The through hole 36 is composed of cap-shaped plating layers 36a, 36d constituting a via land, and a sidewall conductor layer 36b, and the inside of the sidewall conductor layer 36b is filled with a resin filling material 37. The interlaminar resin insulating layer 50 and the interlaminar resin insulating layer 150 are disposed on the cap-shaped plating layers (via lands) 36a and 36d. ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| current density | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com