Semiconductor integrated circuit device

一种集成电路、半导体的技术,应用在半导体集成电路器件领域,能够解决未参考电流、未公开TDDB电场强度与布局关系等问题,达到改善ESD耐压的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

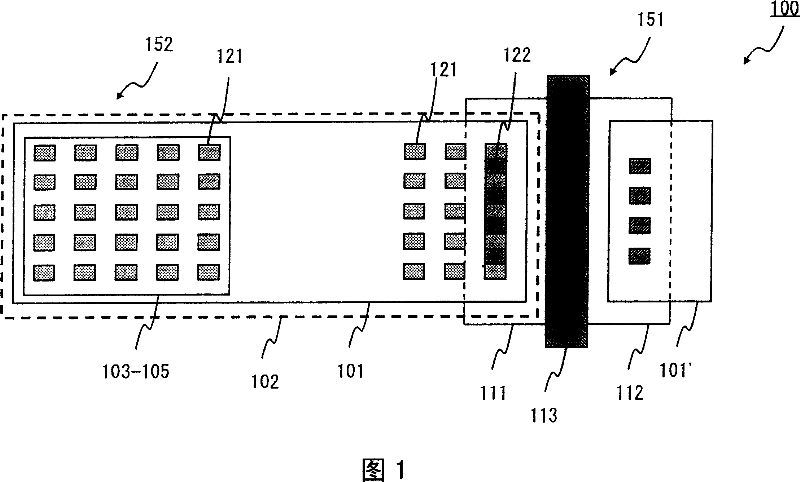

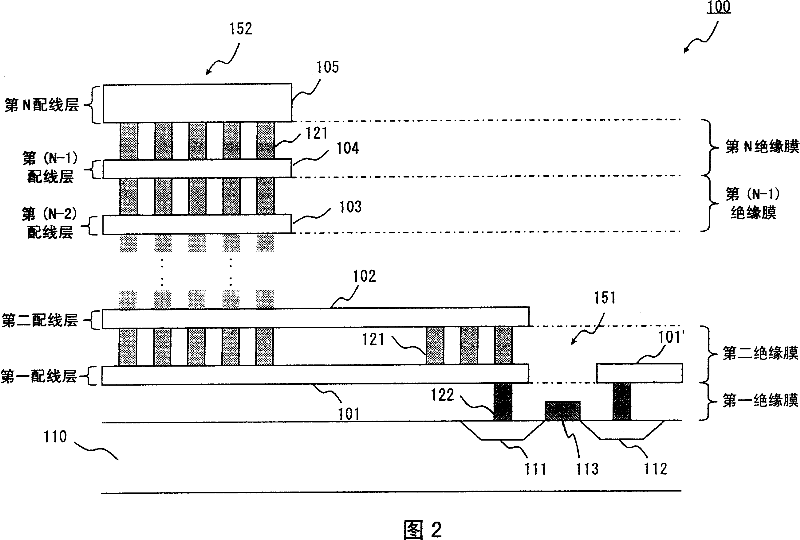

[0038] First, a semiconductor integrated circuit device according to a first embodiment of the present invention will be described. A low dielectric constant film is used for the insulating layer of the semiconductor integrated circuit device of this embodiment. In the semiconductor integrated circuit device of the present embodiment, metal lines extending toward the protection element are formed in a plurality of wiring layers.

[0039] The configuration of the semiconductor integrated circuit device of the present embodiment will be described below with reference to FIGS. 1 and 2 . 1 and 2 illustrate structures of input / output pads and protection elements of the semiconductor integrated circuit device 100 . 1 is a plan view of a semiconductor integrated circuit device 100, and FIG. 2 is a cross-sectional view of the semiconductor integrated circuit device 100 shown in FIG.

[0040] As shown in FIG. 2 , the semiconductor integrated circuit device 100 includes a protection e...

no. 2 example

[0063] Next, a semiconductor integrated circuit device according to a second embodiment of the present invention is described. A low dielectric constant film is used for the semiconductor integrated circuit device of this embodiment. Furthermore, the semiconductor integrated circuit device of the present embodiment has two power supply lines formed in different wiring layers.

[0064] The configuration of the semiconductor integrated circuit device of the present embodiment will be described below with reference to FIGS. 5A and 5B . 5A and 5B show the structure of the power supply line of the semiconductor integrated circuit device 200. As shown in FIG. FIG. 5A is a plan view of the semiconductor integrated circuit device 200 . FIG. 5B is a cross-sectional view of the semiconductor integrated circuit device 200 in FIG. 5A.

[0065] The semiconductor integrated circuit device 200 has a Vcc line 201 for supplying a power supply potential and a GND line 202 for supplying a gro...

no. 3 example

[0070] Next, a semiconductor integrated circuit device according to a third embodiment of the present invention is described. In the semiconductor integrated circuit device of this embodiment, a low dielectric constant film is used for the insulating layer. Furthermore, the semiconductor integrated circuit device of the present embodiment is characterized in that the source potential line and the drain potential line of the MOSFET are formed in different wiring layers.

[0071] The configuration of the semiconductor integrated circuit device 300 of the present embodiment will be described below with reference to FIGS. 6 and 7 . 6 and 7 show the structure of MOSFET and source / drain potential lines. FIG. 6 is a plan view of the semiconductor integrated circuit device 300 . FIG. 7 is a cross-sectional view of the semiconductor integrated circuit device 300 in FIG. 6. Referring to FIG.

[0072] As shown in FIG. 7 , the semiconductor integrated circuit device 300 includes a MOSF...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com