Wall embedding type shallow groove isolation structure and method for forming same

A shallow trench isolation and oxide technology, applied in electrical components, electrical solid-state devices, circuits, etc., to reduce parasitic transistor problems and improve thinning problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

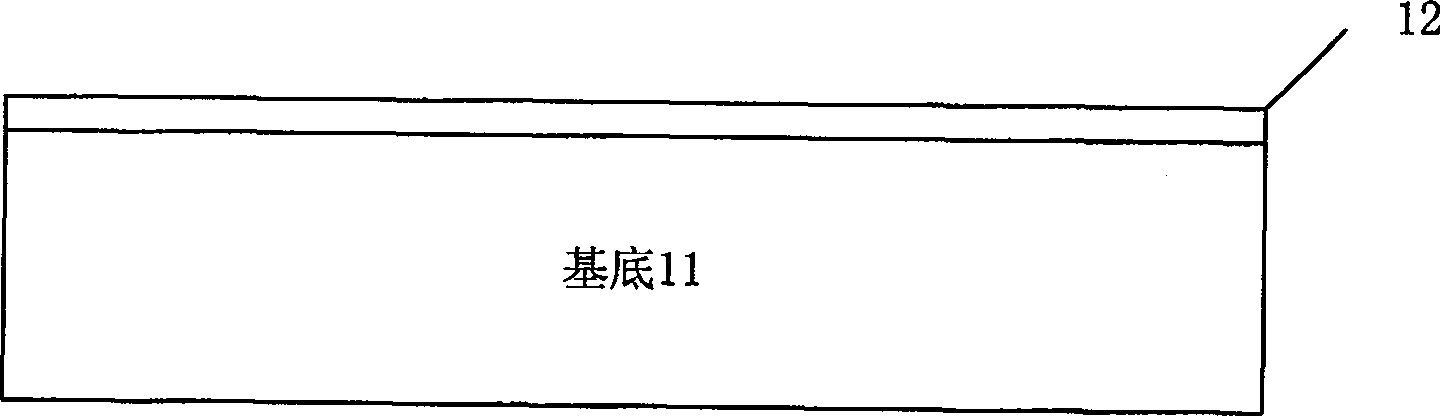

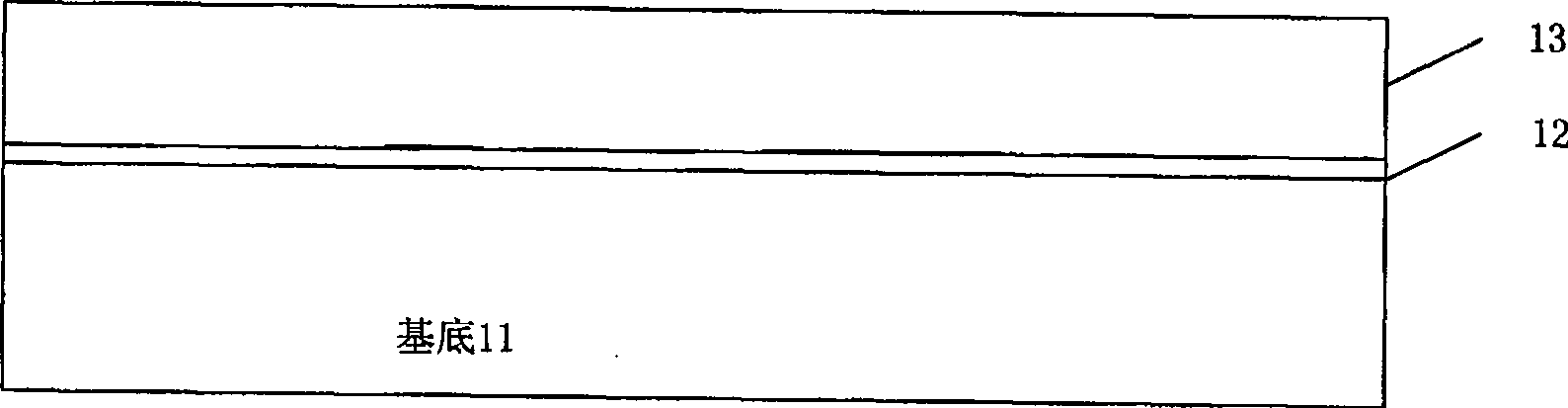

[0031] The thinned structure and formation method of the improved shallow trench isolation high voltage gate oxide in a preferred embodiment of the present invention are shown in the figure.

[0032] figure 1 represents the wafer substrate 11, figure 2 Indicates that a layer of pad oxide (PAD oxide) 12 is covered on the wafer substrate 11, image 3 It means that a layer of hard mask layer (Hardmask) 13 is deposited on the pad oxide layer 12, and the material of the hard mask layer can be silicon nitride or any other suitable material. Figure 4 expressed in image 3 In the shown structure, a layer of photoresist (Photo-Resistance) 14 is firstly coated on the surface of the pad oxide layer 12, and then the photoresist 14 at the place where the groove needs to be formed is removed, and the part where the groove needs to be formed is defined, and then the photo-resistance 14 is removed by drying. Grooves are formed by etching or wet etching, and of course other etching method...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com