Method of manufacturing dielectric layer of grid

A technology for a gate dielectric layer and a manufacturing method, which is applied in the field of semiconductor component manufacturing, can solve the problems of reducing component stability and reliability, reducing process yield, increasing power consumption, etc., so as to avoid thinning and improve reliability. and stability, the effect of preventing junction leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

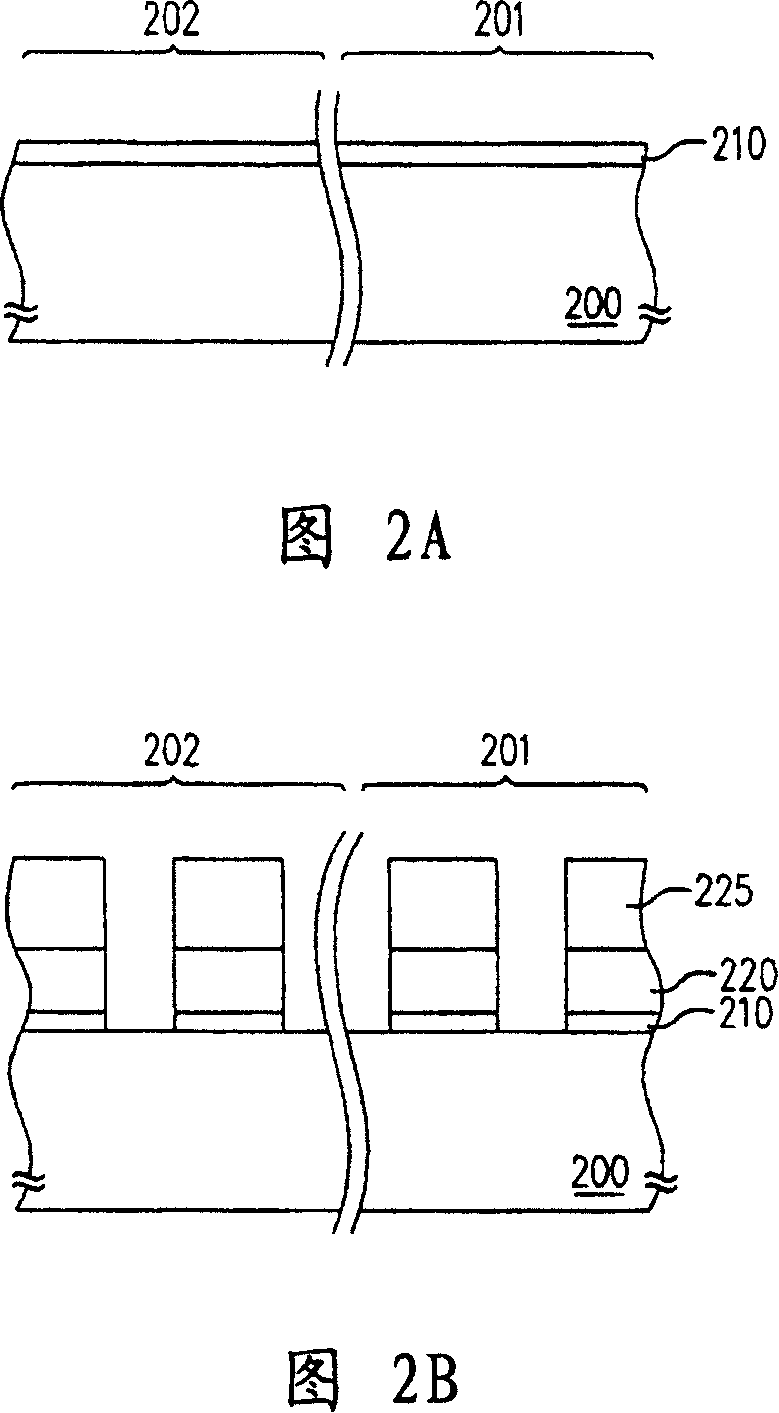

[0046] 2A to 2F are cross-sectional views illustrating a manufacturing process of a gate dielectric layer according to a preferred embodiment of the present invention.

[0047] Please refer to FIG. 2A , in this manufacturing method, for example, a substrate 200 is firstly provided, and the substrate 200 can be at least divided into a high-voltage circuit area 201 and a low-voltage circuit area 202 . Then, for example, RCA solution (ammonia NH 4 OH and hydrogen peroxide H 2 o 2mixed solution) to perform a cleaning step on the substrate 200. Afterwards, a dielectric layer 210 is formed on the substrate 200 . The dielectric layer 210 is used as a gate dielectric layer in the high-voltage circuit region 201 , so the thickness of the dielectric layer 210 is thicker than the existing pad oxide layer, and the thickness of the dielectric layer 210 is about 200˜1000 angstroms. The forming method of the dielectric layer 210 is, for example, a thermal oxidation method.

[0048] Afte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com