Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

56 results about "Decimal floating point" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

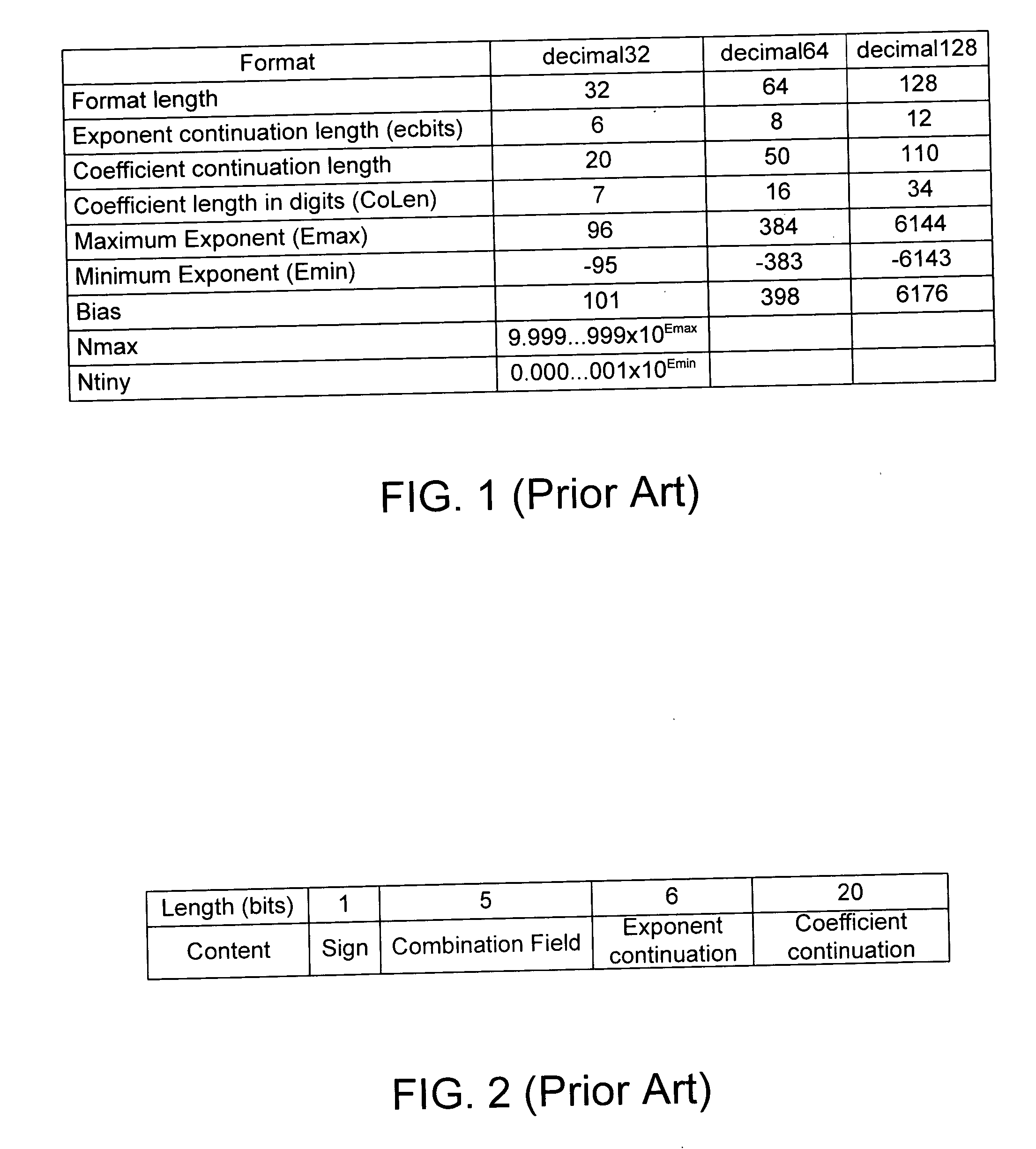

Decimal floating-point (DFP) arithmetic refers to both a representation and operations on decimal floating-point numbers. Working directly with decimal (base-10) fractions can avoid the rounding errors that otherwise typically occur when converting between decimal fractions (common in human-entered data, such as measurements or financial information) and binary (base-2) fractions.

Order-preserving encoding formats of floating-point decimal numbers for efficient value comparison

ActiveUS20070050436A1Fast and direct string comparisonDigital computer detailsRecord information storageFloating pointData type

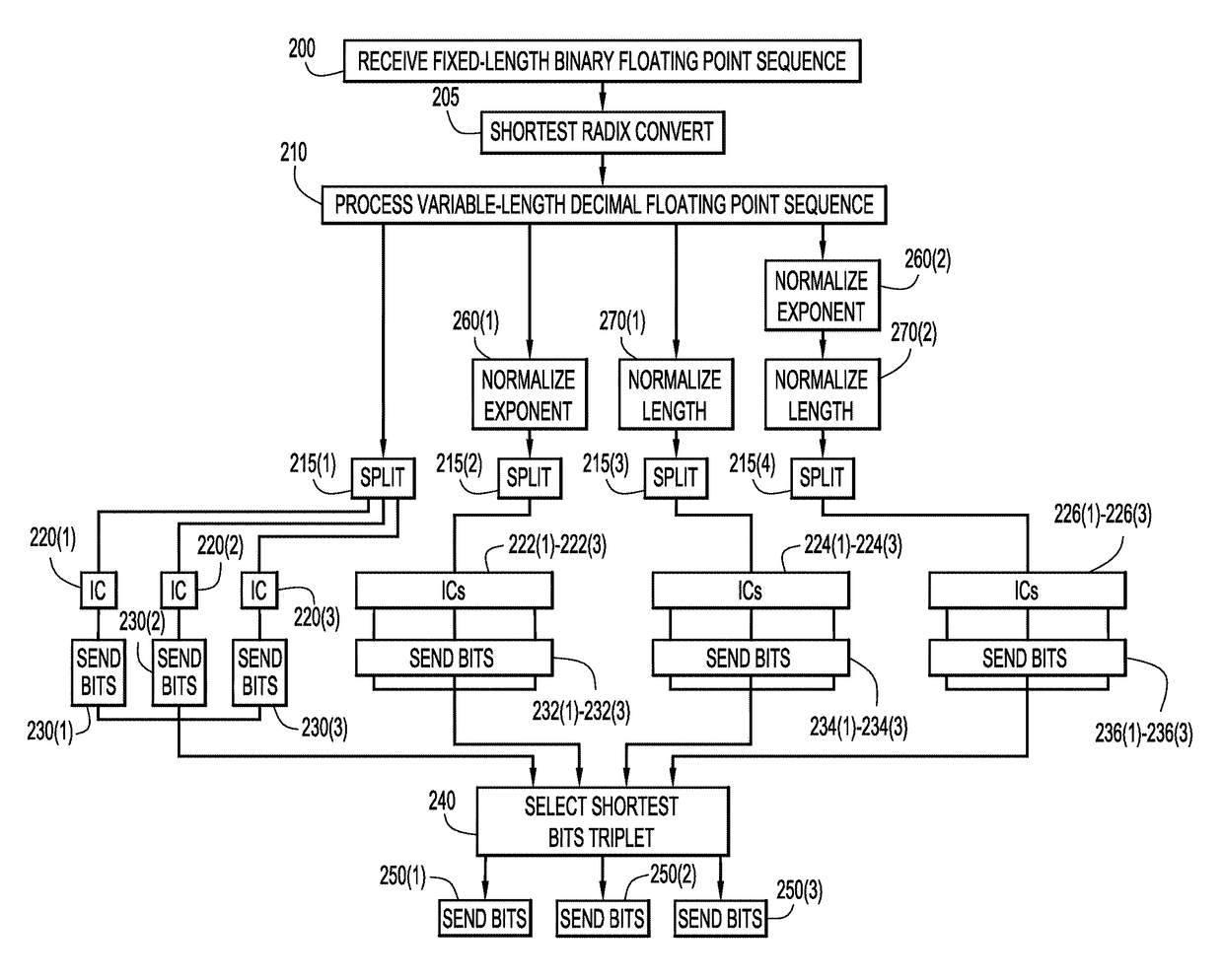

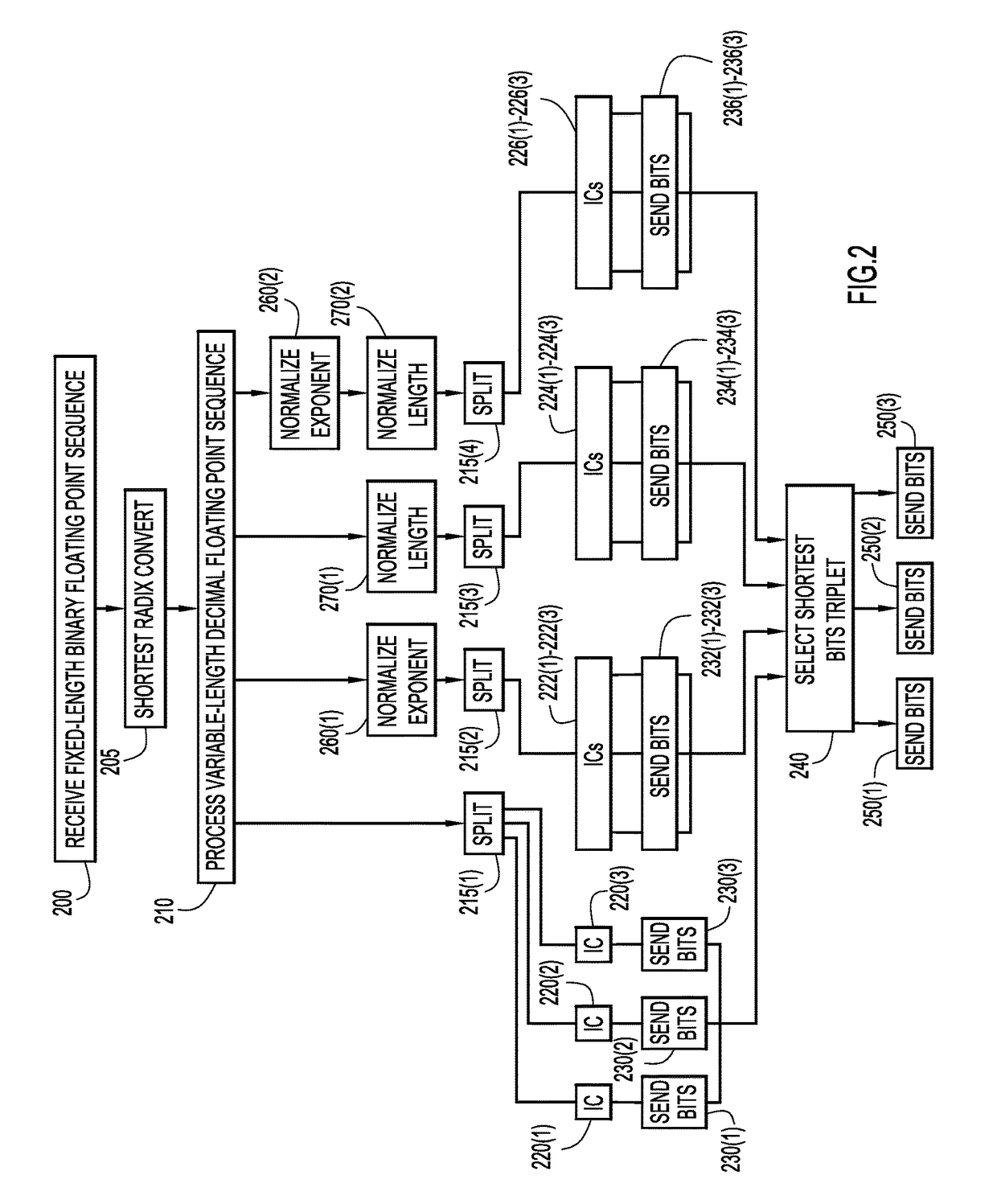

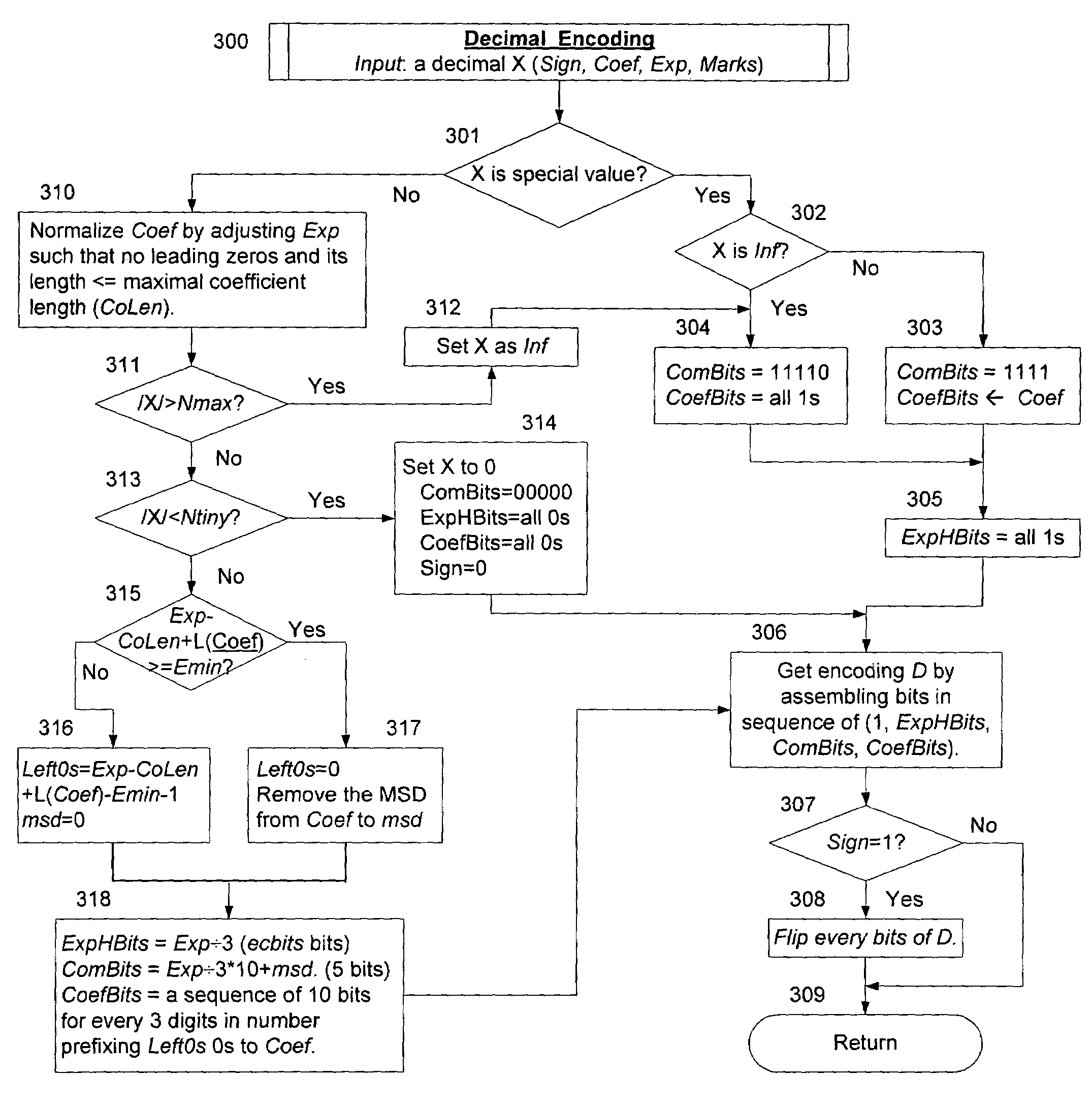

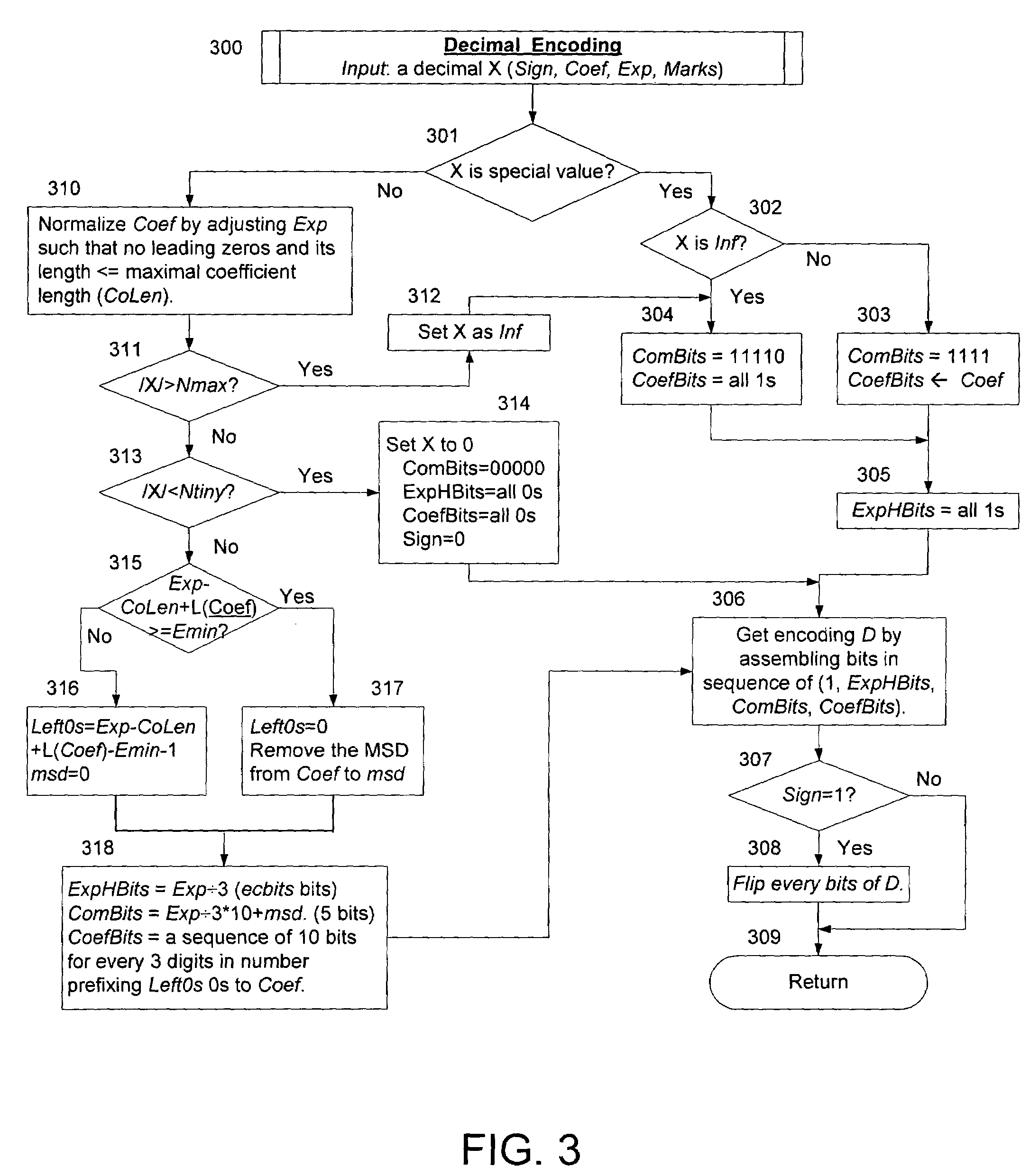

A method for conversion between a decimal floating-point number and an order-preserving format has been disclosed. The method encodes numbers in the decimal floating-point format into a format which preserves value ordering. This encoding allows for fast and direct string comparison of two values. Such an encoding provides normalized representations for decimal floating-point numbers and supports type-insensitive comparisons. Type-insensitive comparisons are often used in database management systems, where the data type is not specified for values to compare. In addition, the original decimal floating-point format can be recovered from the order-preserving format.

Owner:TWITTER INC

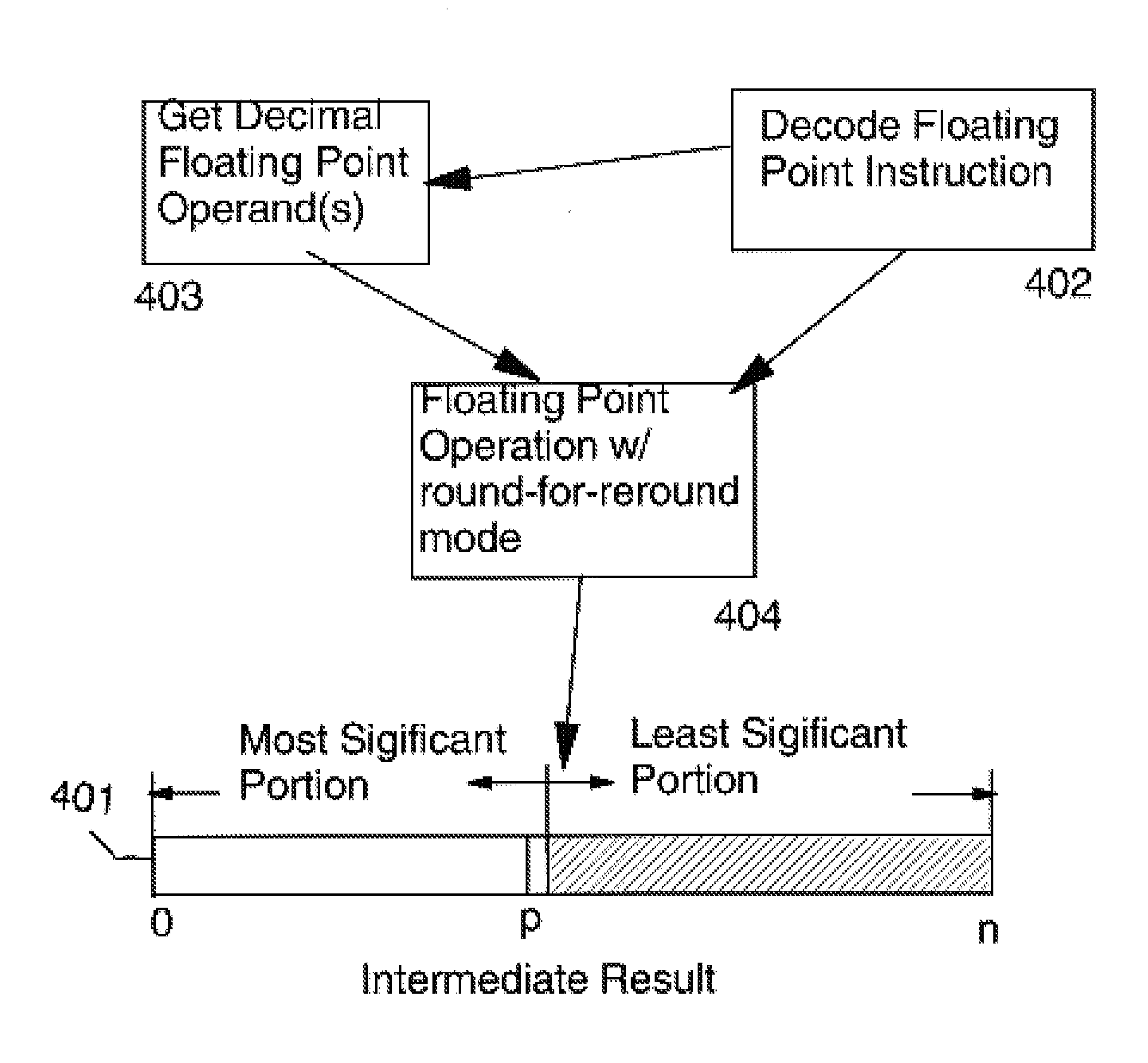

Round for Reround Mode in a Decimal Floating Point Instruction

ActiveUS20080215659A1Computations using magnetic elementsProgram controlParallel computingFloating point

a round-far-reround mode (preferably in a BID encoded Decimal format) of a floating point instruction prepares a result for later rounding to a variable number of digits by detecting that the least significant digit may be a 0, and if so changing it to 1 when the trailing digits are not all 0. A subsequent reround instruction is then able to round the result to any number of digits at least 2 fewer than the number of digits of the result. An optional embodiment saves a tag indicating the fact that the low order digit of the result is 0 or 5 if the trailing bits are non-zero in a tag field rather than modify the result. Another optional embodiment also saves a half-way-and-above indicator when the trailing digits represent a decimal with a most significant digit having a value of 5. An optional subsequent rewound instruction is able to round the result to any number of digits fewer or equal, to the number of digits of the result using the saved tags.

Owner:IBM CORP

Shift significand of decimal floating point data

ActiveUS20080270756A1Digital data processing detailsDigital computer detailsParallel computingSialic acid synthase

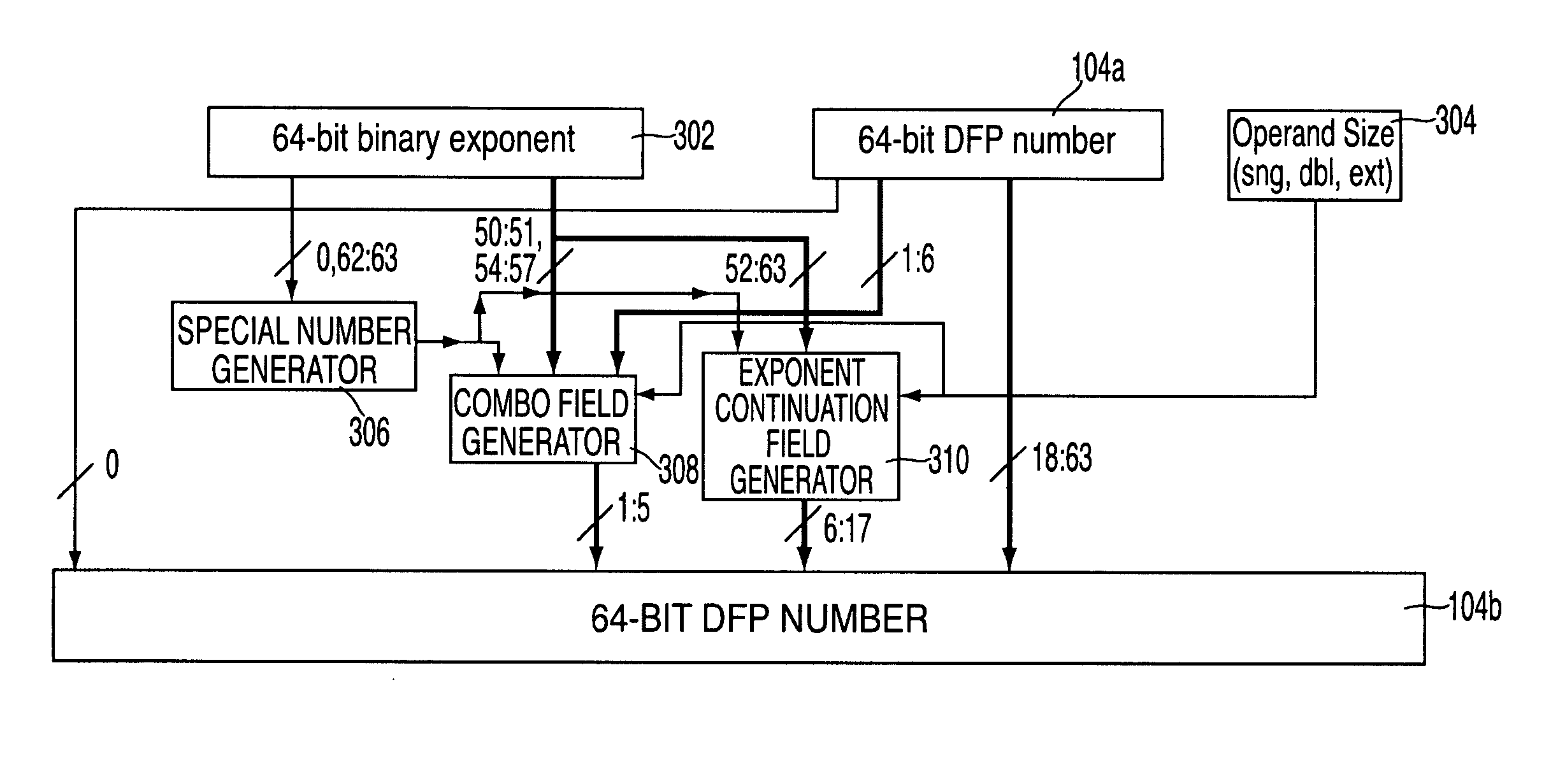

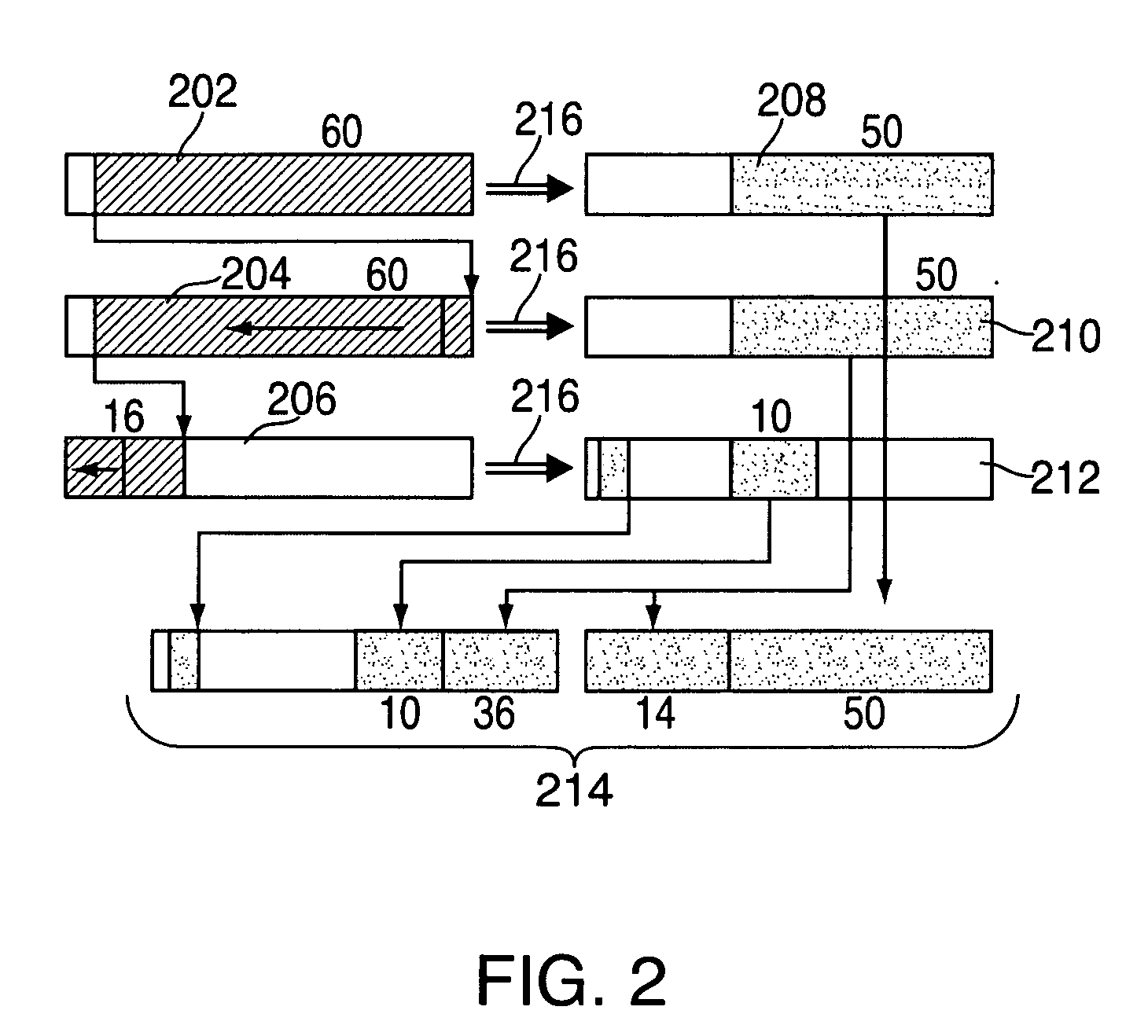

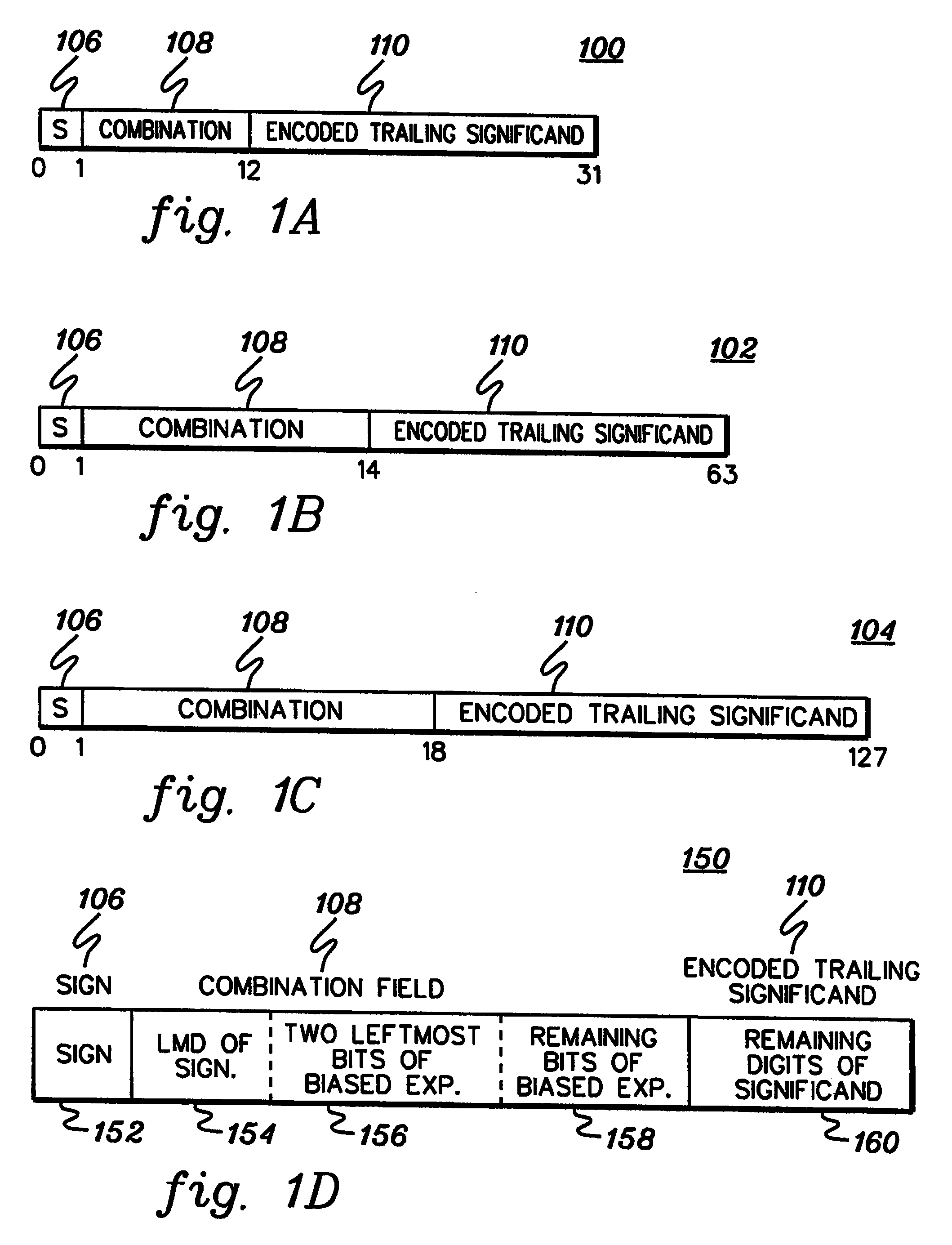

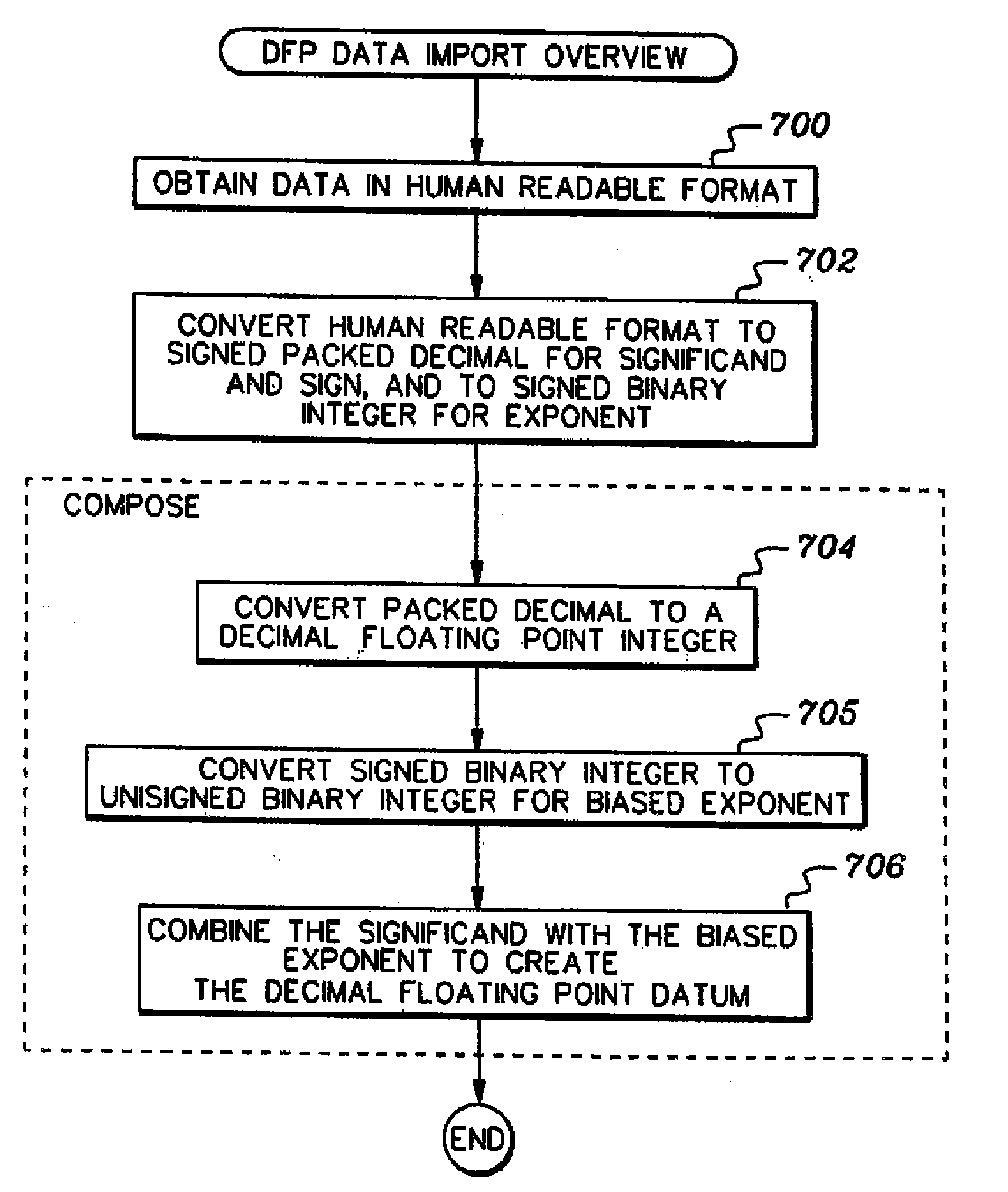

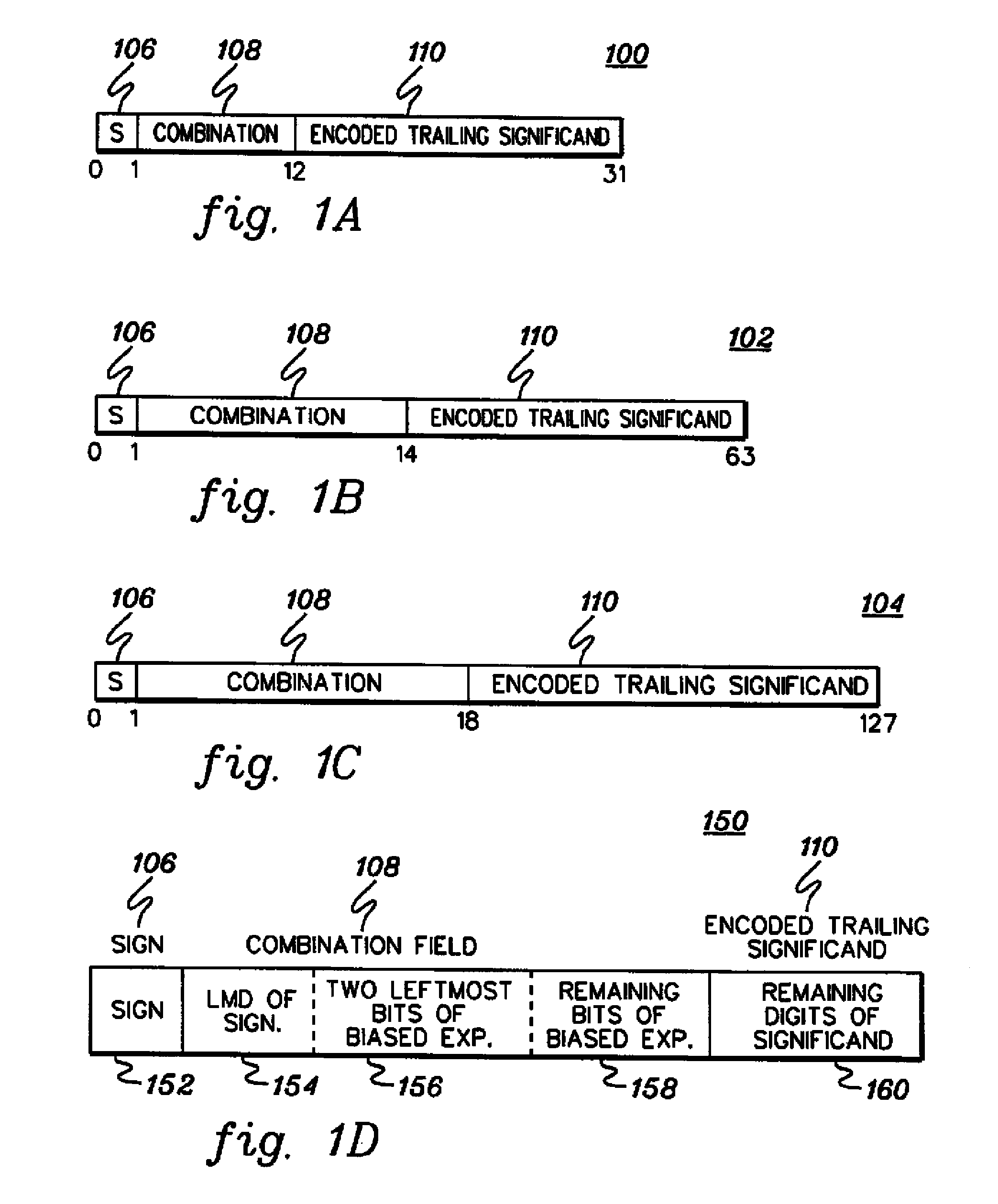

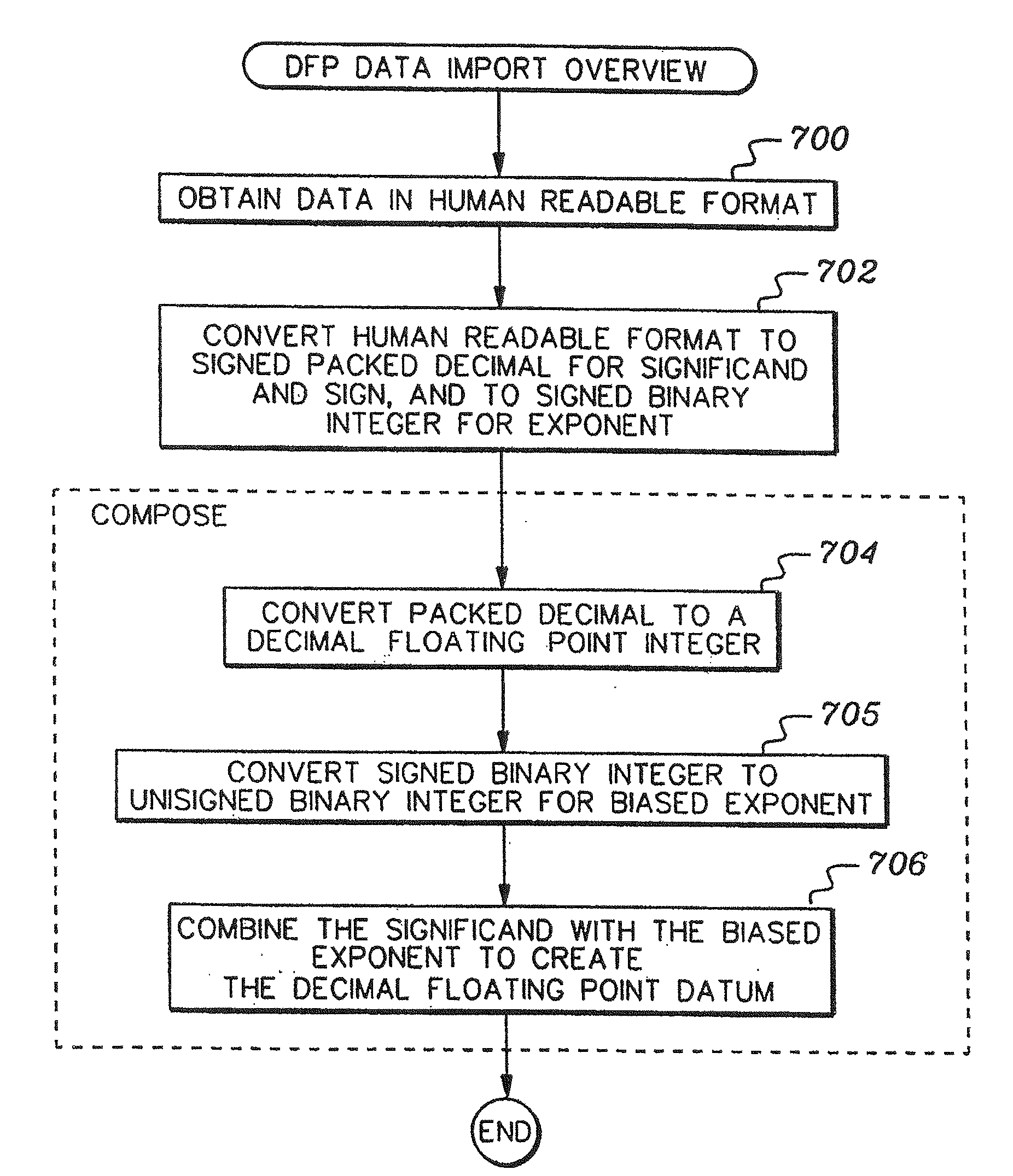

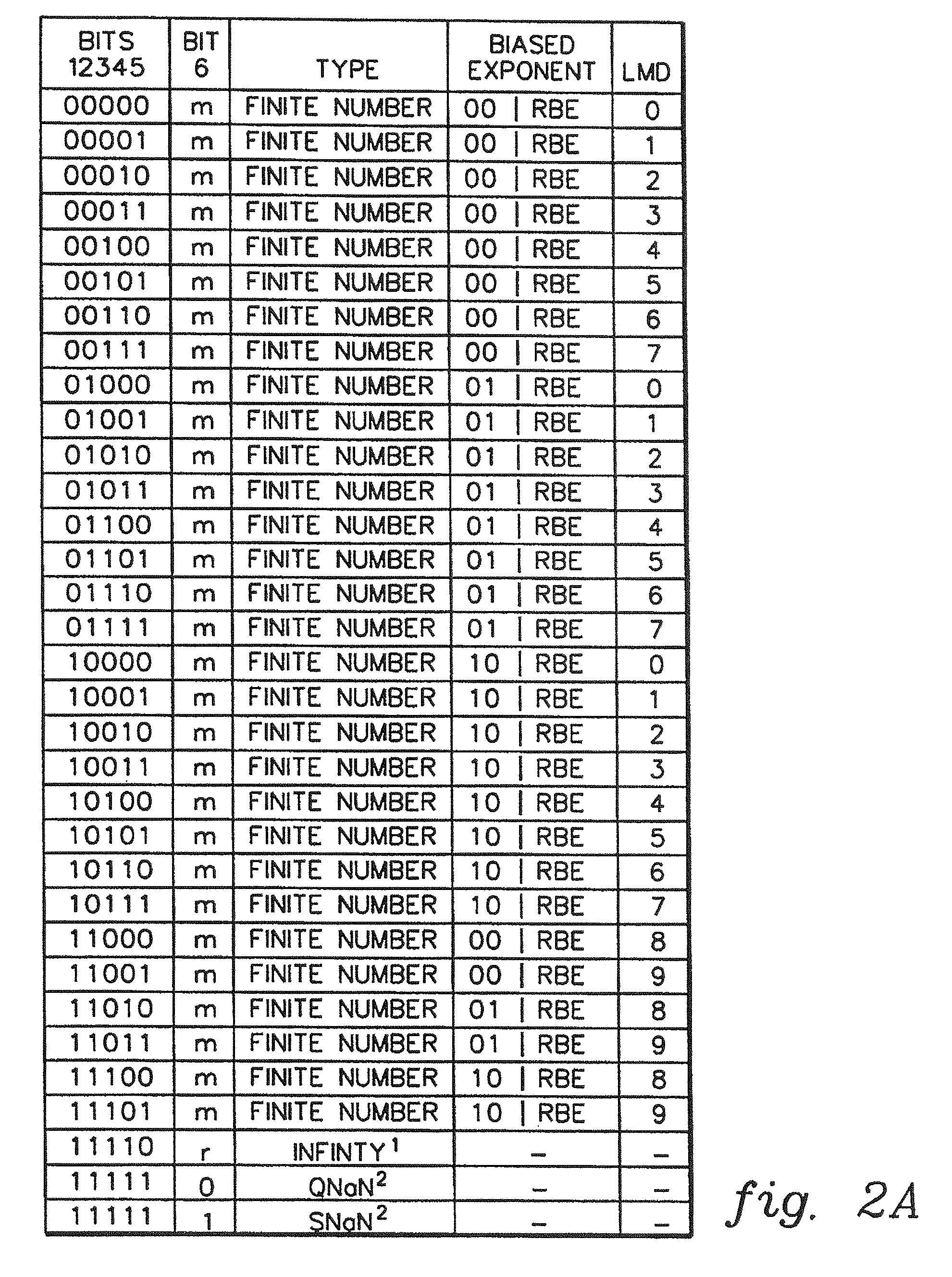

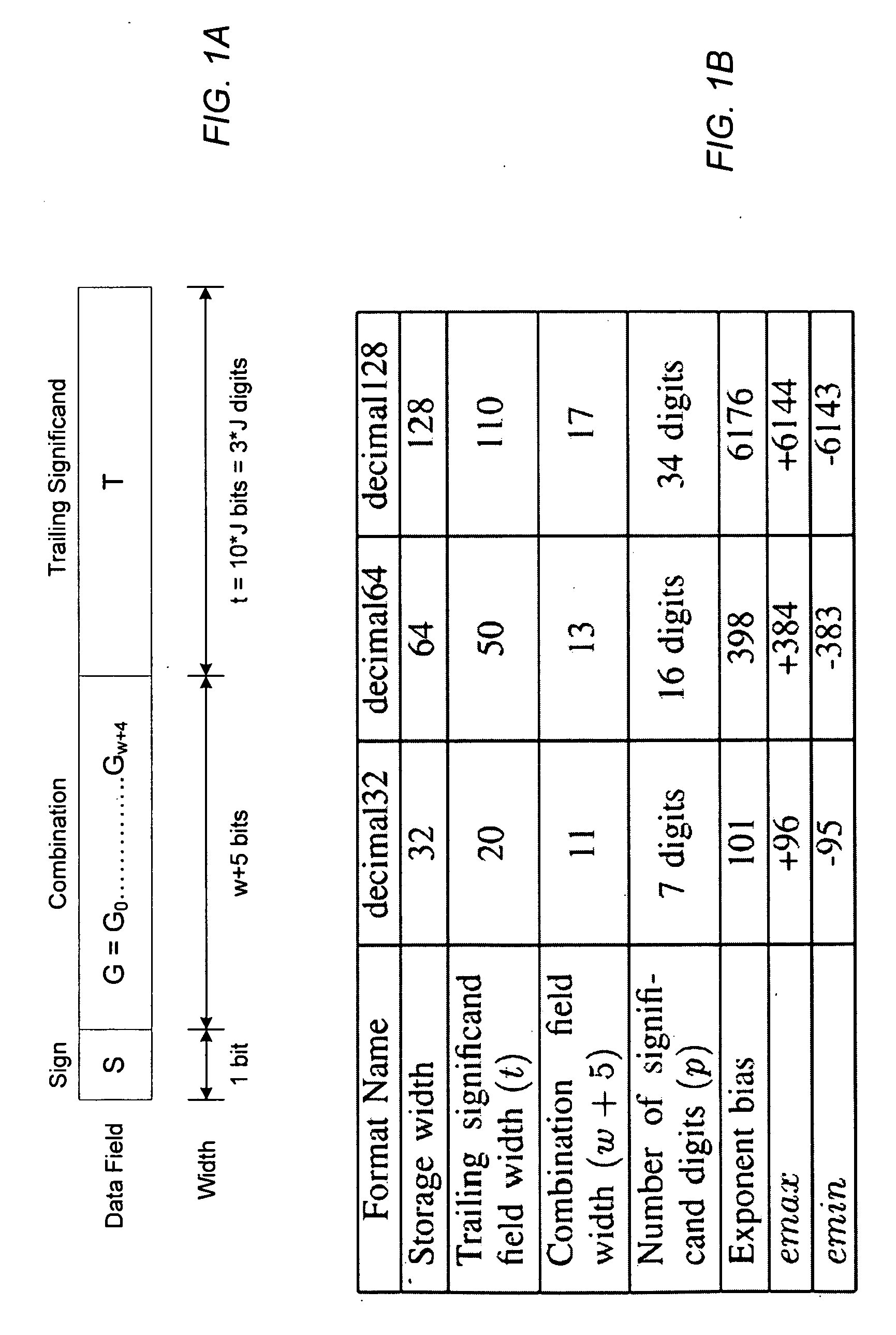

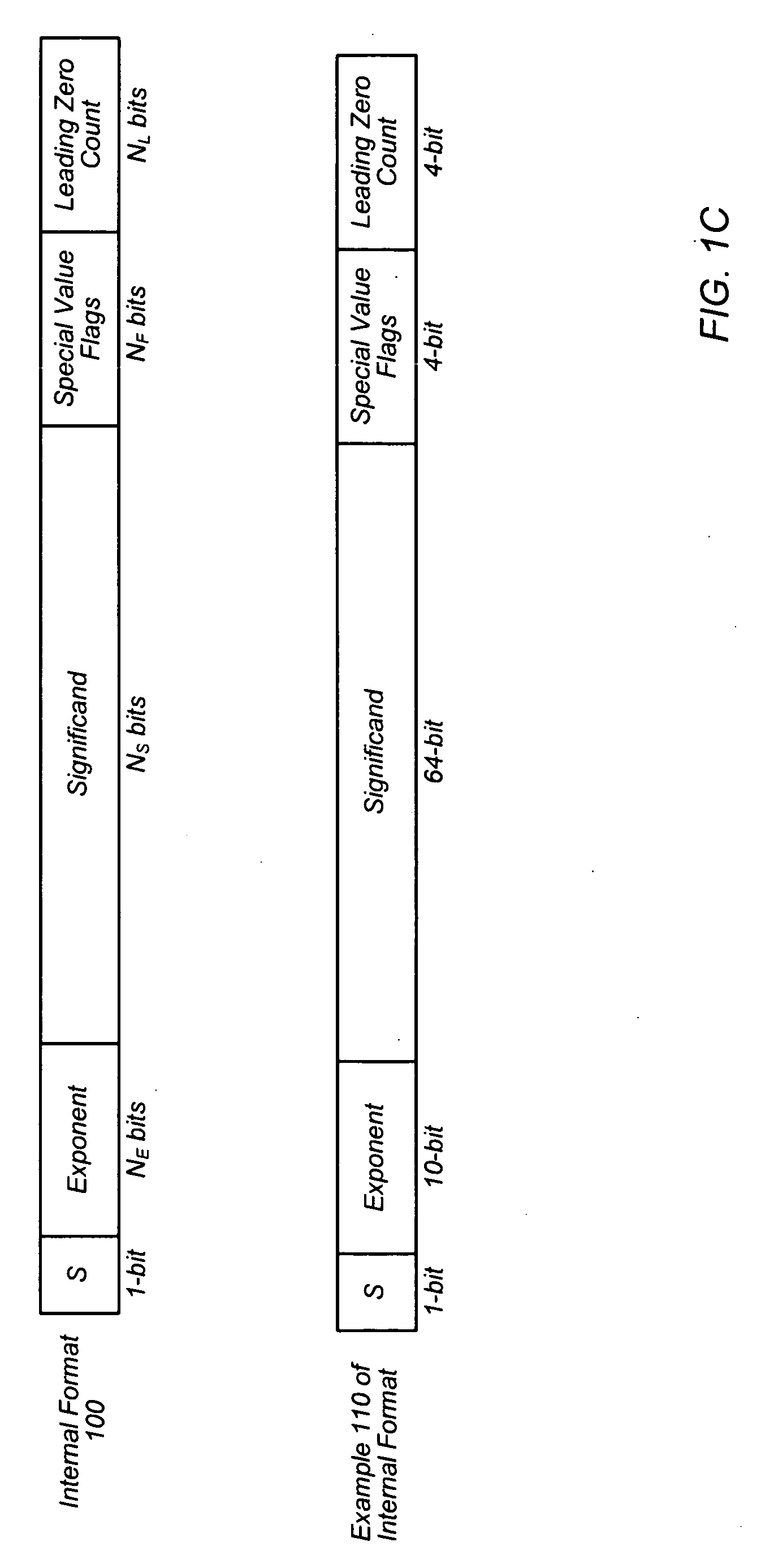

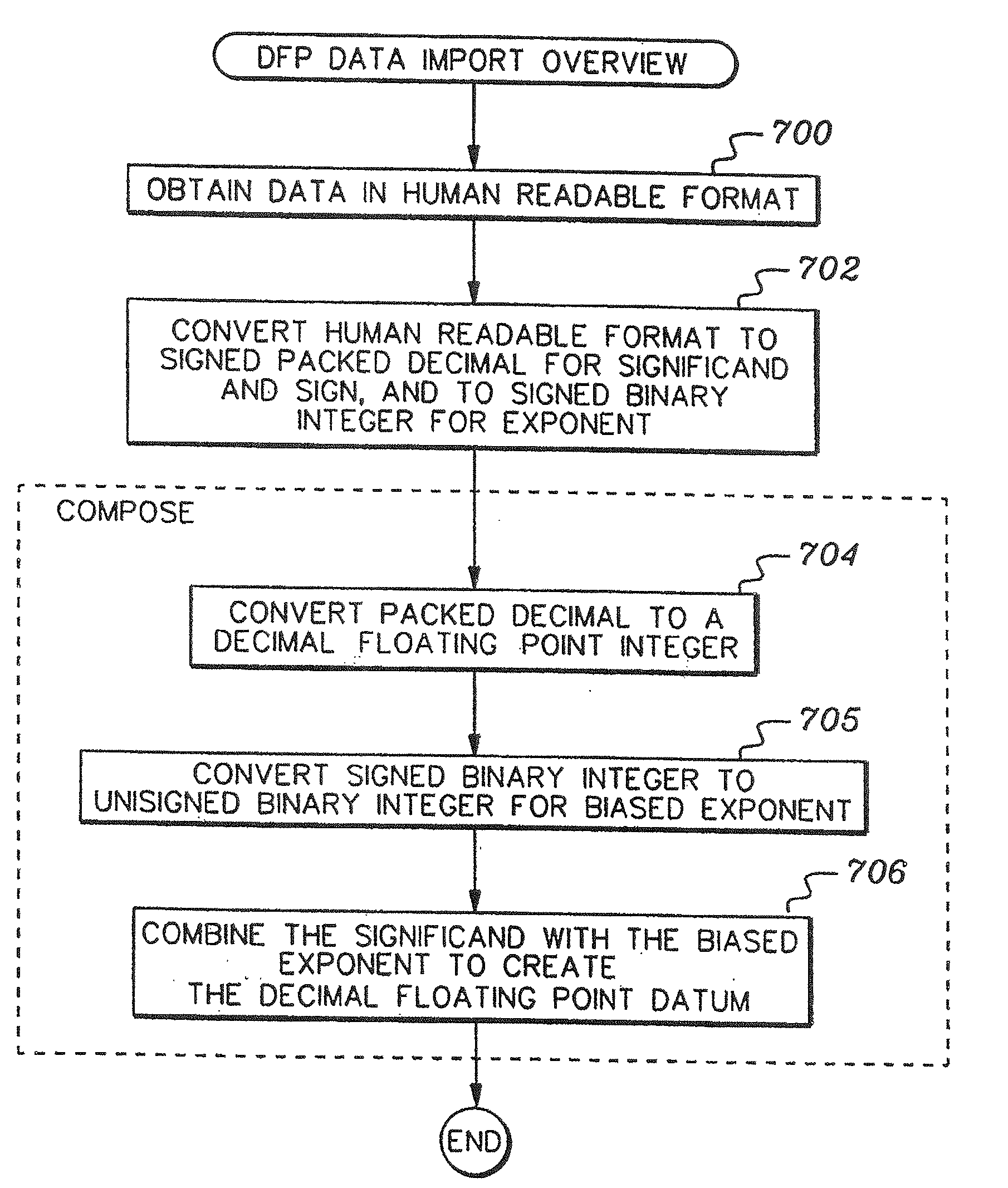

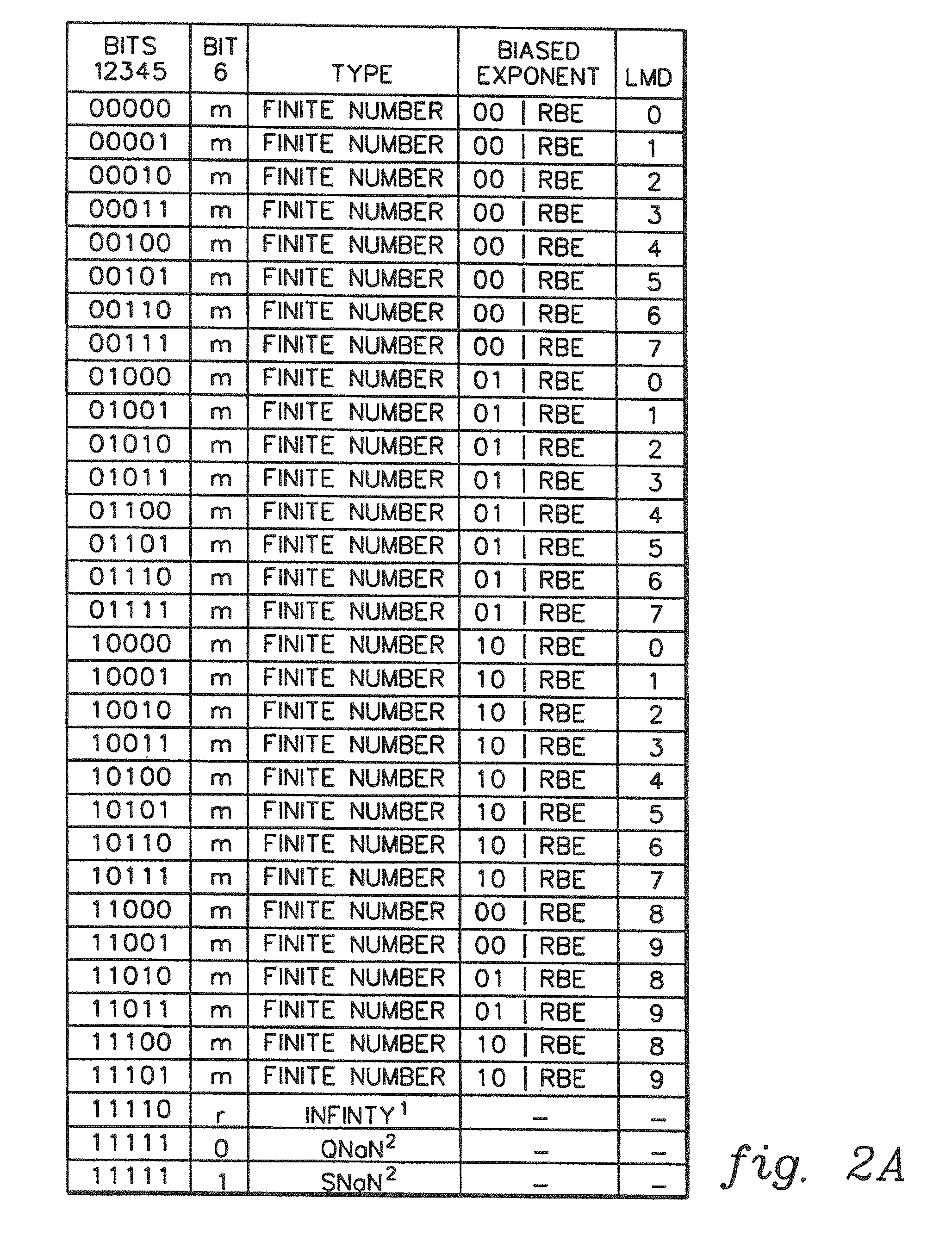

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format. For composition and decomposition, one or more instructions may be employed, including a shift significand instruction.

Owner:IBM CORP

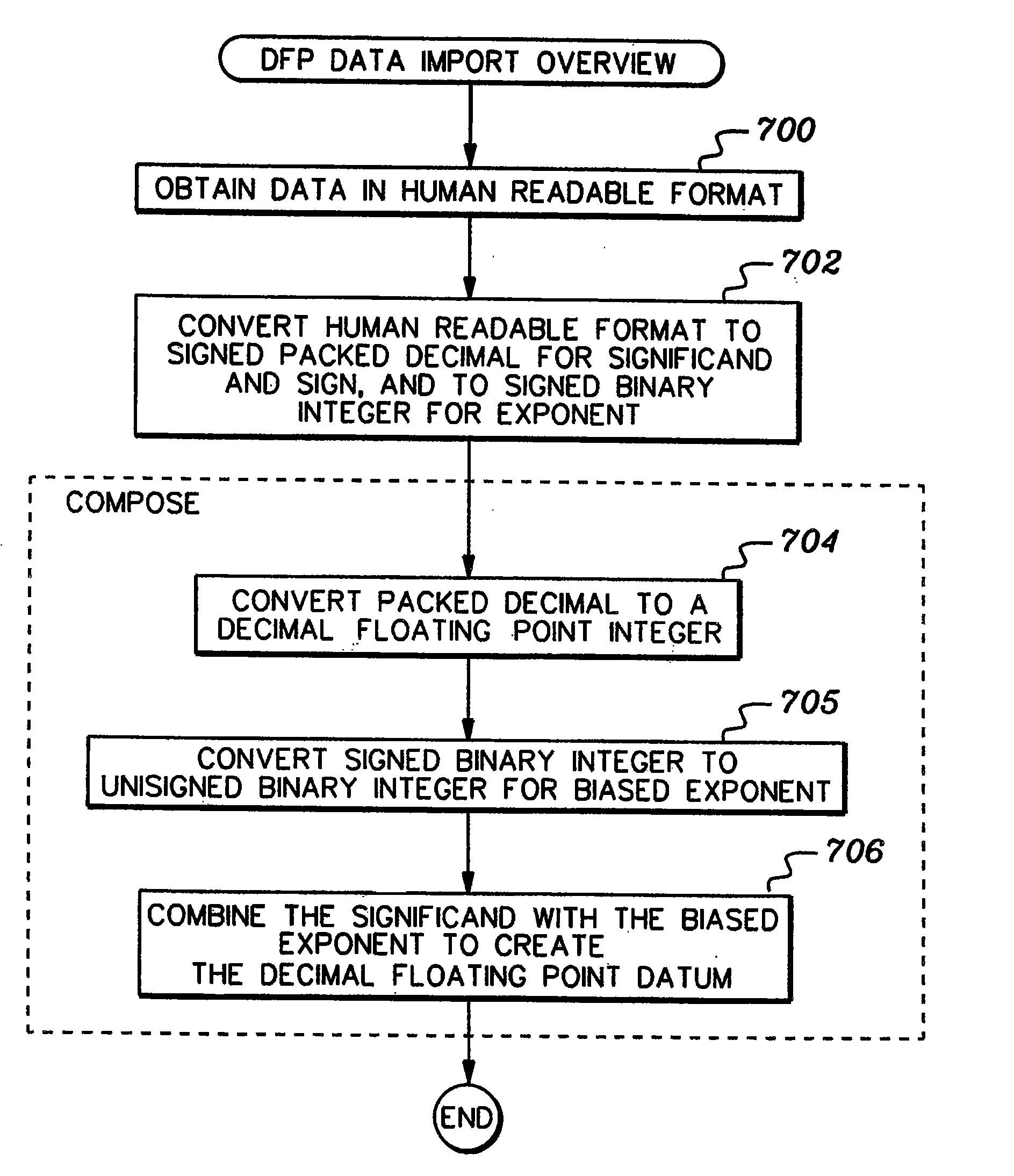

Convert significand of decimal floating point data from packed decimal format

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format. For composition and decomposition, one or more instructions may be employed, including one or more convert instructions.

Owner:IBM CORP

System and method for converting from decimal floating point into scaled binary coded decimal

A system and method for converting from decimal floating point (DFP) into scaled binary coded decimal (SBCD). The system includes a mechanism for receiving a DFP number. The system also includes at least one of a mechanism for performing coefficient expansion on the DFP number to create a binary coded decimal (BCD) coefficient part of a SBCD number and a mechanism for performing exponent extraction on the DFP number to create an exponent part of the SBCD number.

Owner:IBM CORP

Composition/decomposition of decimal floating point data

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format.

Owner:IBM CORP

Method and apparatus for automatically converting numeric data to a processor efficient format for performing arithmetic operations

A compiler (or interpreter) detects source language instructions performing arithmetic operations using a fixed point format (preferably packed decimal). Where the operation can be performed without loss of precision or violation of other constraints of the source language, the compiler automatically converts the operands to a floating point format (preferably Decimal Floating Point (DFP)) having hardware support, and re-converts results to the original fixed point format. Preferably, the compiler may combine multiple operations and instructions in an expression tree, analyze the tree, and selectively convert where possible. The compiler preferably performs a heuristic cost judgment in determining whether to use a particular conversion.

Owner:IBM CORP

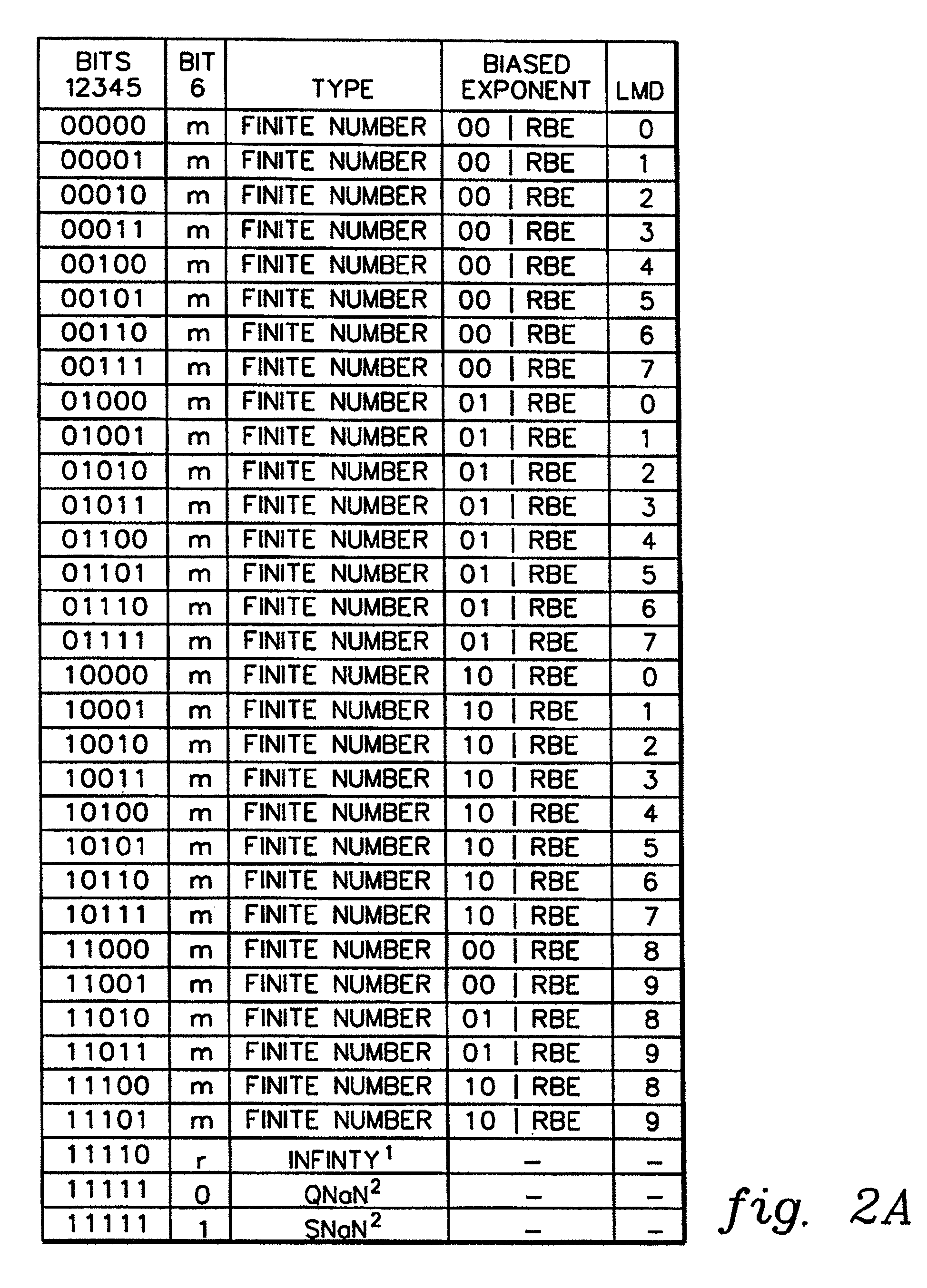

Insert/extract biased exponent of decimal floating point data

InactiveUS20080270495A1Digital computer detailsSpecific program execution arrangementsParallel computingSialic acid synthase

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format. For composition and decomposition, one or more instructions may be employed, including an insert biased exponent or extract biased exponent instruction.

Owner:IBM CORP

Extract biased exponent of decimal floating point data

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format. For composition and decomposition, one or more instructions may be employed, including an insert biased exponent or extract biased exponent instruction.

Owner:IBM CORP

Employing a mask field of an instruction to encode a sign of a result of the instruction

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format. For composition and decomposition, one or more instructions may be employed, including one or more convert instructions.

Owner:INT BUSINESS MASCH CORP

Decomposition of decimal floating point data, and methods therefor

ActiveUS20080270507A1Computations using contact-making devicesCode conversionDecompositionParallel computing

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format.

Owner:IBM CORP

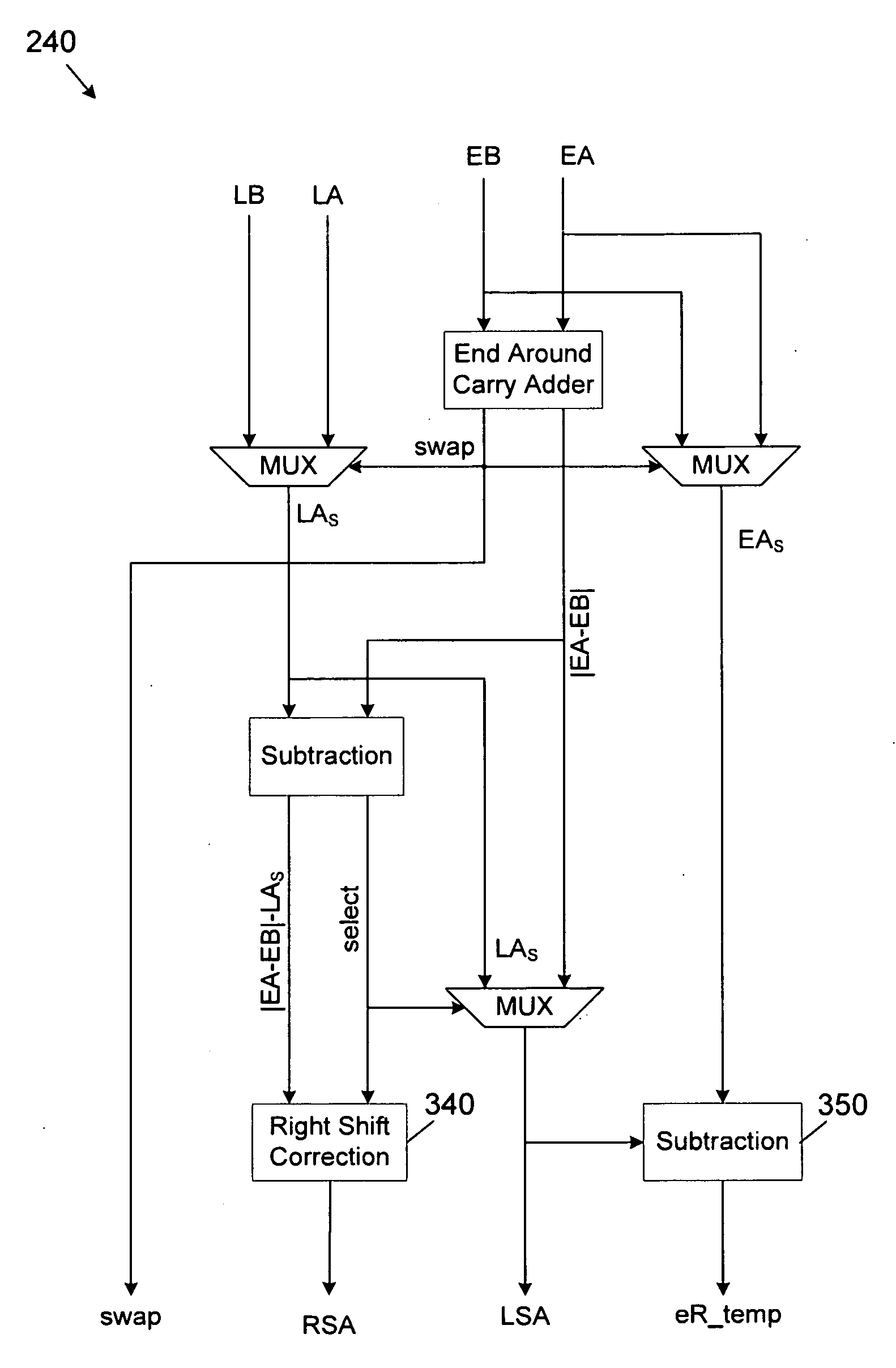

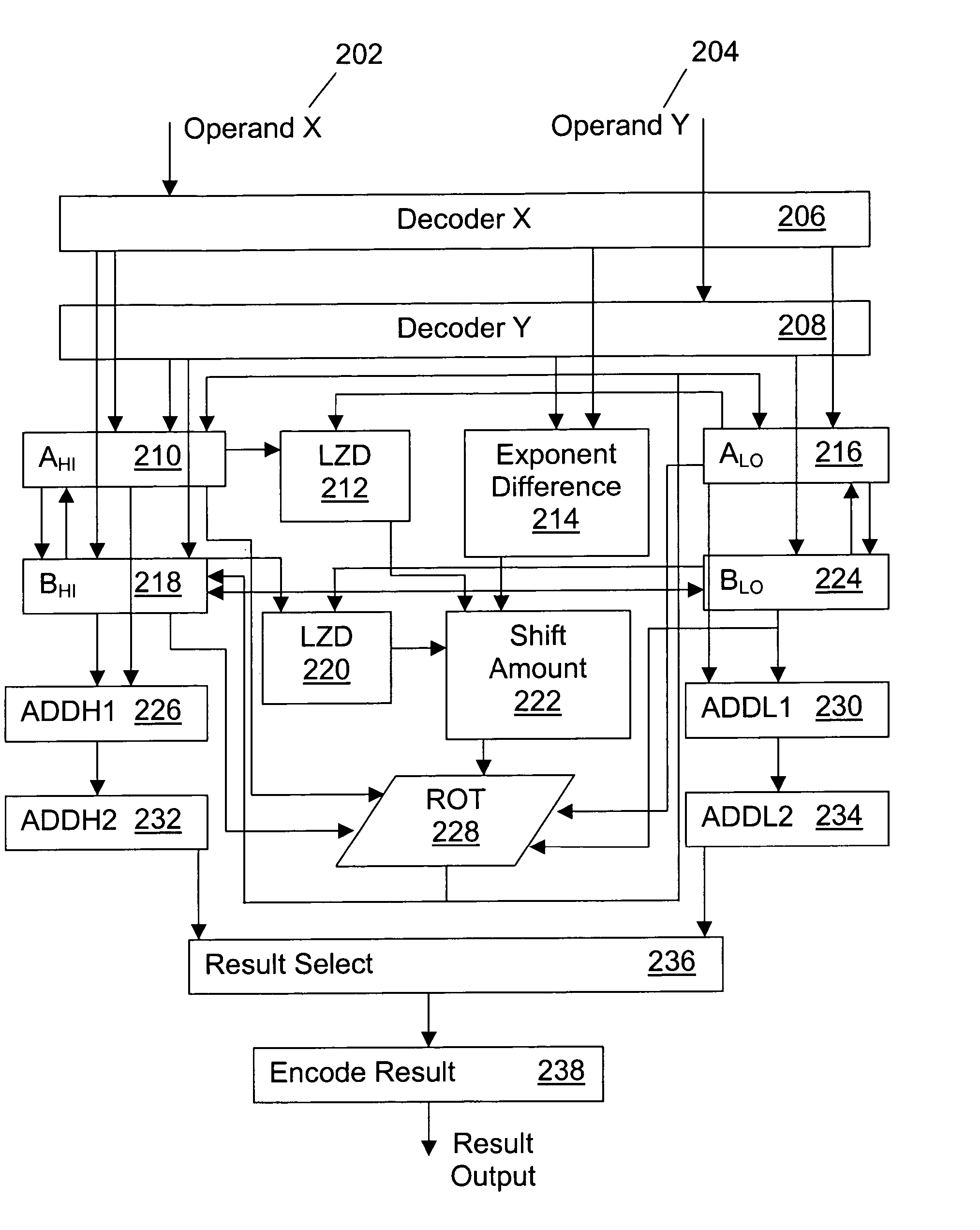

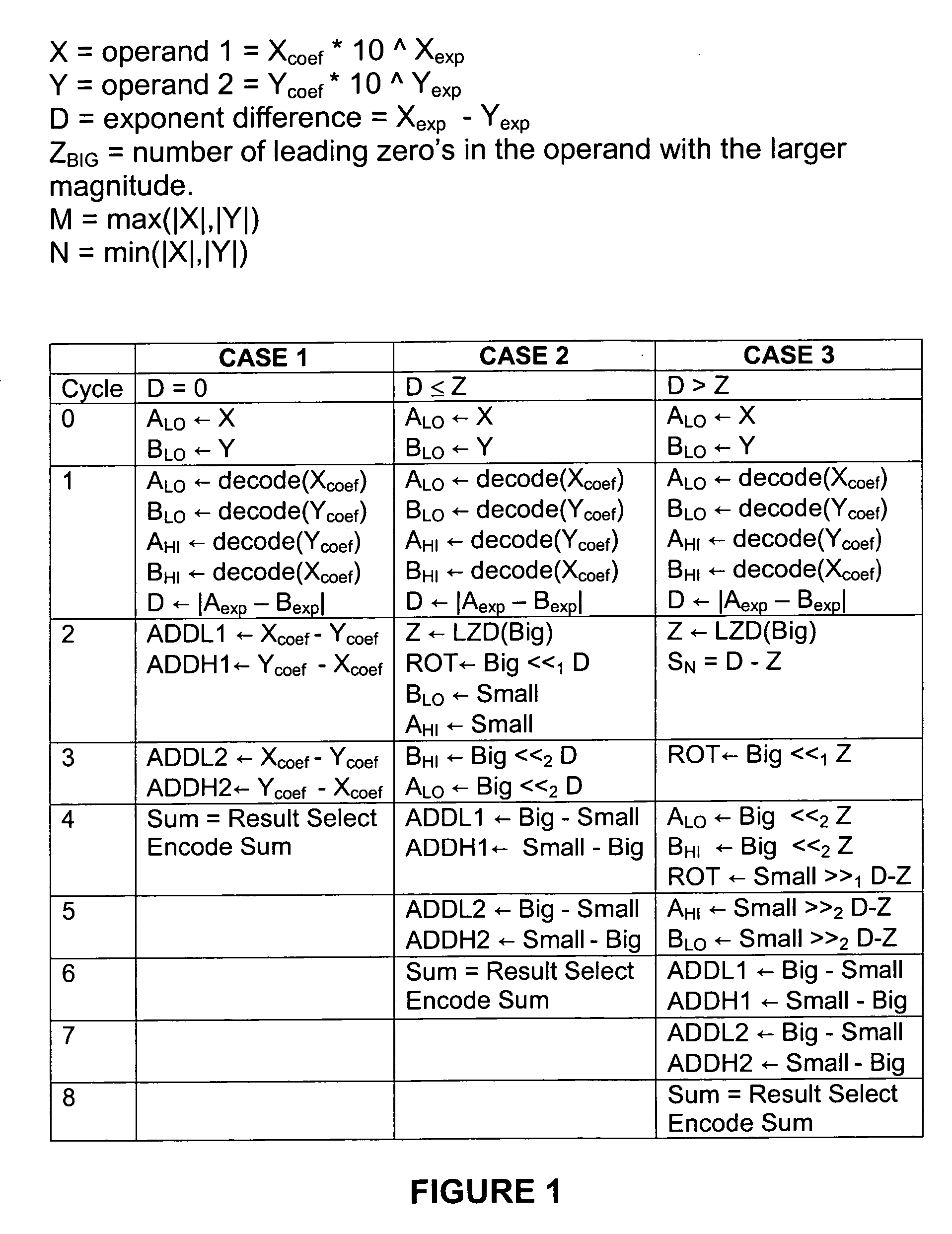

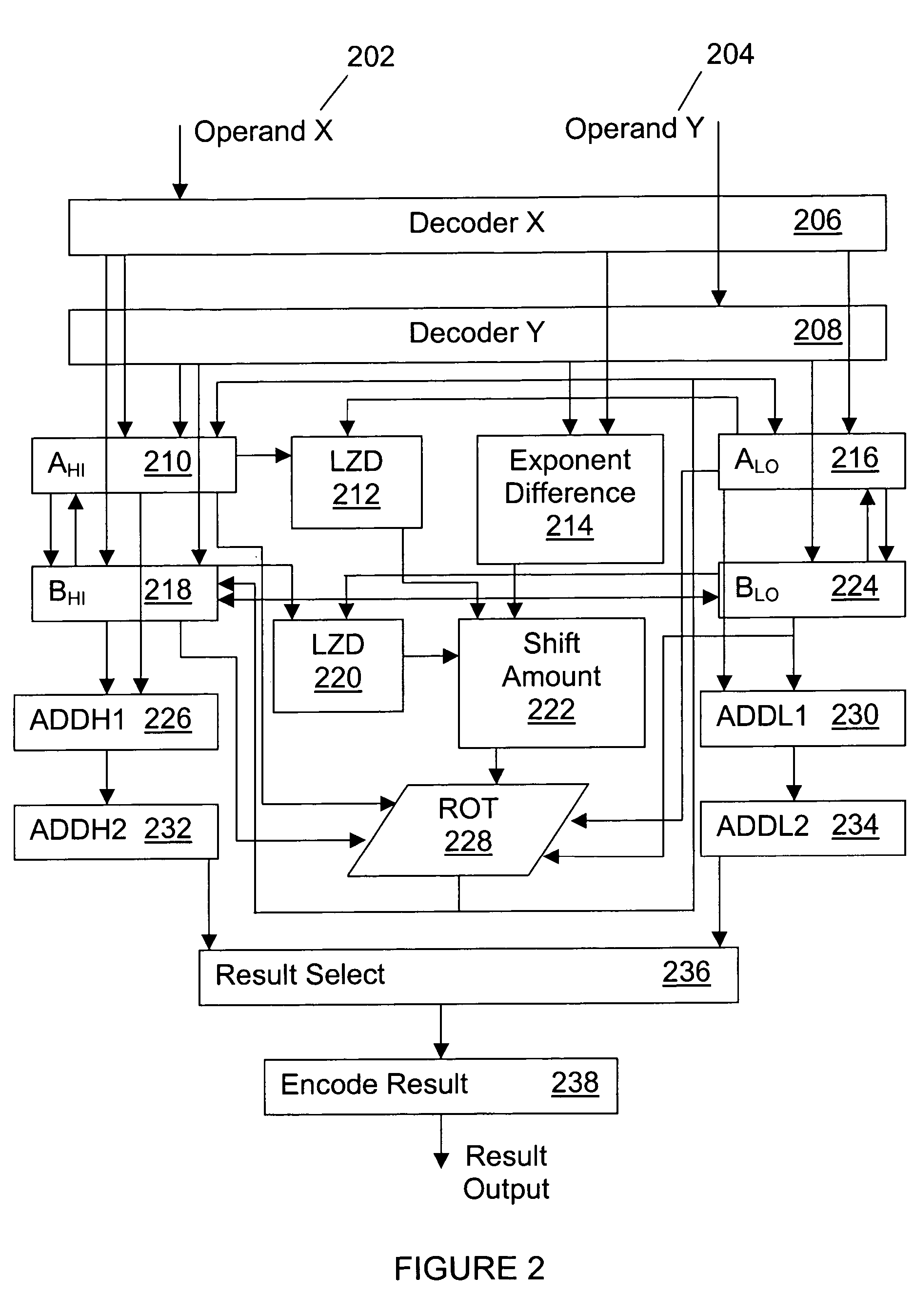

Decimal Floating-Point Adder with Leading Zero Anticipation

ActiveUS20100312812A1Computations using contact-making devicesDigital computer detailsOperandLeading zero

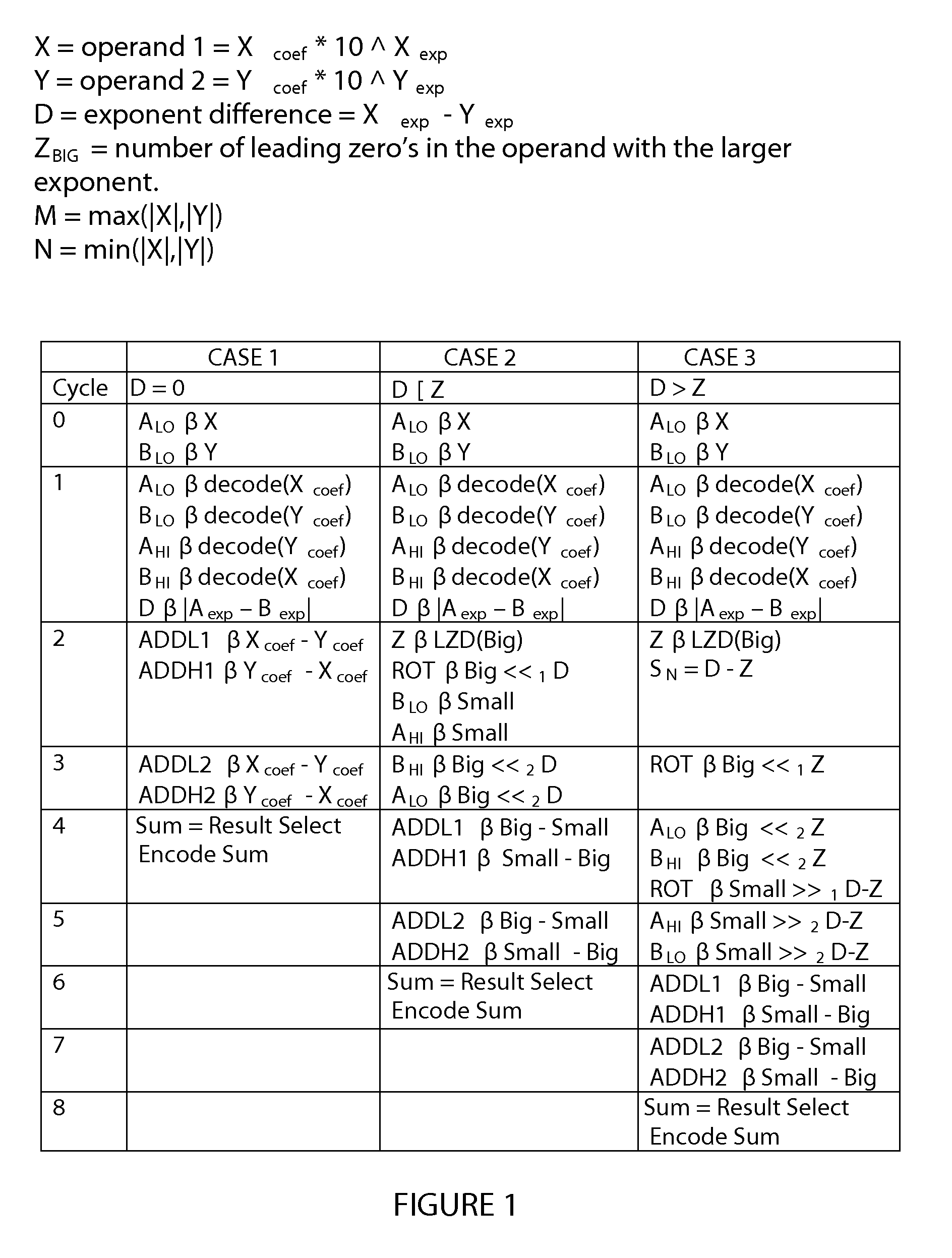

A decimal floating-point (DFP) adder includes a decimal leading-zero anticipator (LZA). The DFP adder receives DFP operands. Each operand includes a significand, an exponent, a sign bit and a leading zero count for the significand. The DFP adder adds or subtracts the DFP operands to obtain a DFP result. The LZA determines the leading zero count associated with the significand of the DFP result. The LZA operates at least partially in parallel with circuitry (in the DFP adder) that computes the DFP result. The LZA does not wait for that circuitry to finish computation of the DFP result. Instead it “anticipates” the number of leading zeros that the result's significand will contain.

Owner:ADVANCED MICRO DEVICES INC

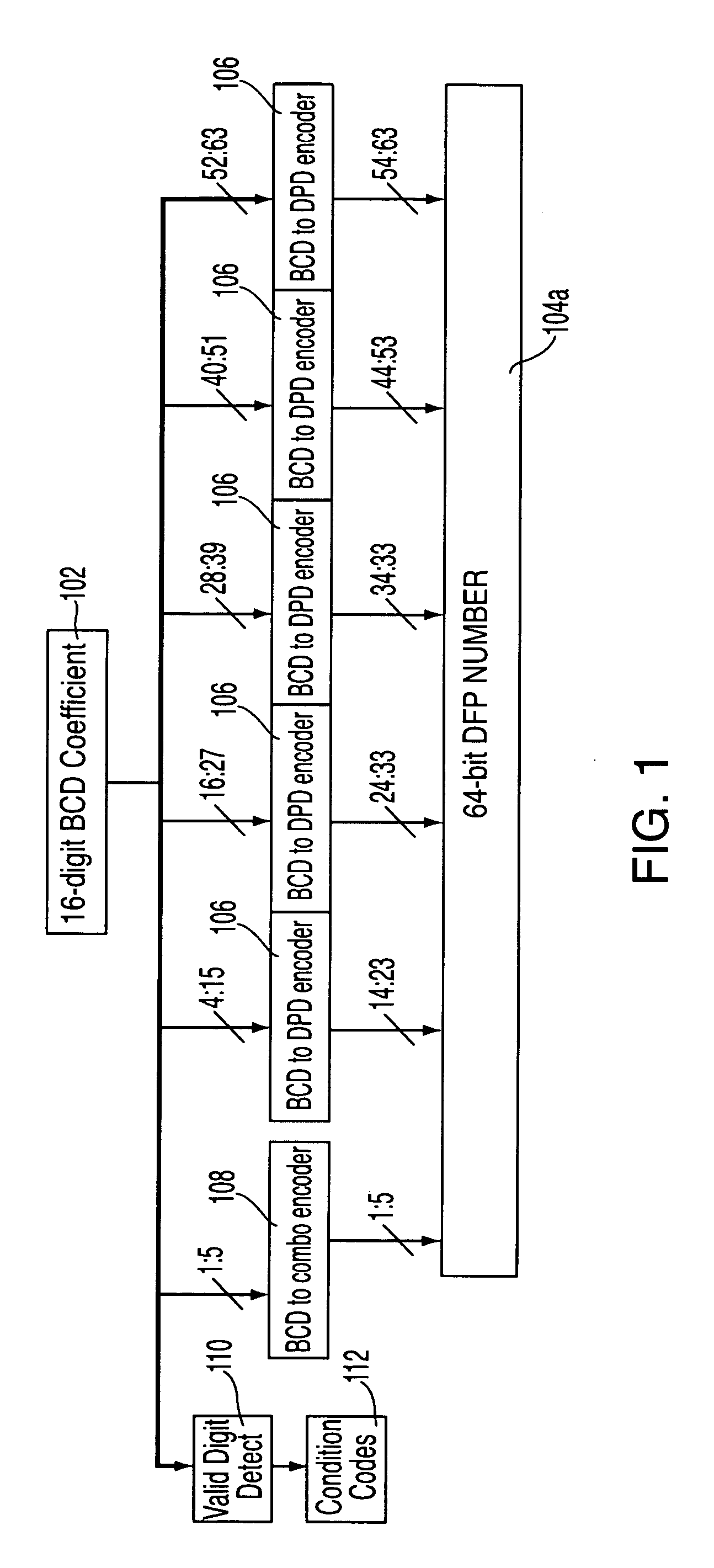

Composition of decimal floating point data

ActiveUS8051118B2Code conversionDigital computer detailsDecimal128 floating-point formatParallel computing

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format.

Owner:INT BUSINESS MASCH CORP

Composition of decimal floating point data, and methods therefor

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format.

Owner:IBM CORP

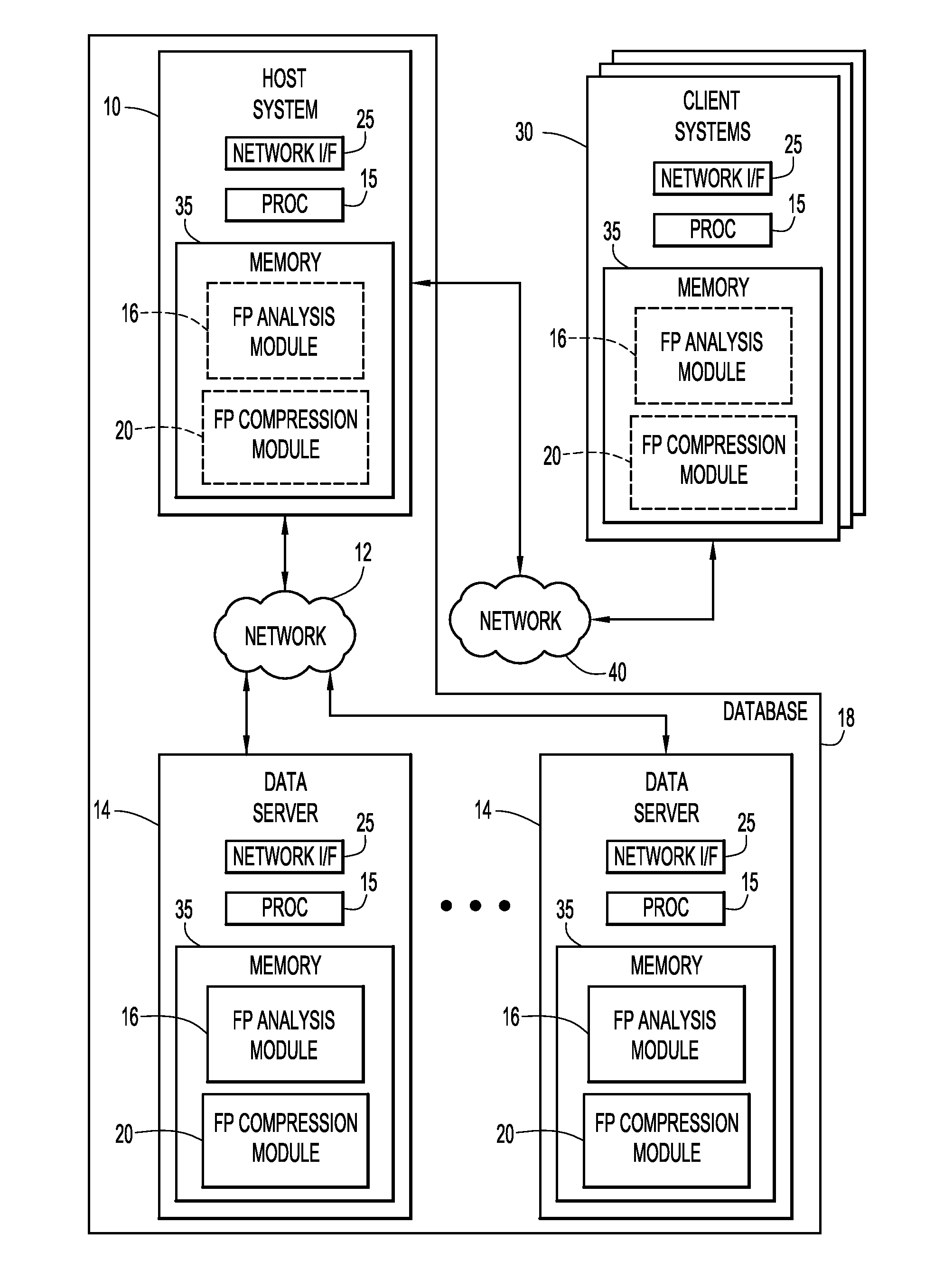

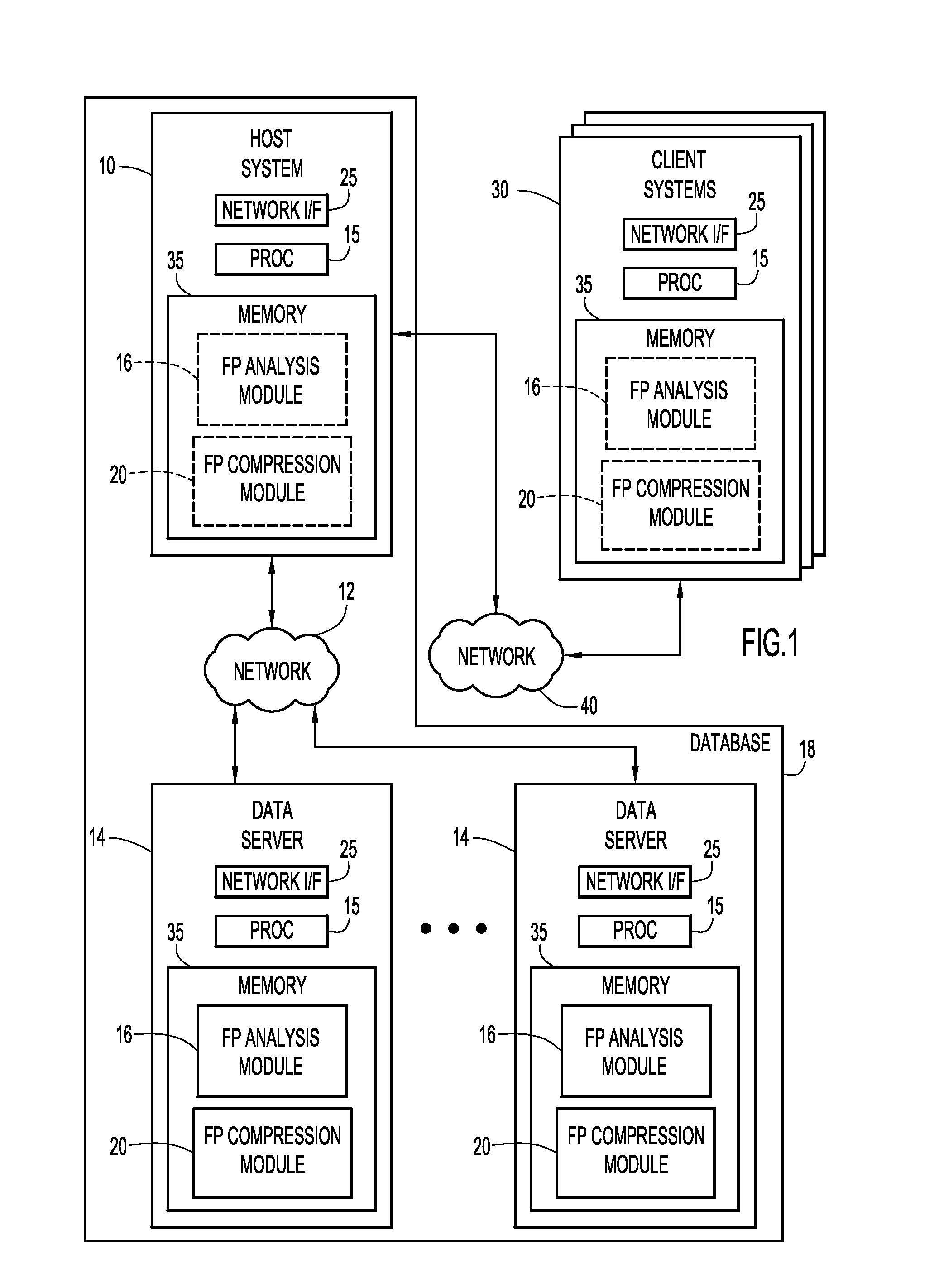

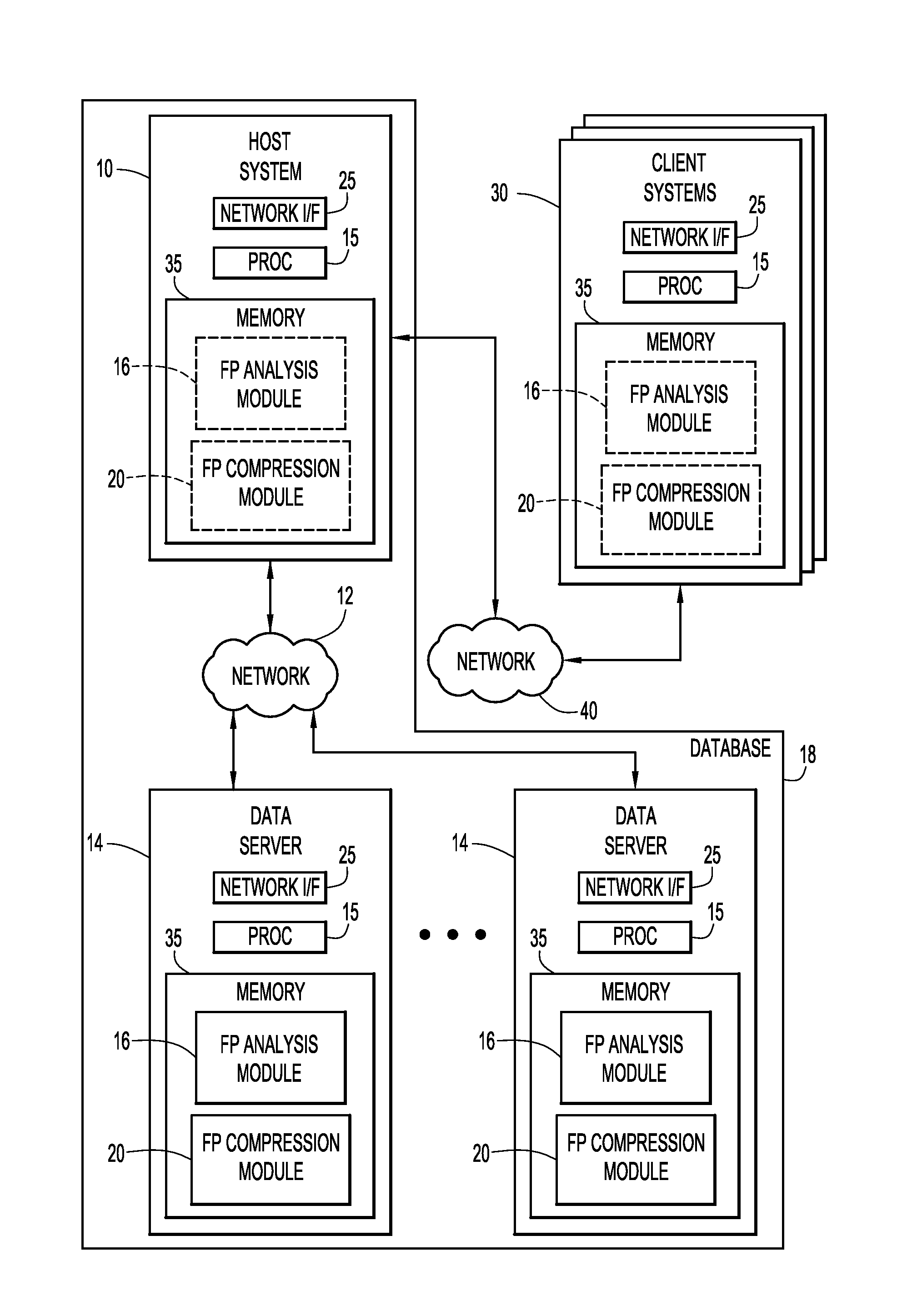

Compression of floating-point data by identifying a previous loss of precision

ActiveUS20150288381A1Digital data processing detailsDigital computer detailsFloating pointData mining

Owner:IBM CORP

Decomposition of decimal floating point data

ActiveUS20080270499A1Digital data processing detailsDigital computer detailsParallel computingSialic acid synthase

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format.

Owner:IBM CORP

Decomposition of decimal floating point data

ActiveUS8051119B2Digital data processing detailsCode conversionDecimal128 floating-point formatParallel computing

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format.

Owner:IBM CORP

Compression of floating-point data by identifying a previous loss of precision

InactiveUS20150286465A1Digital data processing detailsDigital computer detailsFloating pointData mining

Owner:IBM CORP

Convert significand of decimal floating point data to packed decimal format

A decimal floating point finite number in a decimal floating point format is composed from the number in a different format. A decimal floating point format includes fields to hold information relating to the sign, exponent and significand of the decimal floating point finite number. Other decimal floating point data, including infinities and NaNs (not a number), are also composed. Decimal floating point data are also decomposed from the decimal floating point format to a different format. For composition and decomposition, one or more instructions may be employed, including one or more convert instructions.

Owner:IBM CORP

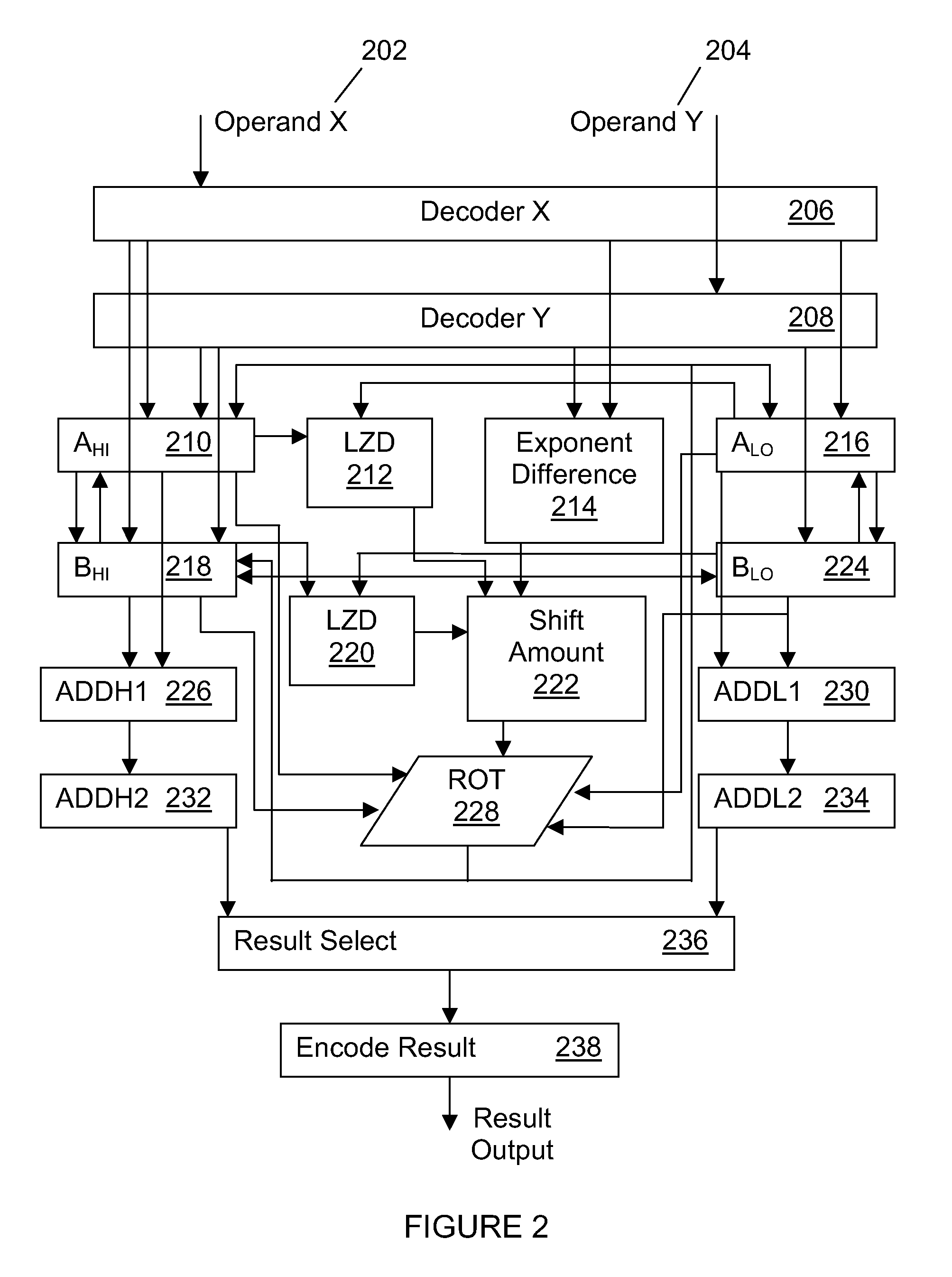

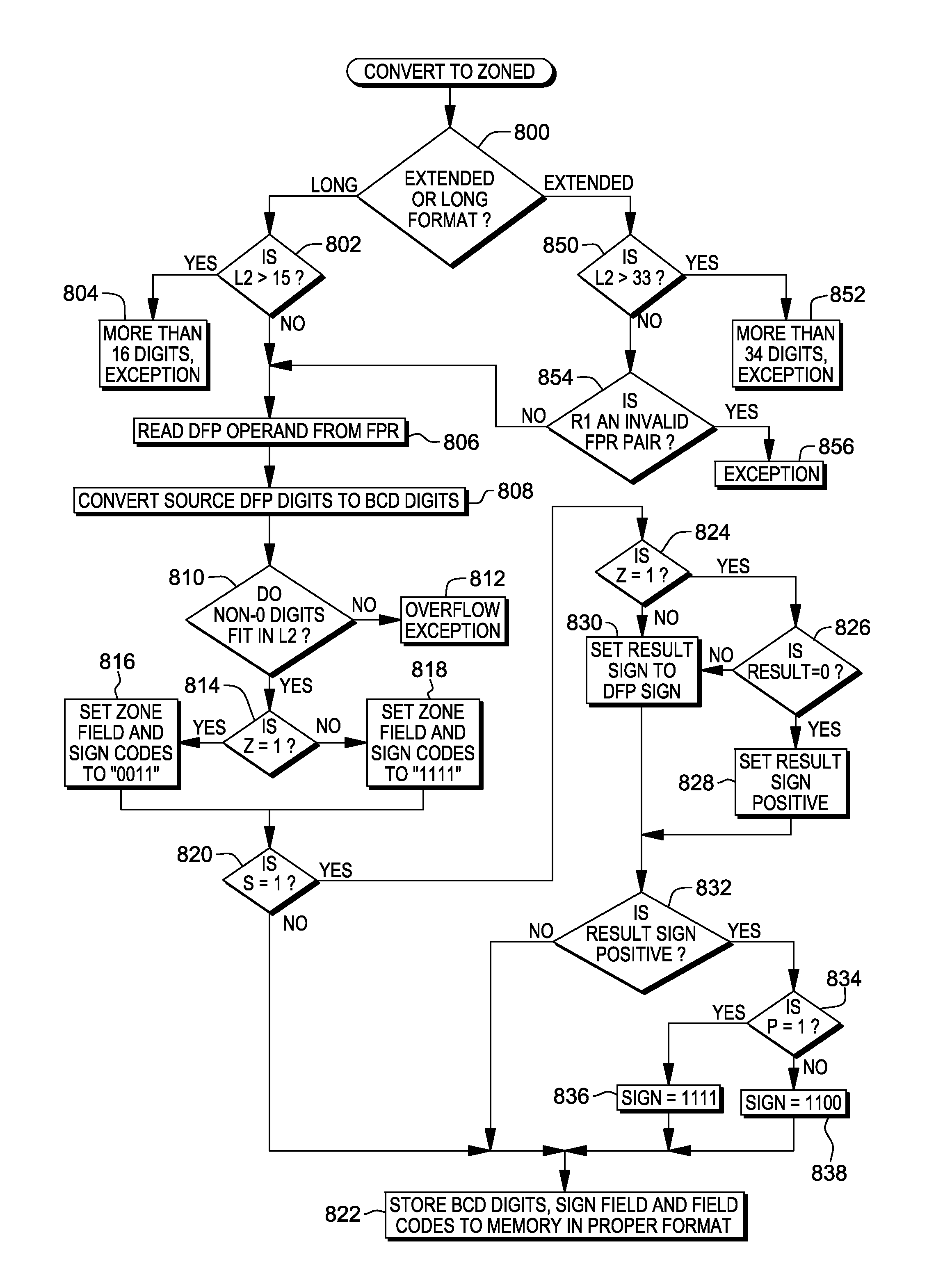

Convert from zoned format to decimal floating point format

Machine instructions, referred to herein as a long Convert from Zoned instruction (CDZT) and extended Convert from Zoned instruction (CXZT), are provided that read EBCDIC or ASCII data from memory, convert it to the appropriate decimal floating point format, and write it to a target floating point register or floating point register pair. Further, machine instructions, referred to herein as a long Convert to Zoned instruction (CZDT) and extended Convert to Zoned instruction (CZXT), are provided that convert a decimal floating point (DFP) operand in a source floating point register or floating point register pair to EBCDIC or ASCII data and store it to a target memory location.

Owner:IBM CORP

System and method for performing decimal floating point addition

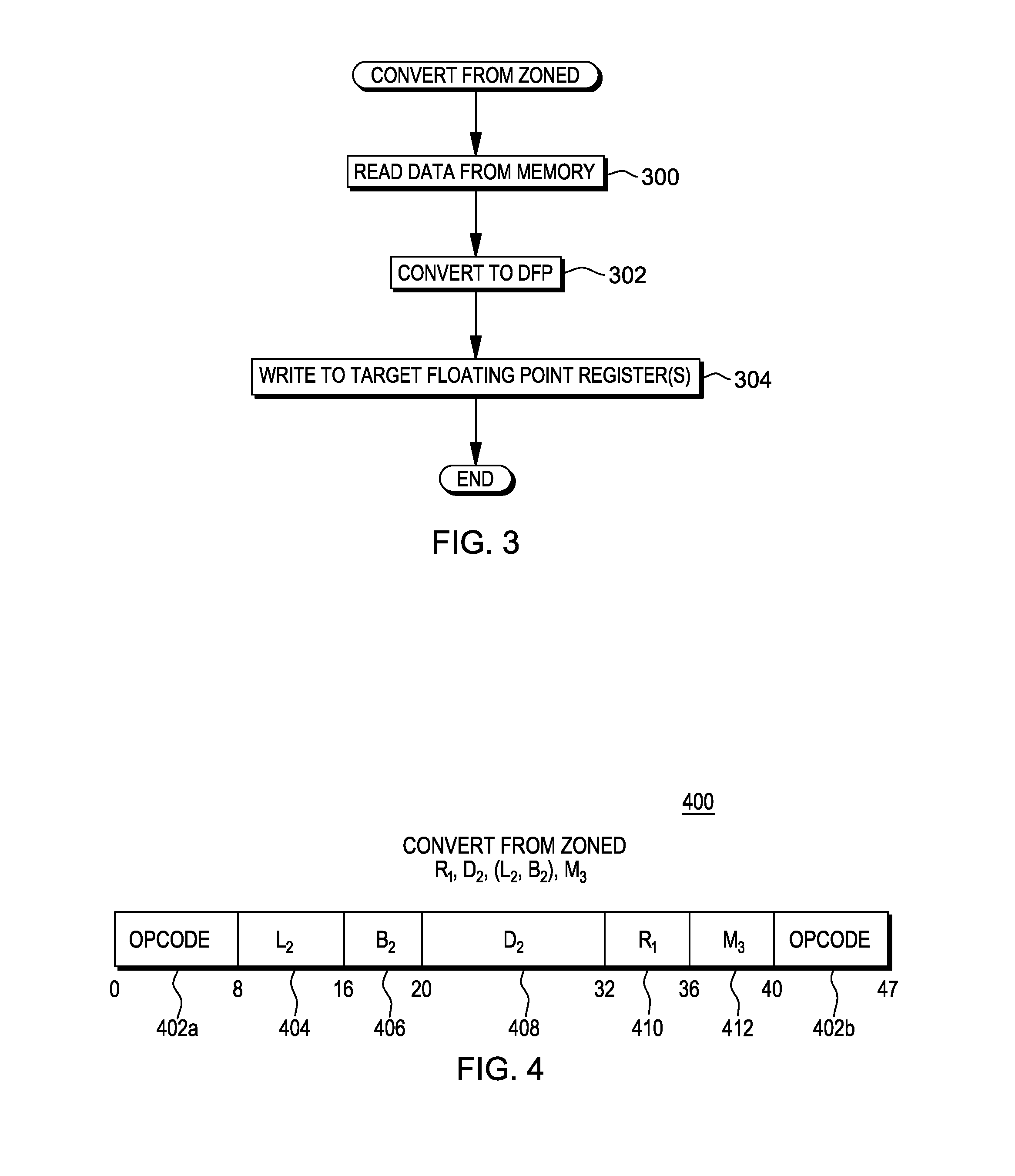

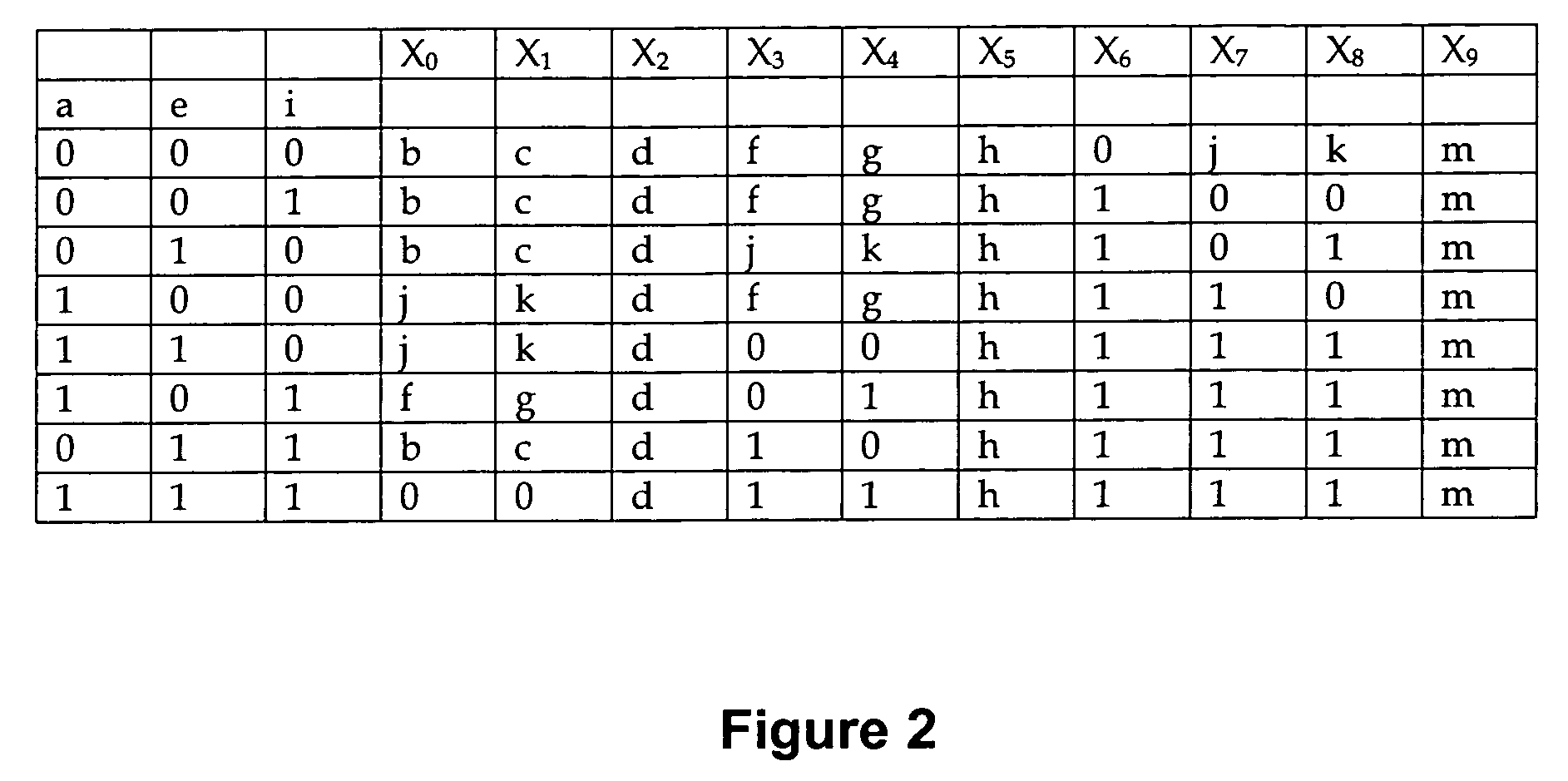

A method for performing a decimal floating point operation. A first operand including a first coefficient and a first exponent is received. The method also includes receiving a second operand that includes a second coefficient and a second exponent. An operation associated with the first operand and the second operand is received. The operation is an addition or a subtraction. Three concurrent calculations are performed on the first operand and the second operand. The first concurrent calculation includes applying the operation to the first operand and the second operand based on a first assumption that the first exponent is equal to the second exponent. The applying the operation based on the first assumption results in a first result and includes utilizing a two cycle adder. The second concurrent calculation includes applying the operation to the first operand and the second operand based on a second assumption that an absolute difference between the first exponent and the second exponent is less than or equal to a number of leading zeros in the coefficient of the operand with the larger exponent. The applying the operation based on the second assumption results in a second result and includes utilizing the two cycle adder. The third concurrent calculation includes applying the operation to the first operand and the second operand based on a third assumption that the absolute difference between the first exponent and the second exponent is greater than the number of leading zeros in the coefficient of the operand with the larger exponent. The applying the operation based on the third assumption results in a third result and includes utilizing the two cycle adder. A final result is selected from the first result, the second result and the third result.

Owner:INT BUSINESS MASCH CORP

Convert to zoned format from decimal floating point format

ActiveUS20130173892A1None provides advantagesRegister arrangementsDigital computer detailsProcessor registerOperand

Machine instructions, referred to herein as a long Convert from Zoned instruction (CDZT) and extended Convert from Zoned instruction (CXZT), are provided that read EBCDIC or ASCII data from memory, convert it to the appropriate decimal floating point format, and write it to a target floating point register or floating point register pair. Further, machine instructions, referred to herein as a long Convert to Zoned instruction (CZDT) and extended Convert to Zoned instruction (CZXT), are provided that convert a decimal floating point (DFP) operand in a source floating point register or floating point register pair to EBCDIC or ASCII data and store it to a target memory location.

Owner:IBM CORP

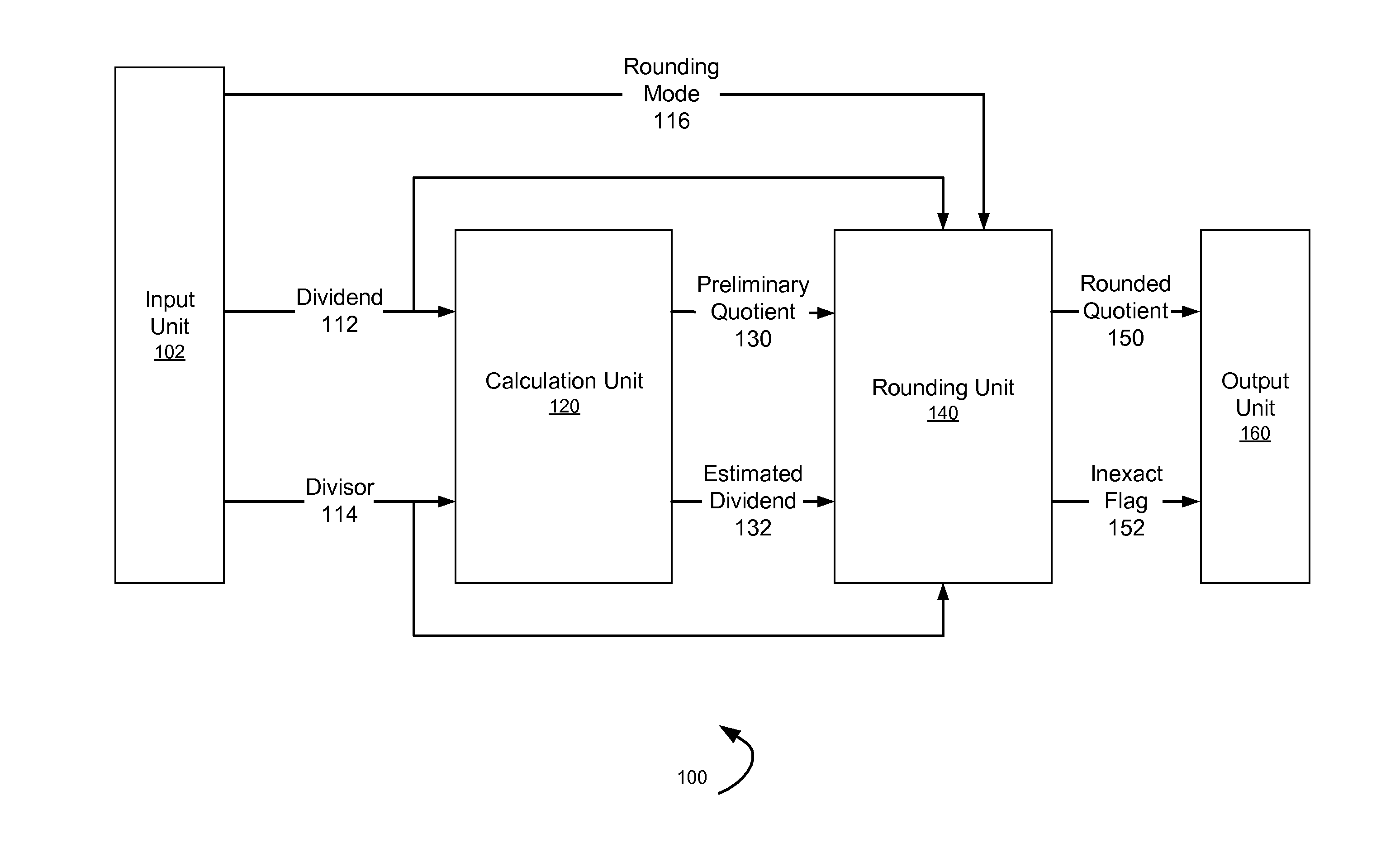

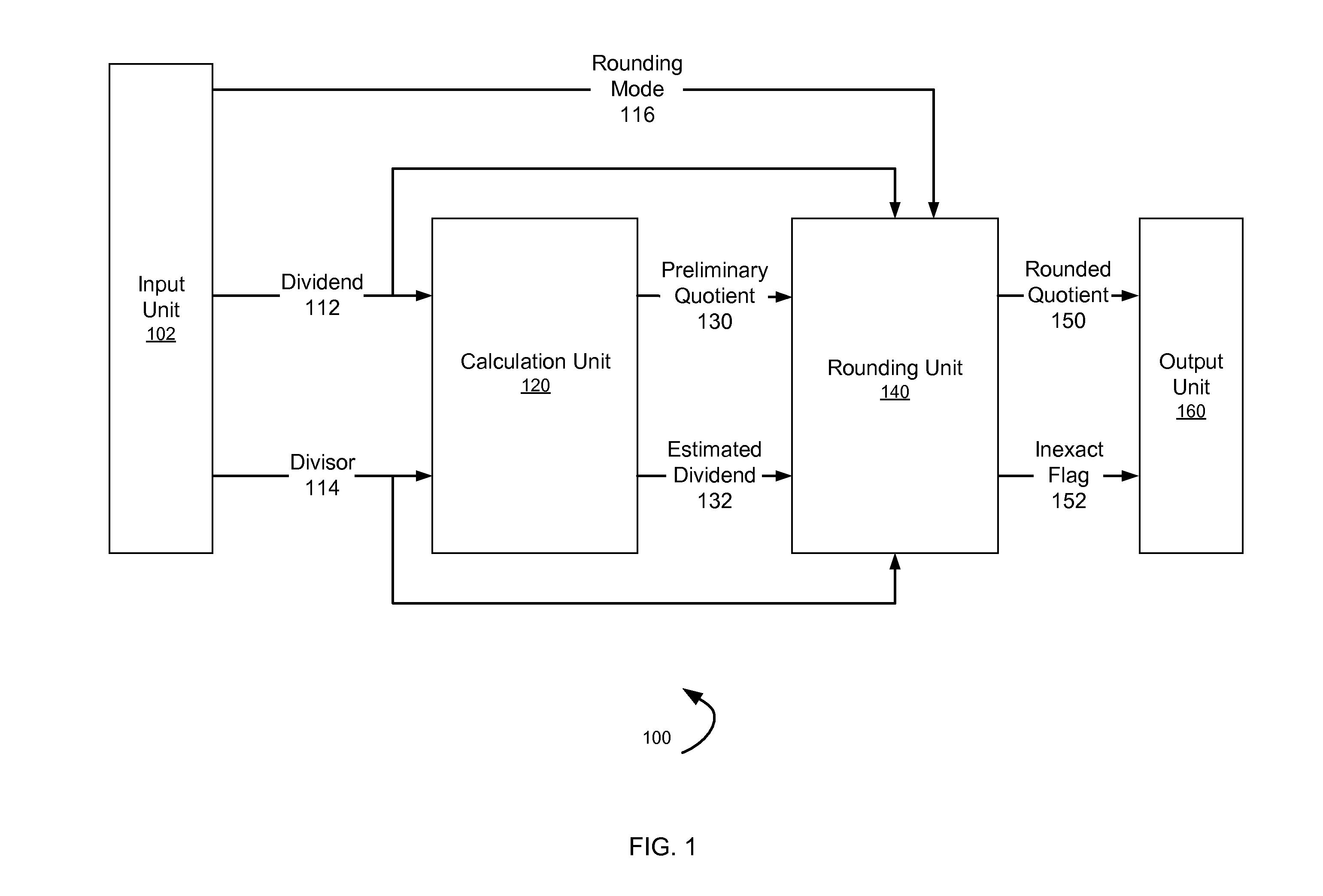

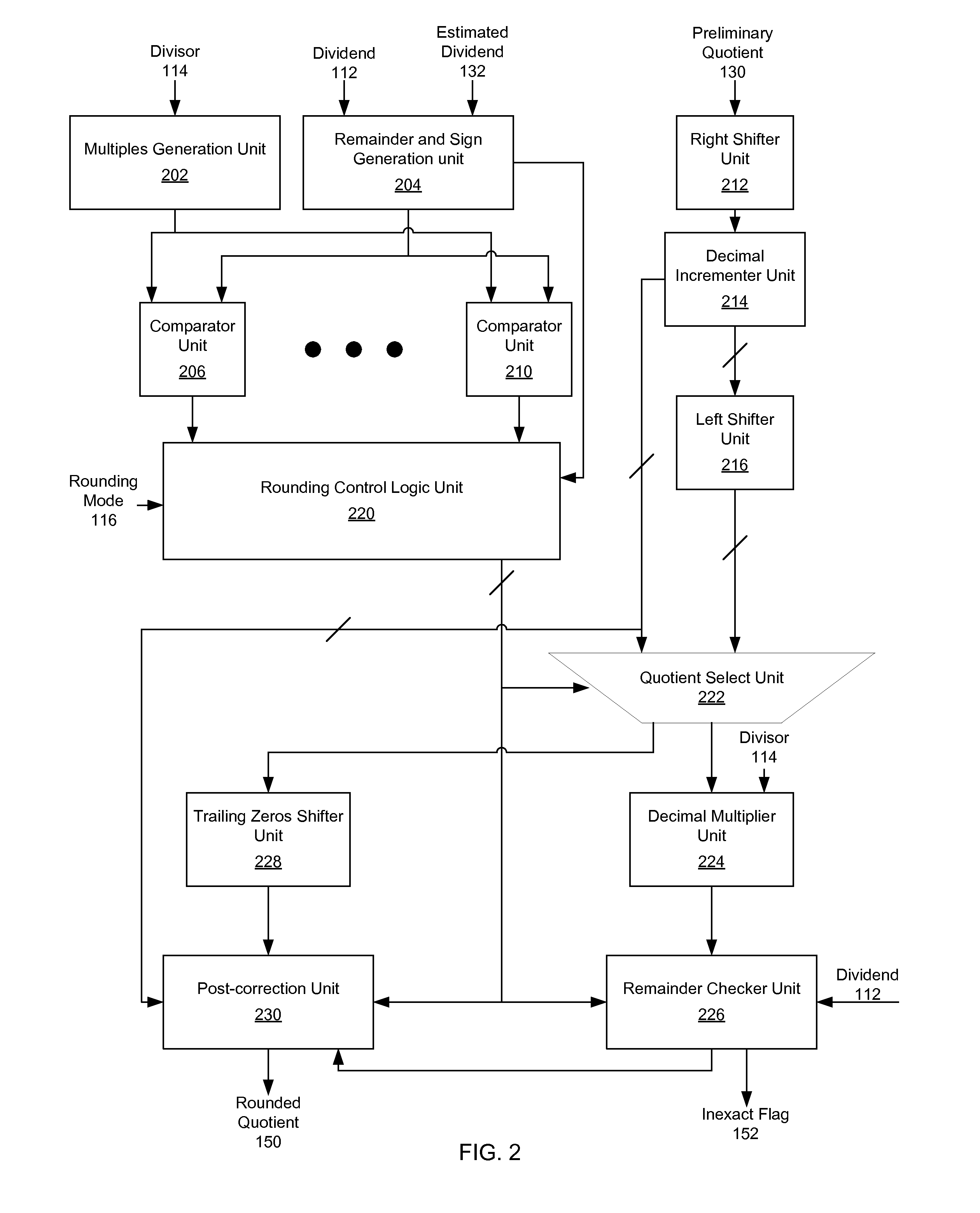

Rounding unit for decimal floating-point division

InactiveUS20120011185A1Computation using denominational number representationFloating pointComputer science

A method for performing a decimal floating-point division, including: receiving, by a decimal floating-point divider, a decimal floating-point dividend and a decimal floating-point divisor; obtaining, by the decimal floating-point divider, a preliminary quotient having a first precision level, where the preliminary quotient is calculated from the decimal floating-point dividend and the decimal-floating point divisor; receiving, by the decimal floating-point divider, a rounding mode; selecting a rounding action based on the preliminary quotient and the rounding mode; and obtaining a rounded quotient having a second precision level by rounding the preliminary quotient according to the rounding action, where the first precision level is at least one digit greater than the second precision level.

Owner:SILMINDS

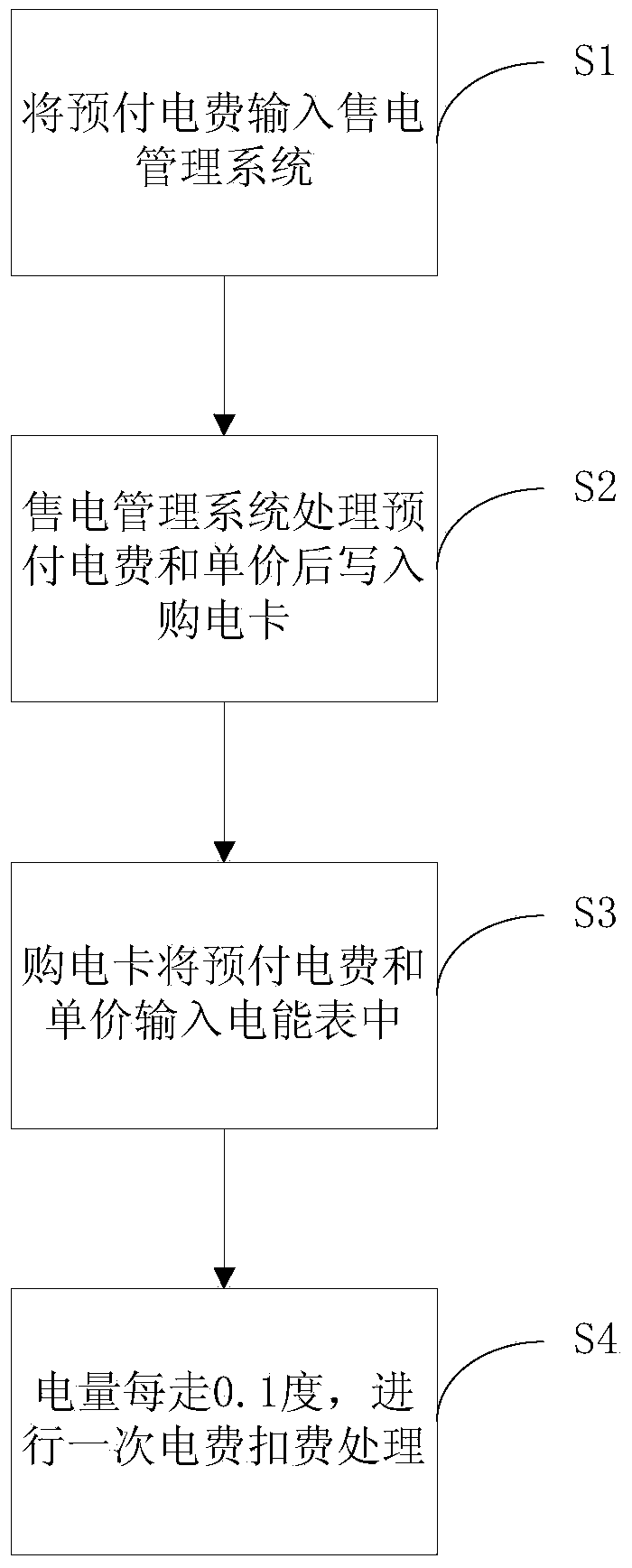

Charge-control processing method of electric power meter for prepayment

ActiveCN104299323ALighten the computational burdenImprove the display effectApparatus for hiring articlesElectricityElectric power system

The invention discloses a charge-control processing method of an electric power meter and relates to the field of charging with the electric power meter. The charge-control processing method includes that firstly, prepaid electricity is inputted into an electricity selling management system; the electricity selling management system magnifies the prepaid electricity to be 10N+1 times and converts the prepaid electricity into a hexadecimal value and magnifies unit price to be 1-N times and converts the unit price into a hexadecimal value; secondly, the converted prepaid electricity and unit price are inputted into the electric power meter storing total electricity and the unit price which are hexadecimal; electricity deduction processing is performed by the electric power meter each time 0.1-degree electric quantity is consumed according to the formula: remaining electricity=remaining electricity before deduction-unit price, and the hexadecimal remaining electricity and unit price are stored in the electric power meter. Multiply operation of decimal floating points in electricity deduction is simplified to be hexadecimal addition and subtraction calculation operation, and burden of the electric power meter is reduced.

Owner:武汉阿迪克电子股份有限公司

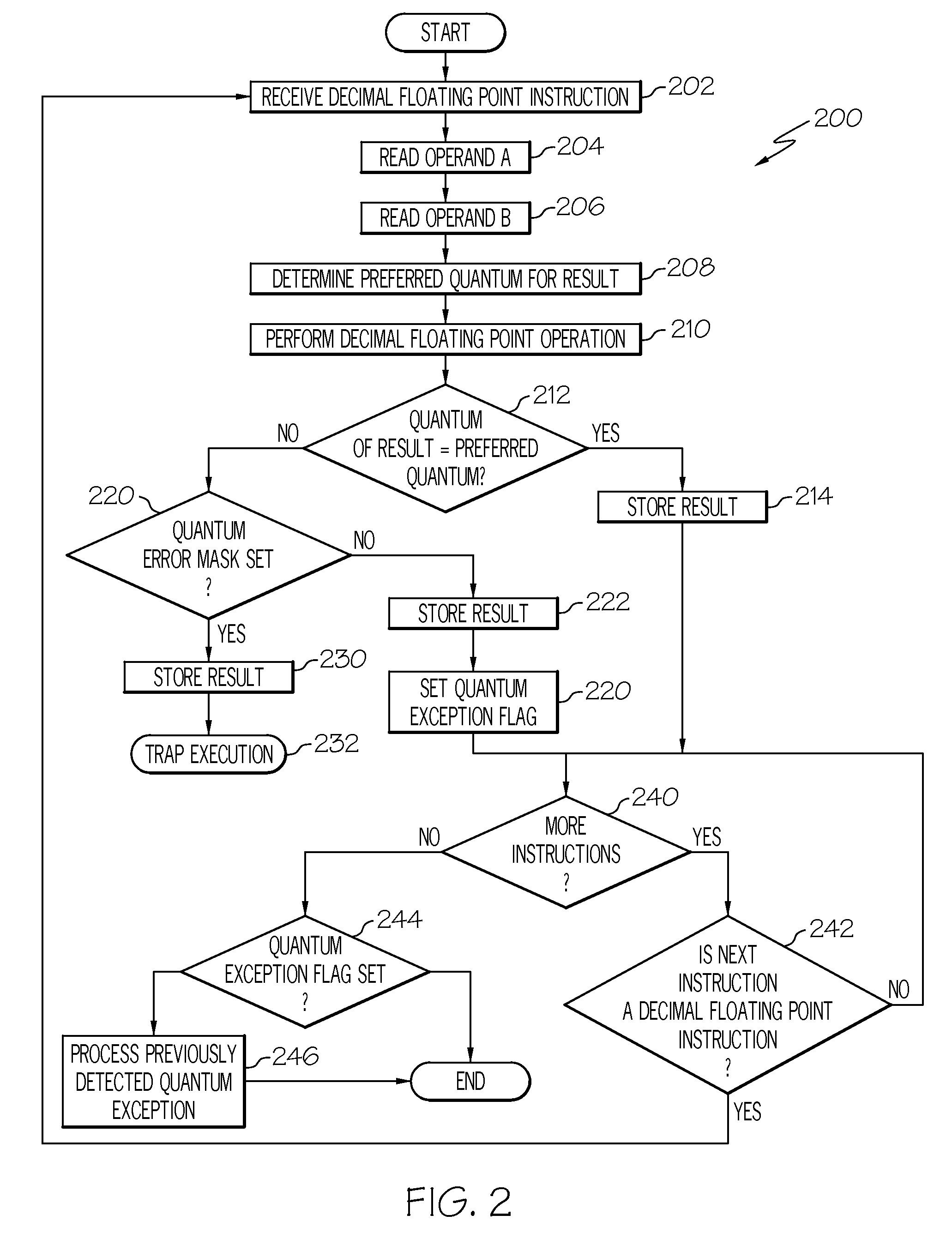

Decimal floating-pointing quantum exception detection

ActiveUS8219605B2Conditional code generationError detection/correctionAnomaly detectionLeast significant bit

A system and method for detecting decimal floating point data processing exceptions. A processor accepts at least one decimal floating point operand and performs a decimal floating point operation on the at least one decimal floating point operand to produce a decimal floating point result. A determination is made as to whether the decimal floating point result fails to maintain a preferred quantum. The preferred quantum indicates a value represented by a least significant digit of a significand of the decimal floating point result. An output is provided, in response to the determining that the decimal floating point result fails to maintain the preferred quantum, indicating an occurrence of a quantum exception. A maskable exception can be generated that is immediately trapped or later detected to control conditional processing.

Owner:IBM CORP

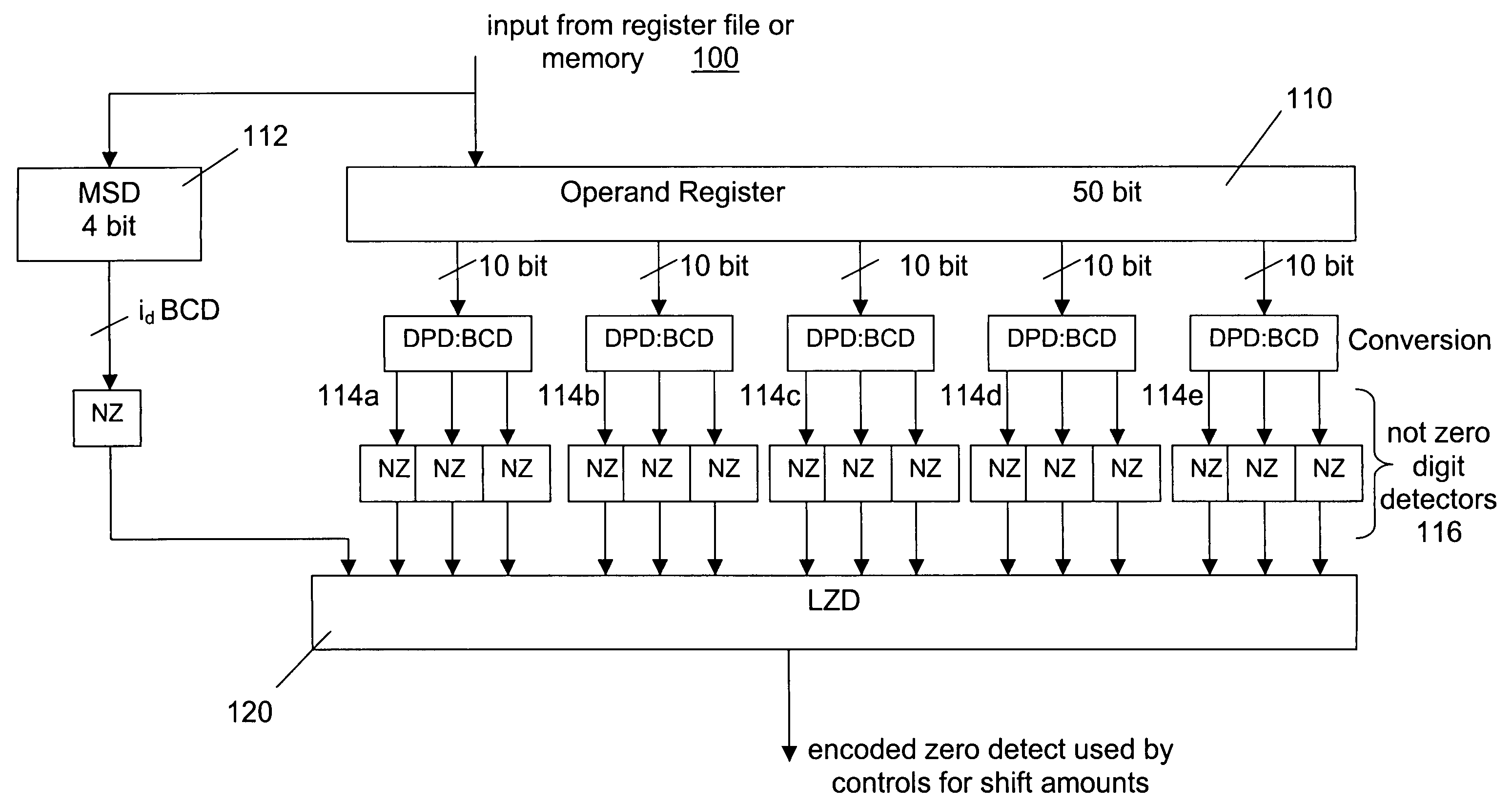

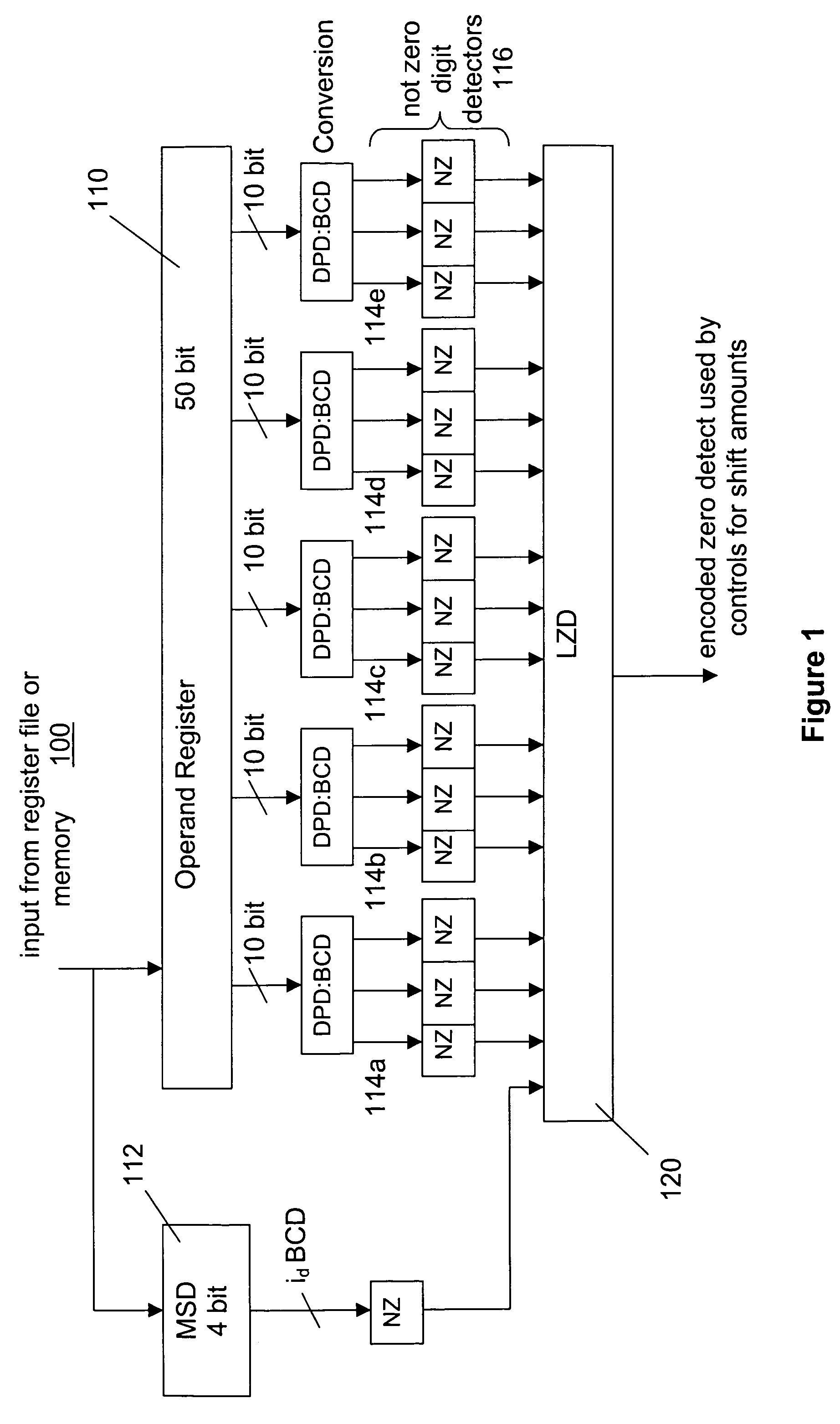

System and method for reduction of leading zero detect for decimal floating point numbers

InactiveUS20060179098A1Easy to receiveComputation using denominational number representationFloating pointLeading zero

A method for leading zero detection. The method includes receiving DPD encoded data representing a three digit BCD number and determining directly from the DPD encoded data if the BCD number represented by the DPD encoded data contains at least one leading zero digit. A group one switch is set to zero if it was determined that the BCD number represented by the DPD encoded data contains at least one leading zero digit and set to one otherwise. The method also includes determining directly from the DPD encoded data if the BCD number represented by the DPD encoded data contains at least two leading zero digits. A group two switch is set to zero if it was determined that the BCD number represented by the DPD encoded data contains at least two leading zero digits and set to one otherwise. The method further includes determining directly from the DPD encoded data if the BCD number represented by the DPD encoded data contains three leading zero digits. A group three switch is set to zero if was determined that the BCD number represented by the DPD encoded data contains three leading zero digits and set to one otherwise.

Owner:IBM CORP

System and method for performing decimal floating point addition

InactiveUS20060179099A1Computations using contact-making devicesConcurrent computingAbsolute difference

A method for performing a decimal floating point operation. A first operand including a first coefficient and a first exponent is received. The method also includes receiving a second operand that includes a second coefficient and a second exponent. An operation associated with the first operand and the second operand is received. The operation is an addition or a subtraction. Three concurrent calculations are performed on the first operand and the second operand. The first concurrent calculation includes applying the operation to the first operand and the second operand based on a first assumption that the first exponent is equal to the second exponent. The applying the operation based on the first assumption results in a first result and includes utilizing a two cycle adder. The second concurrent calculation includes applying the operation to the first operand and the second operand based on a second assumption that an absolute difference between the first exponent and the second exponent is less than or equal to a number of leading zeros in the coefficient of the operand with the larger exponent. The applying the operation based on the second assumption results in a second result and includes utilizing the two cycle adder. The third concurrent calculation includes applying the operation to the first operand and the second operand based on a third assumption that the absolute difference between the first exponent and the second exponent is greater than the number of leading zeros in the coefficient of the operand with the larger exponent. The applying the operation based on the third assumption results in a third result and includes utilizing the two cycle adder. A final result is selected from the first result, the second result and the third result.

Owner:IBM CORP

Compression of floating-point data by identifying a previous loss of precision

Owner:INT BUSINESS MASCH CORP

Order-preserving encoding formats of floating-point decimal numbers for efficient value comparison

ActiveUS7685214B2Fast and direct string comparisonDigital computer detailsRecord information storageFloating pointData type

A method for conversion between a decimal floating-point number and an order-preserving format has been disclosed. The method encodes numbers in the decimal floating-point format into a format which preserves value ordering. This encoding allows for fast and direct string comparison of two values. Such an encoding provides normalized representations for decimal floating-point numbers and supports type-insensitive comparisons. Type-insensitive comparisons are often used in database management systems, where the data type is not specified for values to compare. In addition, the original decimal floating-point format can be recovered from the order-preserving format.

Owner:TWITTER INC

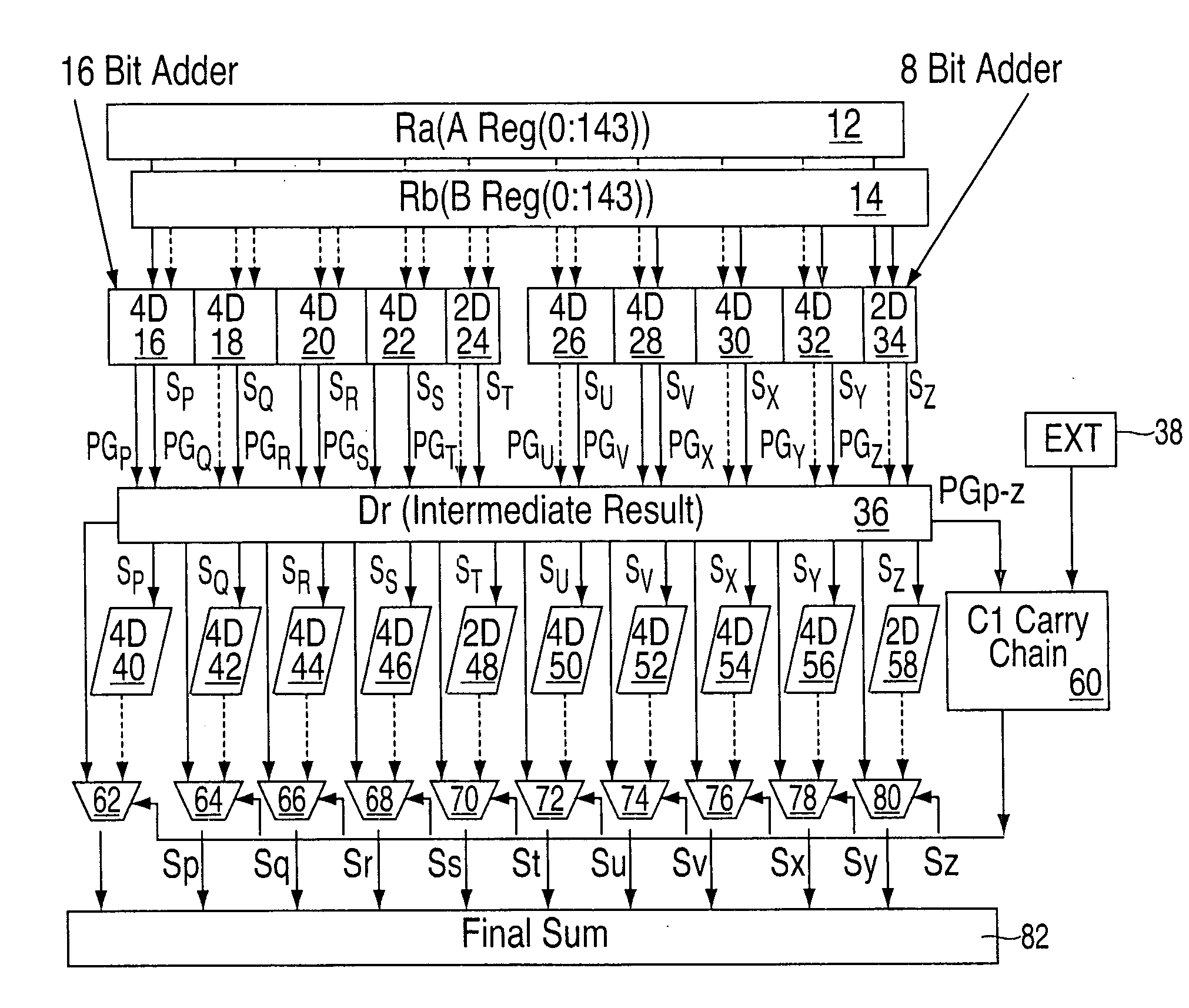

System and method for providing a double adder for decimal floating point operations

InactiveUS20060179103A1Computations using contact-making devicesComputation using non-contact making devicesOperandDecimal floating point

A system for performing decimal floating point addition. The system includes input registers for inputting a first and second operand for an addition operation. The system also includes a plurality of adder blocks, each calculating a sum of one or more corresponding digits from the first operand and the second operand. Output from each of the adder blocks includes the sum of the corresponding digits and a carry out indicator for the corresponding digits. The calculating is performed during a first clock cycle. The system also includes an intermediate result register for storing the sums of the corresponding digits output from each of the plurality of adder blocks, the storing during the first clock cycle. The system further includes a carry chain for storing the carry out indicator output from each of the plurality of adder blocks, the storing occurring during the first clock cycle. The system further includes an incrementer for adding one to each of the sums stored in the intermediate result register, the incrementing occurring during a second clock cycle. In addition, a mechanism is provided for selecting between each of the sums and the sums incremented by one. The input to the mechanism includes the carry chain. The output includes the final sum of the first operand and the second operand. The selecting occurs during the second clock cycle.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com