Method of manufacturing semiconductor device

a manufacturing method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problems of increasing interconnect resistance, increasing the burden on the plating step, and low uniformity of the coverage of the conductive layer, so as to suppress the burden on the plating step, and suppress the sheet resistance of the plating seed layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

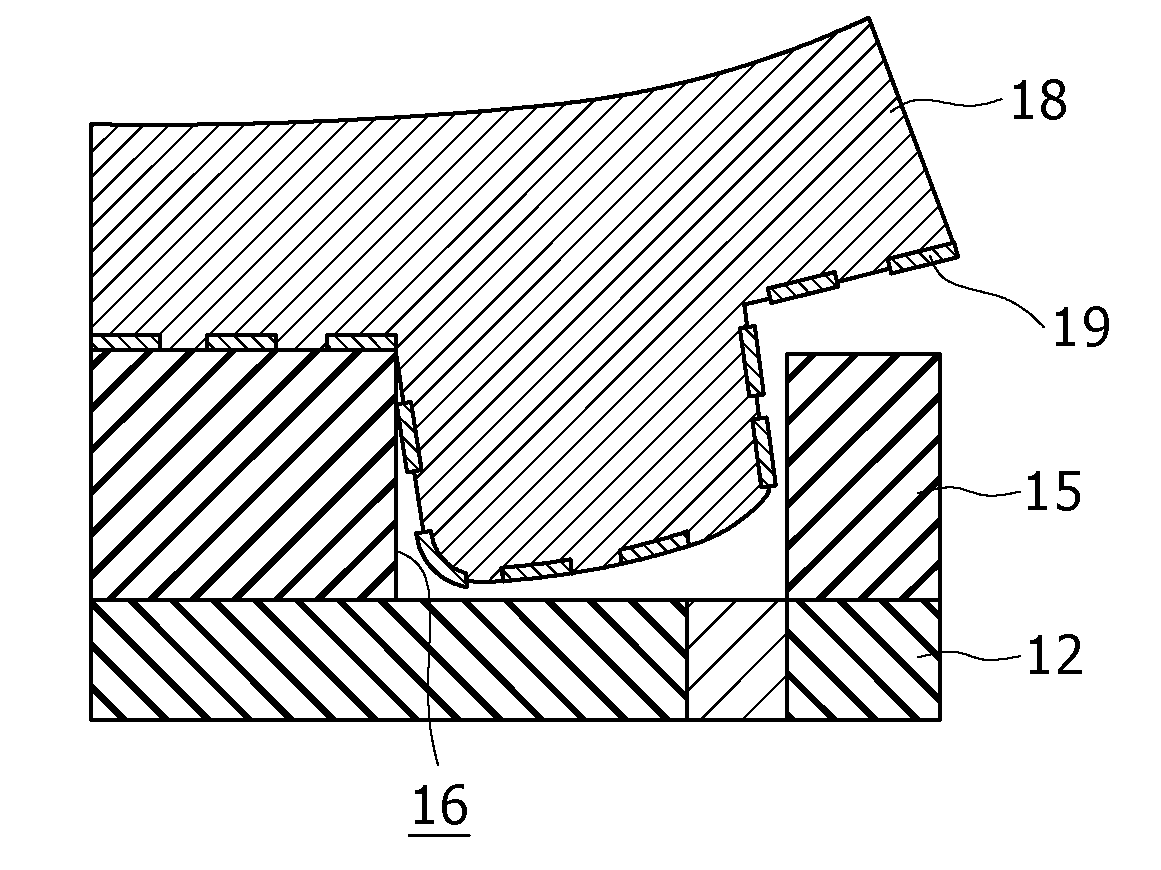

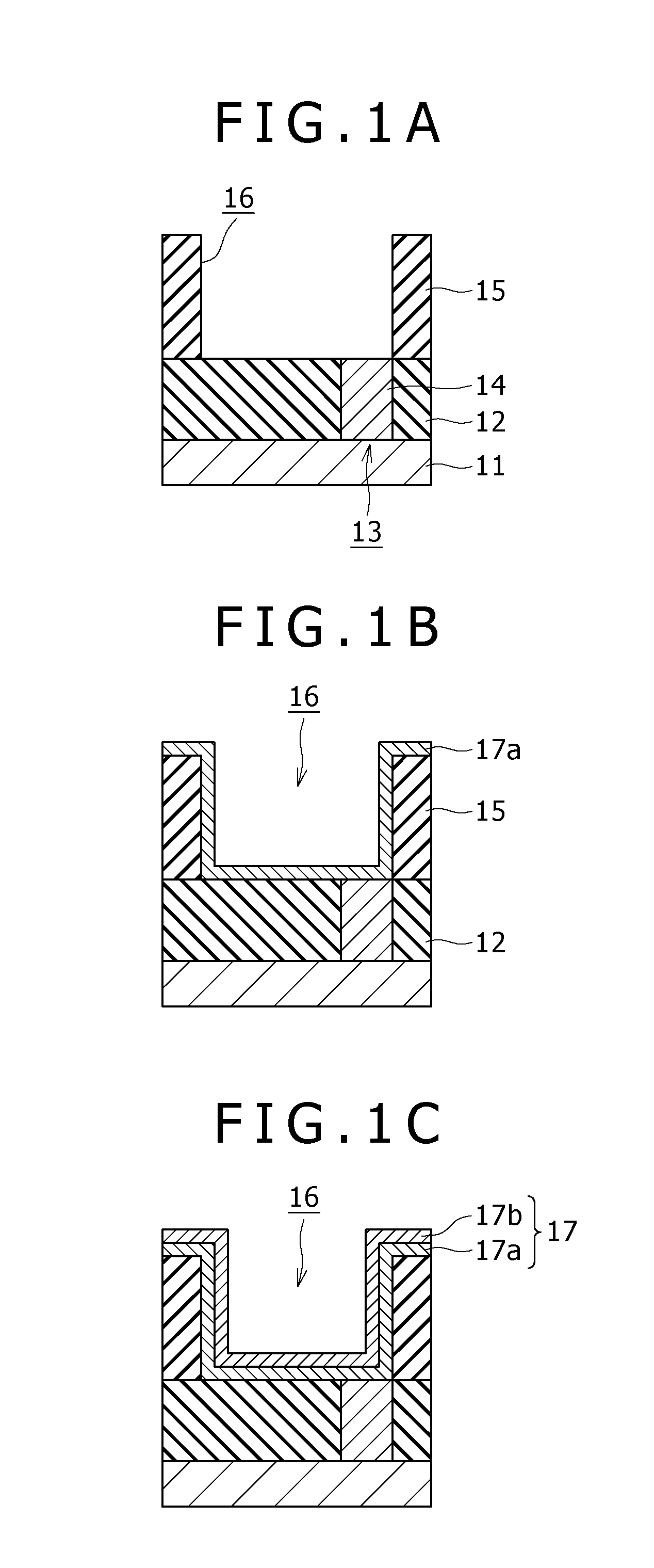

[0023]A method for manufacturing a semiconductor device according to a first embodiment of the present invention relates to formation of a single damascene interconnect structure. The first embodiment will be described below with reference to FIGS. 1A to 1F as sectional views of manufacturing steps. In the following description, the same components as those in the related art are given the same numerals.

[0024]Referring initially to FIG. 1A, an interlayer insulating film 12 composed of e.g. SiO2 is formed on a substrate 11 formed of a silicon wafer on which elements such as transistors are formed. Thereafter, a via hole 13 reaching the substrate 11 is formed, and then a via 14 composed of e.g. W is buried in the via hole 13.

[0025]Subsequently, by e.g. plasma enhanced chemical vapor deposition (PECVD) with use of silane (SiH4) as the deposition gas, an interlayer insulating film 15 composed of e.g. SiO2 is formed on the interlayer insulating film 12 and the via 14.

[0026]Subsequently, ...

second embodiment

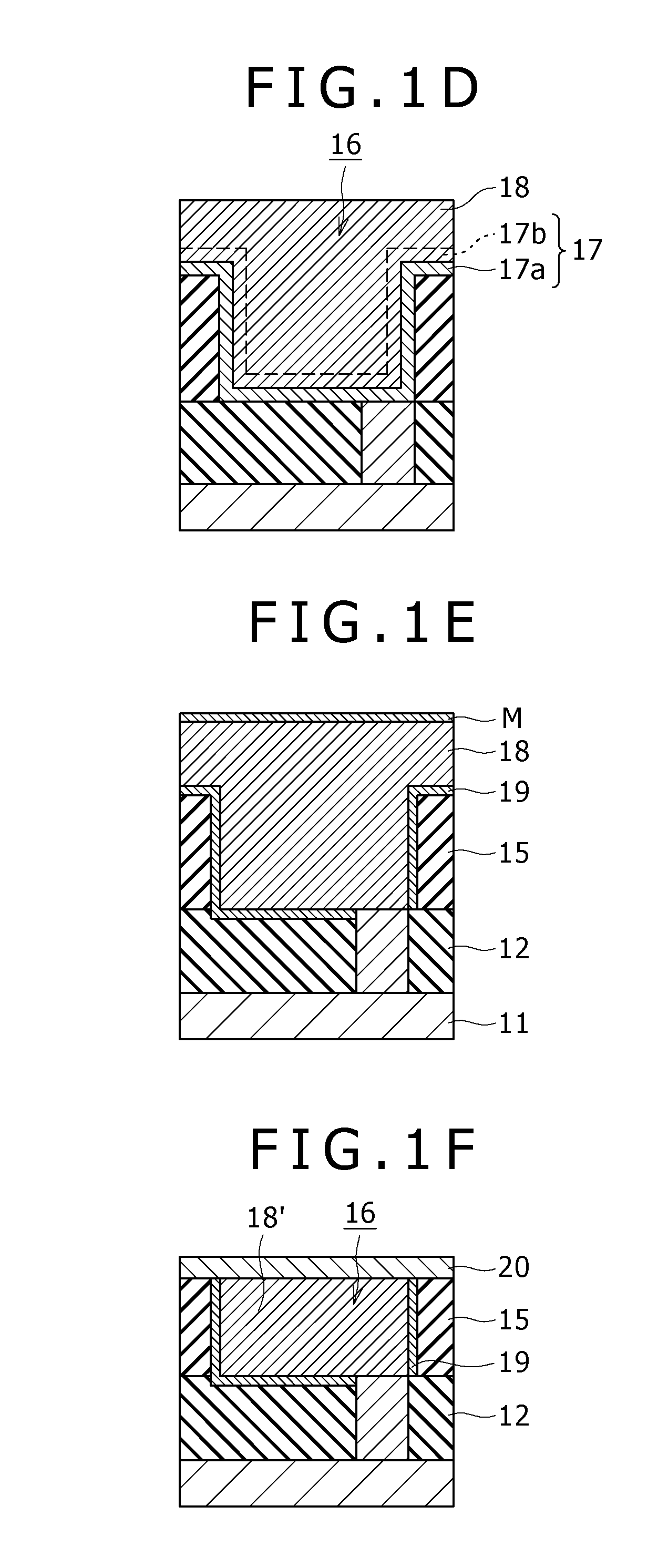

[0044]A method for manufacturing a semiconductor device according to a second embodiment of the present invention will be described below with reference to FIGS. 2A to 2K as sectional views of manufacturing steps. For the description of the method according to the second embodiment, an example in which a dual damascene interconnect structure is formed over the cap film described in the first embodiment will be described.

[0045]Referring initially to FIG. 2A, on the cap film 20, an interlayer insulating film 21 composed of e.g. SiO2 is deposited to a film thickness of 350 nm by e.g. PE-CVD. Subsequently, a resist pattern (not shown) having a via hole pattern is formed on the interlayer insulating film 21, and then a via hole 22a reaching the cap film 20 is formed by etching with use of this resist pattern as the mask.

[0046]Referring next to FIG. 2B, a resist R is applied on the interlayer insulating film 21 in such a manner as to fill the via hole 22a. Subsequently, a spin-on-glass (S...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com