Highly-scalable hardware-based traffic management within a network processor integrated circuit

a network processor and integrated circuit technology, applied in the field of hardware-based traffic management within the network processor integrated circuit (ic), can solve the problems of reducing the amount of space available on the ic for other circuitry, requiring a large ic footprint, etc., and achieves the effects of large ic footprint, large area, and high throughpu

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

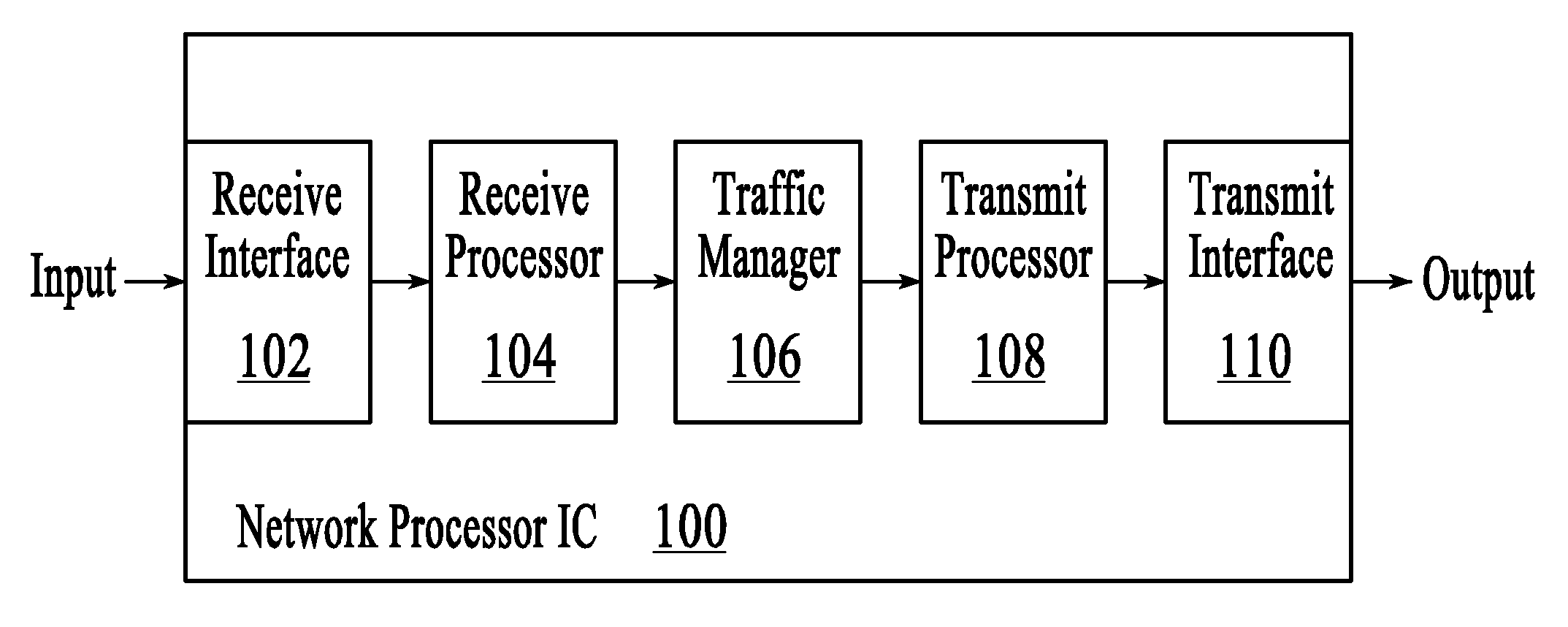

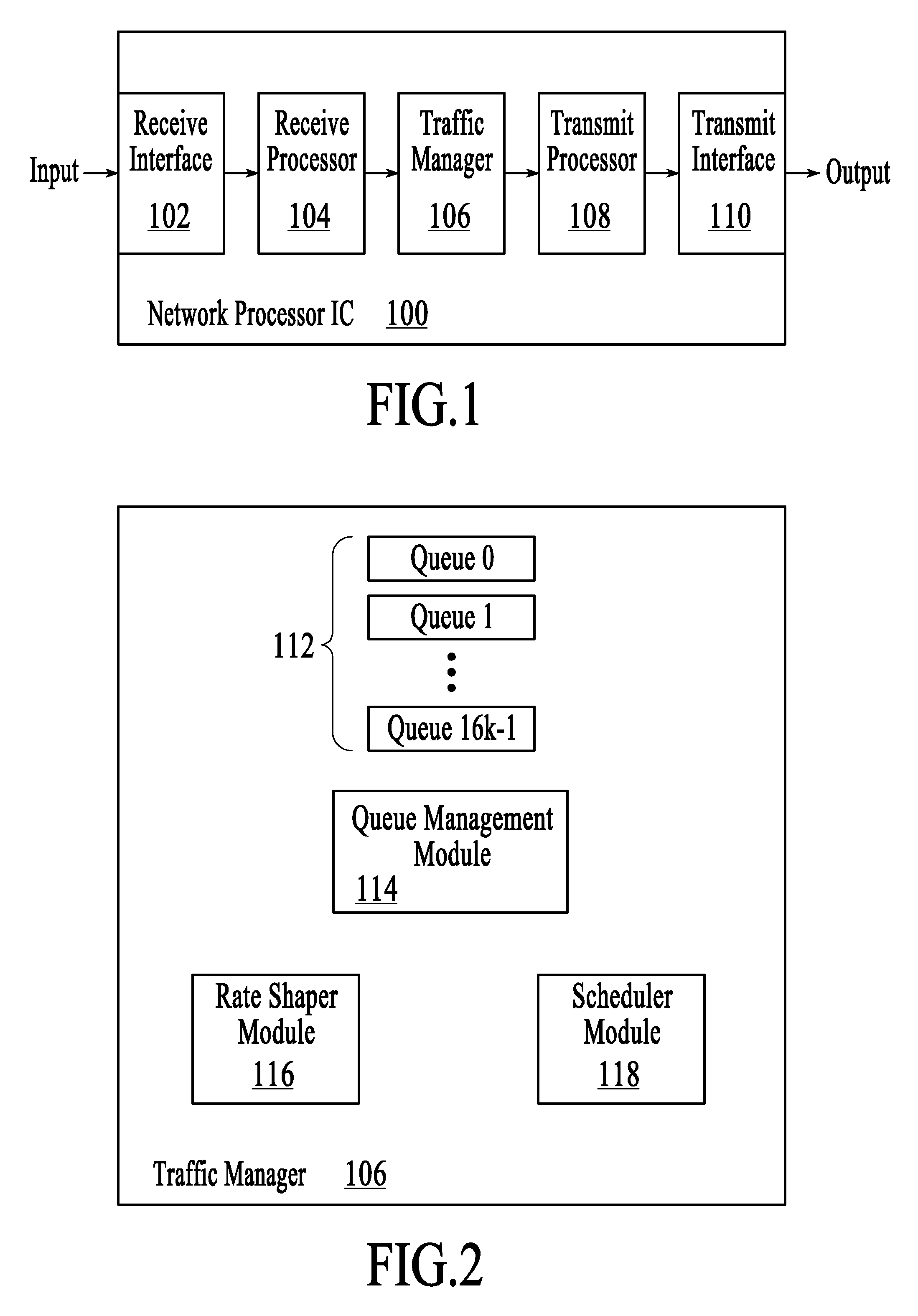

[0021]FIG. 1 depicts a functional block diagram of an embodiment of a network processor IC 100 that can be used in a network device such as a router and / or a switch to process various different types of network traffic (e.g., voice, video, and data). The network processor IC includes a receive interface 102, a receive processor 104, a traffic manager 106, a transmit processor 108, and a transmit interface 110. The receive interface performs, for example, physical layer conversion and deserializing operations. The receive processor supports, for example, traffic classification, traffic editing, and queuing operations. The traffic manager supports, for example, queue management, rate shaping, and scheduling operations. Operations of the traffic manger are the focus of the invention and are described in more detail below. The transmit processor supports, for example, traffic editing and dequeing operations and the transmit interface supports, for example, serializing and physical layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com