Methods for manufacturing silicon wafer and silicon epitaxial wafer, and silicon epitaxial wafer

a technology of epitaxial wafers and manufacturing methods, applied in semiconductor/solid-state device manufacturing, basic electric elements, electric devices, etc., can solve the problems of affecting the ig capability, so as to and improve the ig capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

examples

[0192] While description will be given of the present invention showing Experimental Examples below, the present invention is not limited to the Experimental Examples.

experimental examples 1 to 5

[0193] There were prepared boron-doped silicon wafers each having a diameter of 8 inches, a plane orientation of and resistivity of about 10 Ω·cm grown by means of a CZ method. Oxygen concentrations of the wafers were 16.0, 17.0, 18.5 and 19.5 ppma, respectively (JEIDA scale). The wafers were all subjected to heat treatment at 1050° C. for 1 hr. With the aid of the heat treatment, almost all oxygen precipitation nuclei formed in a crystal thermal history are annihilated. By this treatment, for example, there can be simulated states of an epi wafer containing almost no oxygen precipitation nuclei and a wafer heat-treated at a temperature of 1000° C. or higher in advance. Note that JEIDA is an abbreviation for Japan Electronic Industry Development Association (now renamed JEITA: Japan Electronics and Information Technology Industries Association).

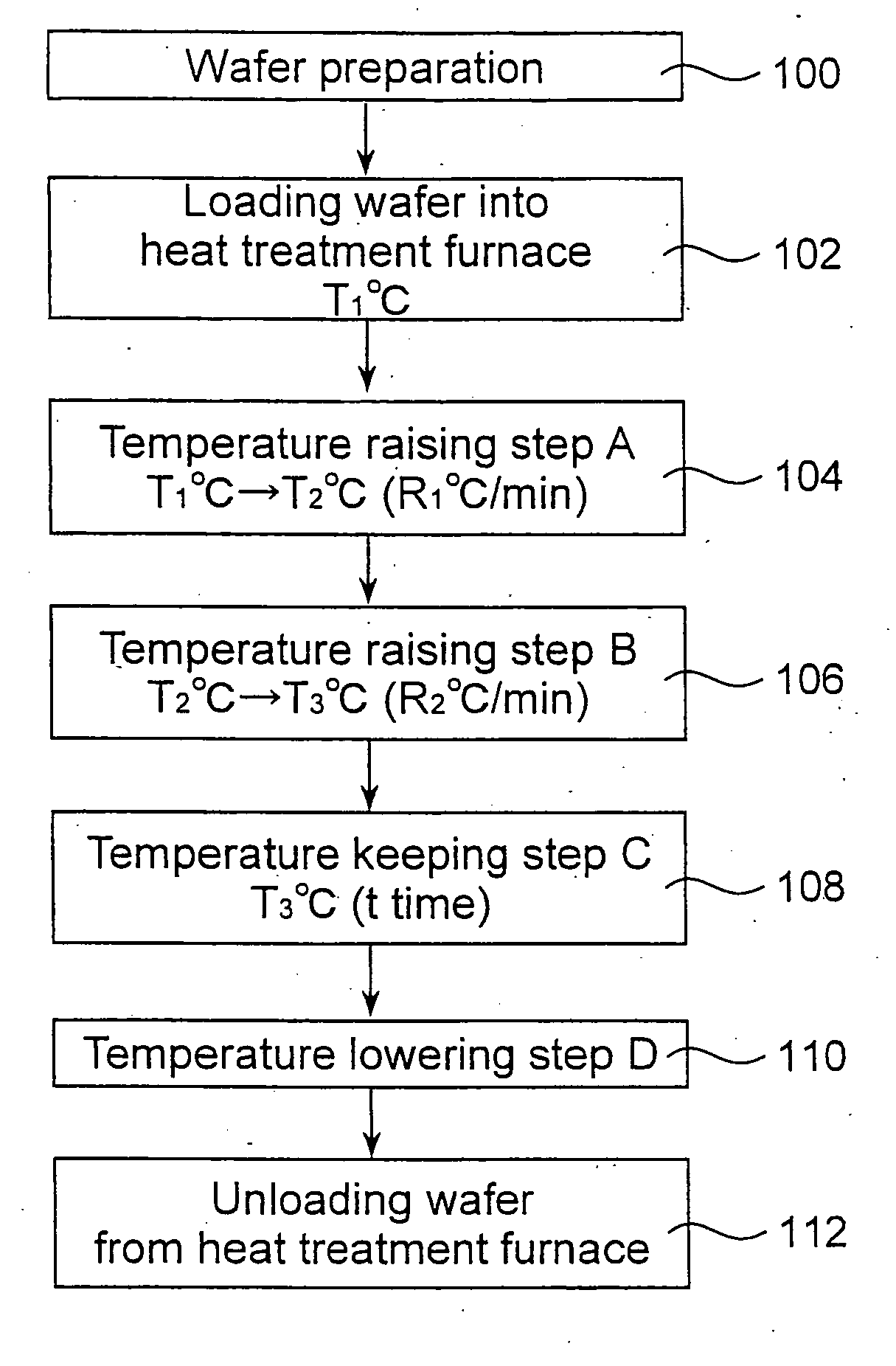

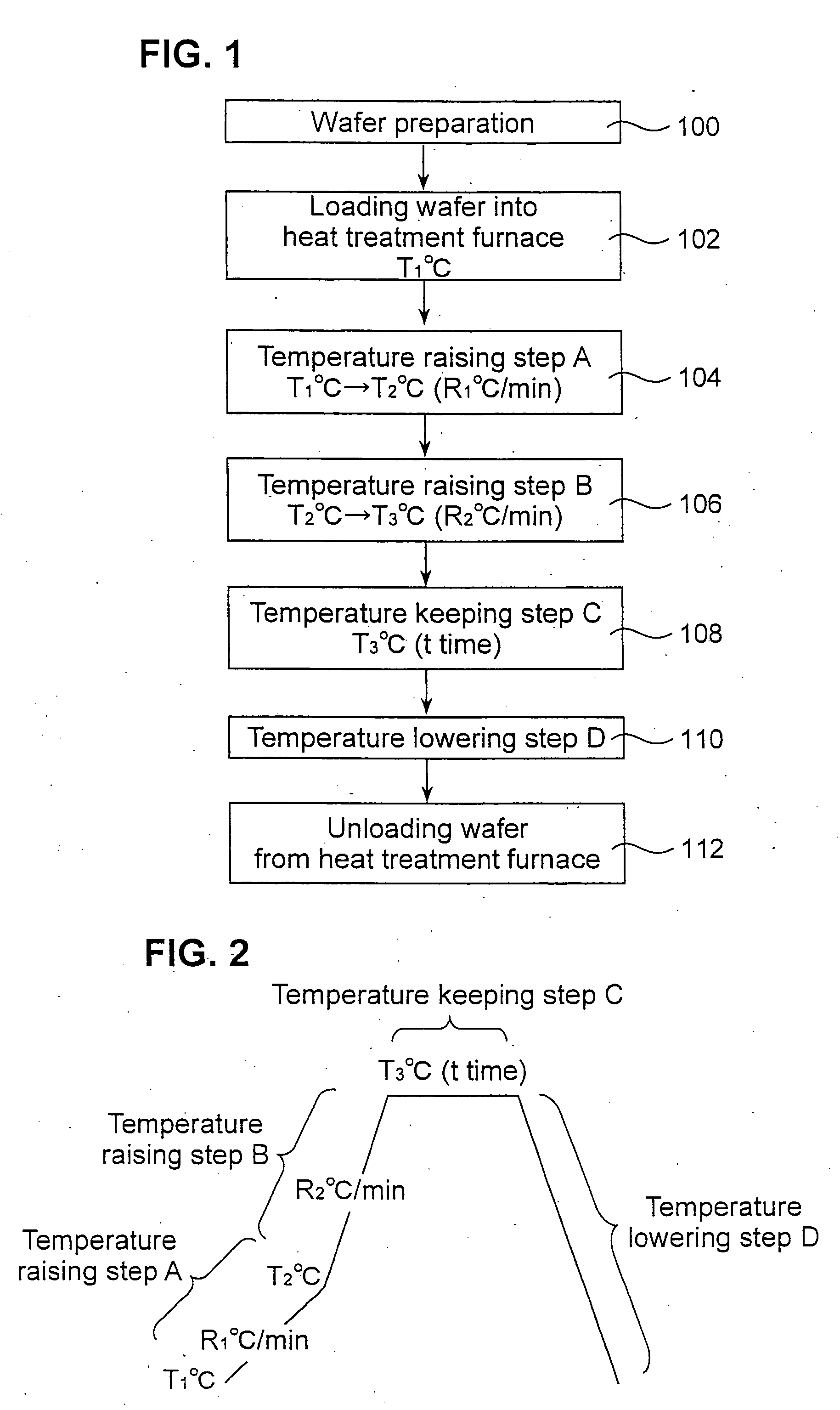

[0194] Next, heat treatment shown in FIGS. 1 and 2 was applied to the wafers. That is, a temperature was raised from T1° C. to T2° C. at a...

experimental examples 6 to 10

[0202] There were prepared mirror-polished silicon wafers each having a diameter of 8 inches, a plane orientation of and resistivity of about 10 Ω·cm, which were manufactured from different two portions (these portions belong to positions grown in the former half and the latter half of the crystal growth step and hereinafter may be referred to as a crystal position A and a crystal position B, respectively) of a boron-doped silicon single crystal grown by means of a CZ method. Oxygen concentrations of the wafers are 16 ppma to 20 ppma (JEIDA scale).

[0203] Next, the wafers were subjected to heat treatment in atmosphere of a mixture of oxygen and nitrogen according to a procedure shown in FIGS. 3 and 4. That is, the wafer was kept at T4° C. for t1 time, thereafter the temperature was raised from the T4° C. to T5° C. at a rate of R° C. / min and kept at the T5° C. for t2 time. After the keeping, the temperature in a heat treatment furnace was lowered to 700° C. at a rate of 2° C. / min an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com