Methods for preparing a bonding surface of a semiconductor wafer

a technology of semiconductor wafers and bonding surfaces, applied in semiconductor devices, solid-state devices, decorative arts, etc., can solve problems such as surface blisters, surface rough patches, and detrimental to good bonding, and achieve the effect of increasing bonding energy and increasing bonding energy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

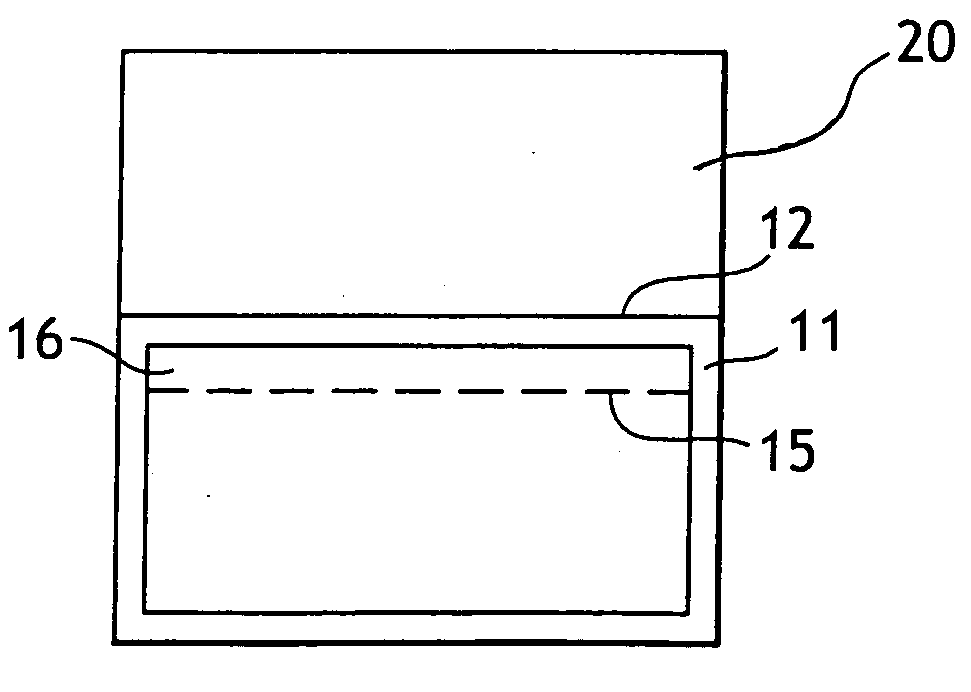

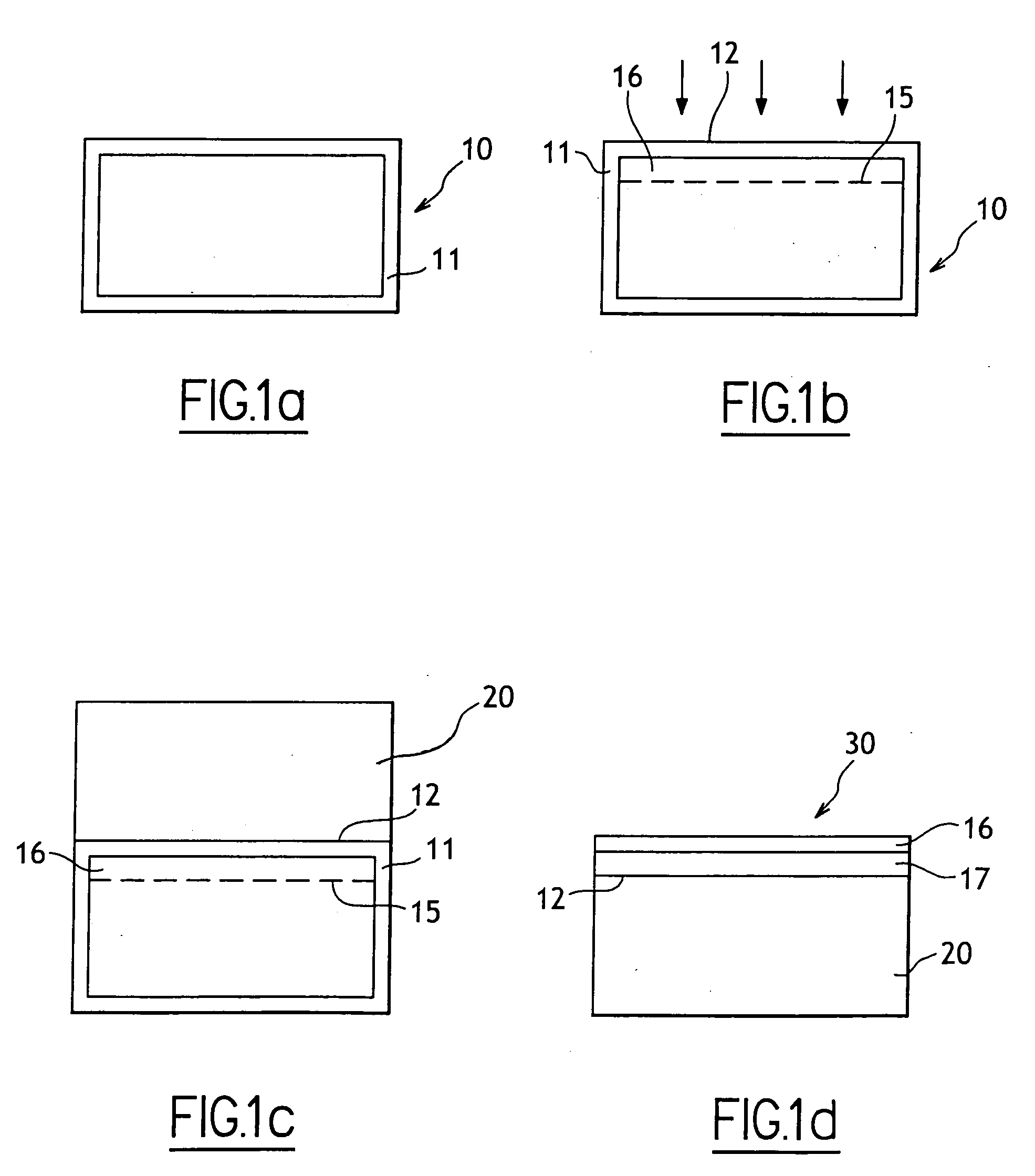

[0018] The wafer cleaning process according to the invention may be used with the thin layer removal method according to the SMART-CUT® process. Referring to FIG. 1a, a first stage includes oxidizing a semi-conductor wafer to create a donor wafer 10 having an oxide layer 11 on its surface. This oxidation process may be native, or may be conducted under a heat treatment (i.e. thermal oxidation), or by deposit of aggregates of SiO2.

[0019] With reference to FIG. 1b, the oxidized donor wafer 10 is subjected to an implantation of atomic species through one of the oxidized surfaces. The atomic species may be hydrogen and / or helium ions. The atomic species used during implantation are dosed and are implanted with a predetermined energy to form a weakened zone 15 at a pre-set depth under the surface of the donor wafer 10. The weakened zone 15 has a particular weakness relative to the rest of the donor wafer 10. A film 16 is thus formed that is delimited by the weakened zone 15 and the oxid...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Temperature | aaaaa | aaaaa |

| Temperature | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com