Low-stress packaging method of MEMS chip

A packaging method and low-stress technology, which can be used in measurement devices, decorative art, microstructure devices, etc., can solve the problems of low-temperature packaging technology, such as low bonding temperature, low bonding rate, and many holes in the bonding interface, and achieve improved chemical performance. Effects of reactivity, enhanced bonding strength, and increased atomic-scale contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

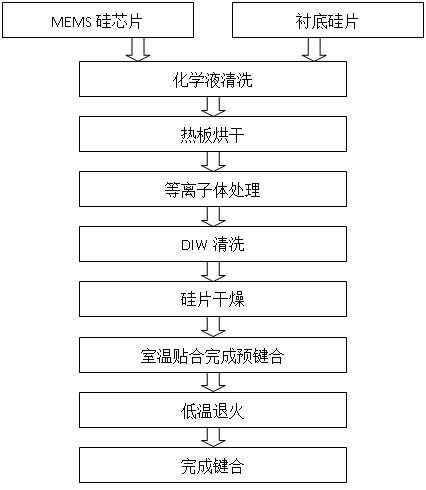

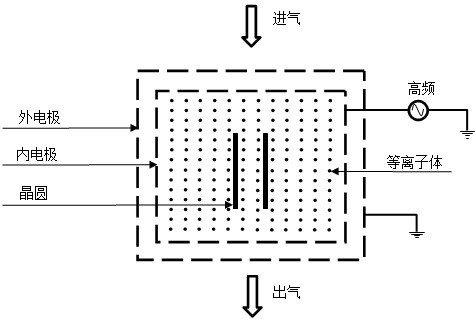

[0054] The invention is a MEMS chip low-stress packaging method, which uses the MEMS silicon chip and substrate silicon chip manufactured by all processes, and sequentially performs chemical liquid treatment, hot plate drying, plasma treatment, DIW (deionized water) cleaning, Silicon wafer drying, pre-bonding, low-temperature annealing and other processes are used to realize low-stress packaging of MEMS chips with homogeneous materials. process such as figure 1 As shown, the specific steps are as follows:

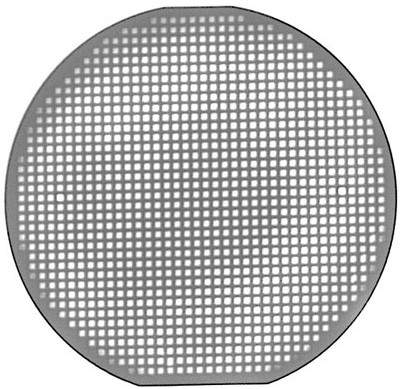

[0055] Step 1. Use double-sided polished silicon wafers, one is the completed MEMS silicon chip, and the other is the substrate silicon wafer, and the micromachining method is used to complete the array through-hole fabrication;

[0056] Step 2, use the SPM solution under the condition of 120°C, the volume ratio is H 2 SO 4 :H 2 o 2 = 5:1 (where H 2 SO 4 The concentration is 96.0±1.0%, H 2 o 2 The concentration is 31.0±1.0%), the surface treatment of the MEMS silicon...

Embodiment 2

[0065] In this embodiment, a double-sided polished silicon wafer is used, one of which is a finished MEMS silicon chip, and the substrate silicon wafer is mechanically drilled to complete the array through-hole fabrication. Except that the process parameters listed in the following steps change, all the other process steps and process parameters are completely consistent with embodiment 1.

[0066] In step 2, use the SPM solution under the condition of 100°C, and the volume ratio is H 2 SO 4 :H 2 o 2 = 10:1 (where H 2 SO 4 The concentration is 96.0±1.0%, H 2 o 2 The concentration is 31.0±1.0%), the MEMS silicon chip and the substrate silicon chip are surface treated, the treatment time is 30min, and the DIW cleaning is 30min;

[0067] In step 3, use the RCA1 solution at 50°C, and the volume ratio is NH 4 OH:H 2 o 2 :H 2 O= 1:1:10 (where NH 4 OH concentration is 28.0~30.0%, H 2 o 2 The concentration is 31.0±1.0%), the MEMS chip and the substrate silicon wafer are ...

Embodiment 3

[0073] In this embodiment, except that the process parameters listed in the following steps are changed, the remaining process steps and process parameters are completely consistent with those of Example 1.

[0074] In step 2, use the SPM solution under the condition of 110°C, and the volume ratio is H 2 SO 4 :H 2 o 2 = 7:1 (where H 2 SO 4 The concentration is 96.0±1.0%, H 2 o 2 Concentration is 31.0±1.0%), surface treatment of MEMS silicon chips and substrate silicon wafers;

[0075] In step 3, use the RCA1 solution at 60°C, and the volume ratio is NH 4 OH:H 2 o 2 :H 2 O= 1:1:7 (where NH 4 OH concentration is 28.0~30.0%, H 2 o 2 The concentration is 31.0±1.0%), the surface treatment of the MEMS silicon chip and the substrate silicon chip is carried out, the treatment time is 20min, and the DIW cleaning is 60min;

[0076] In step 5, anode voltage 2000V, anode current 800mA, gate current 160mA, processing time 30sec, O 2 Flow 160l / hr, CF 4 Flow 160l / hr;

[0077...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com