Slew rate controlled output buffer

a buffer circuit and output buffer technology, applied in logic circuits, voltage/current interference elimination, reliability increasing modifications, etc., can solve the problems of affecting the output of other signals on a given ic chip or on an application circuit board/card, and the components of the given ic chip interfere with other signals, etc., to achieve tight control of output impedance, tight control of output slew rate, and reduce propagation delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Glossary

[0017] CMOS—Complementary Metal Oxide Semiconductor.

[0018] FET—Field Effect Transistor. The gate terminal, source terminal and drain terminal of a FET are referred to herein as the gate, source and drain of the FET, respectively.

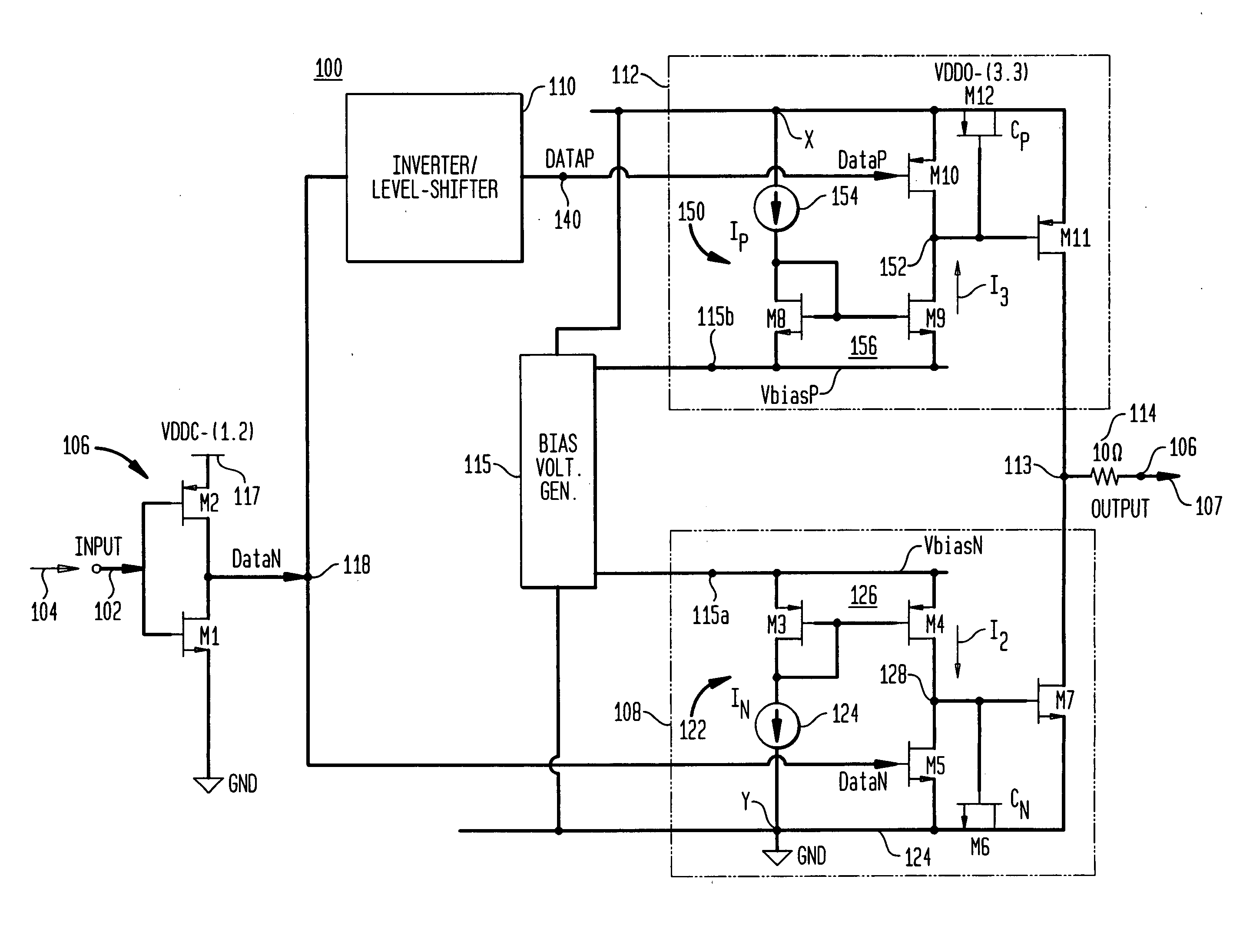

[0019] NMOS—n-type MOS. In FIG. 1, an arrow pointing from the gate to the source of a FET indicates an NMOS FET, while an arrow pointing in the opposite direction indicates a PMOS FET, as is understood in the art.

[0020] PMOS—p-type MOS, which is complementary to NMOS.

Overview

[0021]FIG. 1 is a circuit and block diagram of an example output buffer 100 constructed and operated in accordance with the present invention. Buffer 100 may be constructed on a single IC. In an embodiment, output buffer 100 is a PCI-X Input / Output (I / O) output buffer. Buffer 100 includes an input terminal 102 for receiving an input logic signal or voltage 104, an output terminal 106, and circuitry, coupled between the input and output terminals, for producing an output l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com