High-capacity cache memory

A high-speed buffer storage and high-speed buffering technology, applied in static memory, digital memory information, information storage and other directions, can solve the problems of low read and write data rate of hard disk ports, affecting high-speed interface bandwidth, long time interval of hard disk ports, etc. The effect of buffer memory capacity, small read and write access latency, and large access bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described below in conjunction with the accompanying drawings.

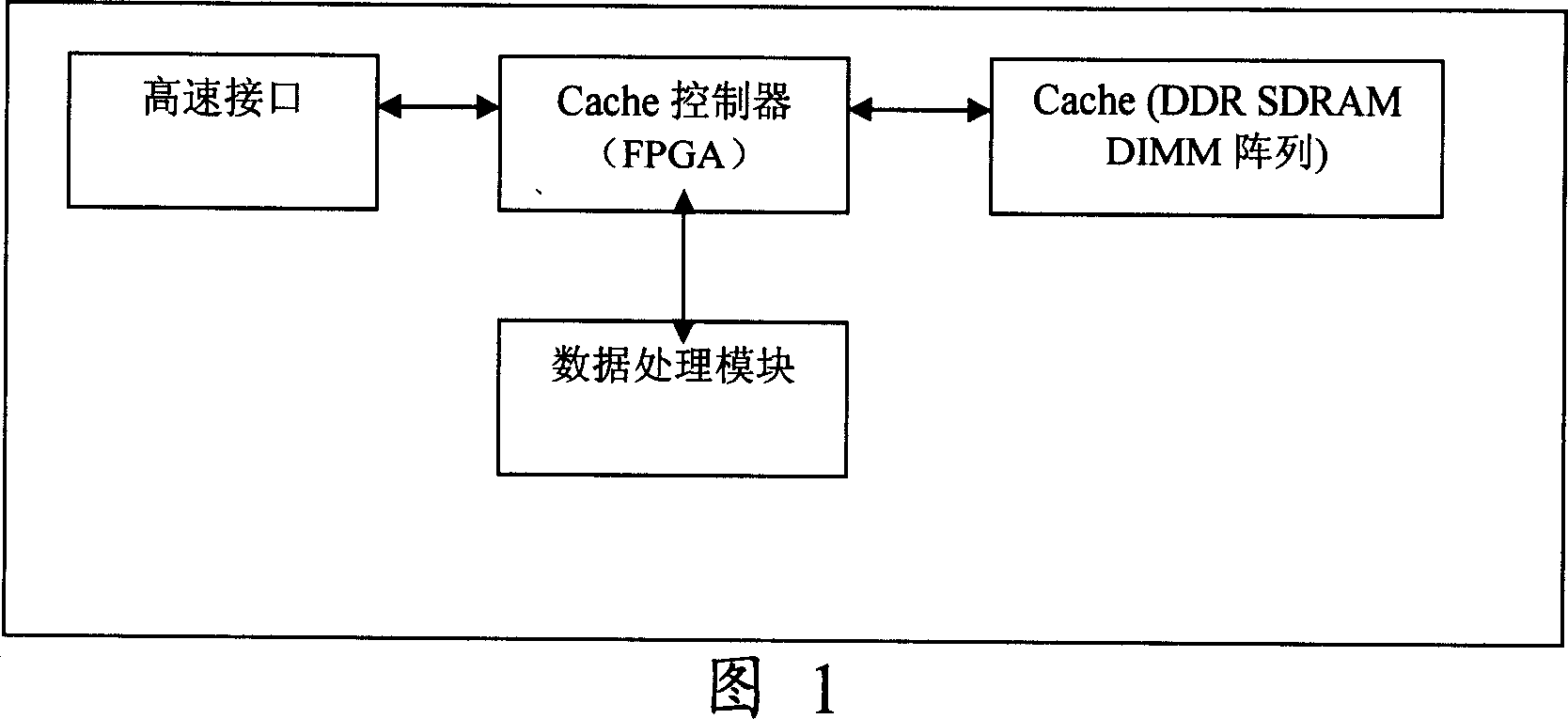

[0021] Please refer to shown in Fig. 1, the high-capacity high-speed storage buffer of the present invention adds the Cache that is made up of double data rate synchronous dynamic random access memory stick array (DDRSDRAM DIMM Array, hereinafter referred to as DDR Array) between the high-speed interface chip and the data processing module A unit and a Cache controller unit implemented with a Field Programmable Gate Array (Field Programmable Gate Array, hereinafter referred to as FPGA). The data processing module can store data in the Cache unit composed of DDR Array, or read data from the Cache unit as needed, and the high-speed interface unit exchanges data with the Cache unit through the Cache controller.

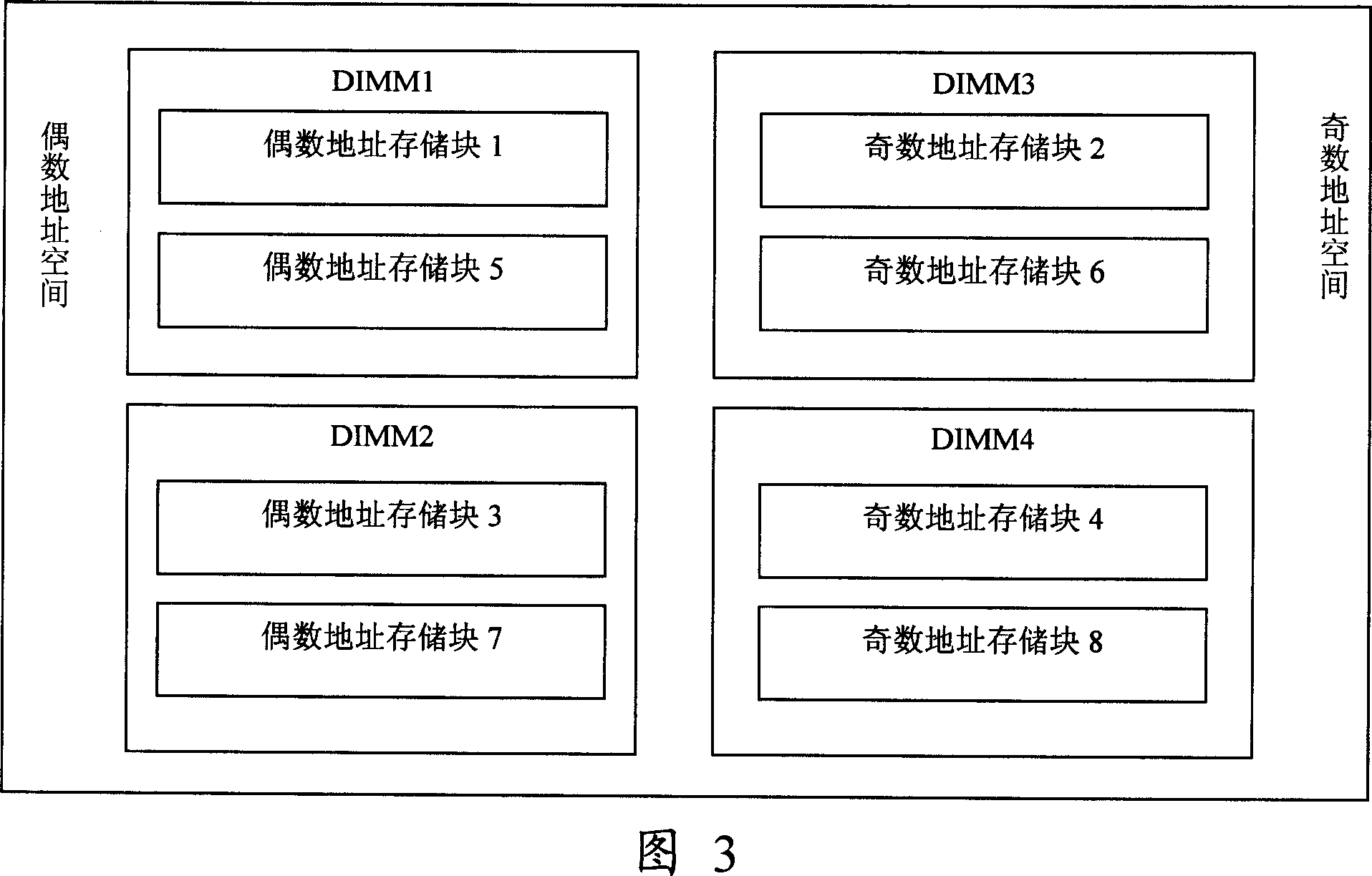

[0022] DDR Array is symmetrically divided into 2 or 2 according ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com