Method of design of control circuit in static storage in LCD drive chipset

A technology for static memory and driving chips, applied in static indicators, cathode ray tube indicators, instruments, etc., can solve the problems of complex circuit structure and high chip power consumption, reduce chip power consumption, reduce processing time, and reduce line consumption. The effect of the number of scan operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

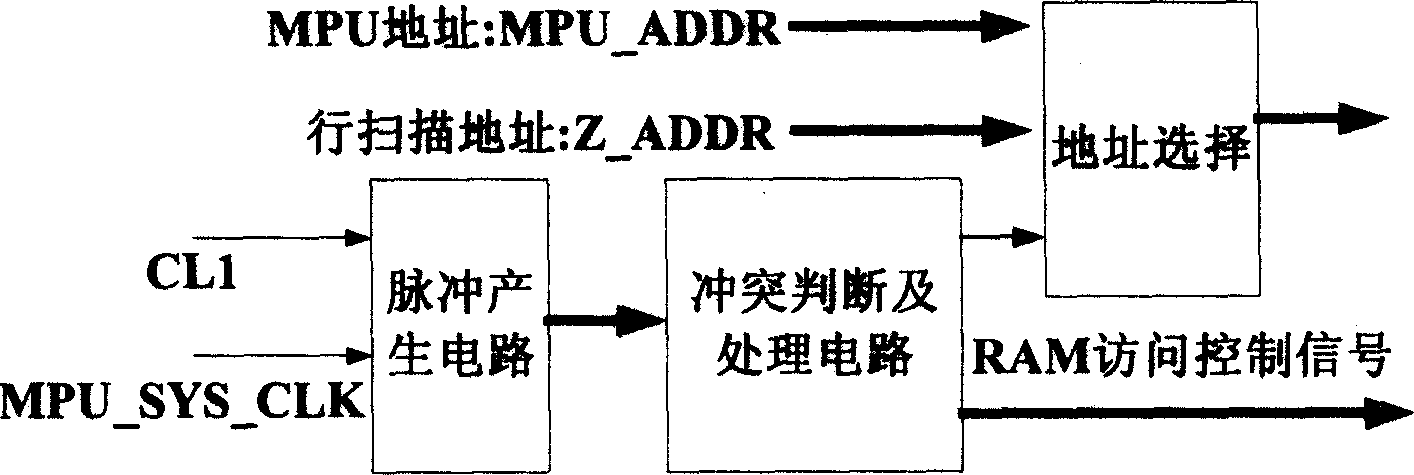

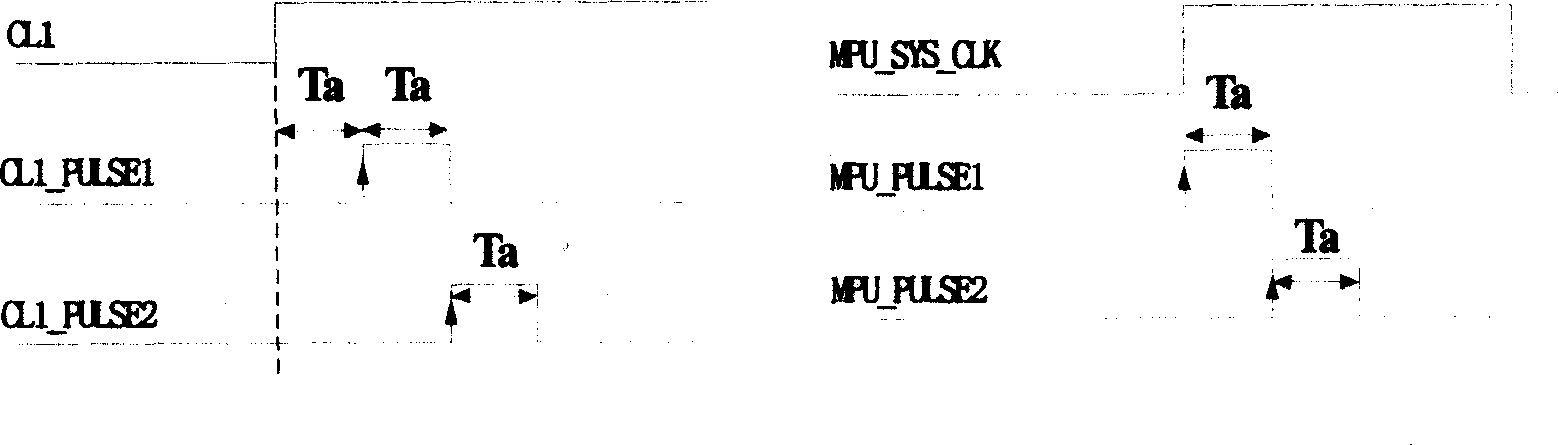

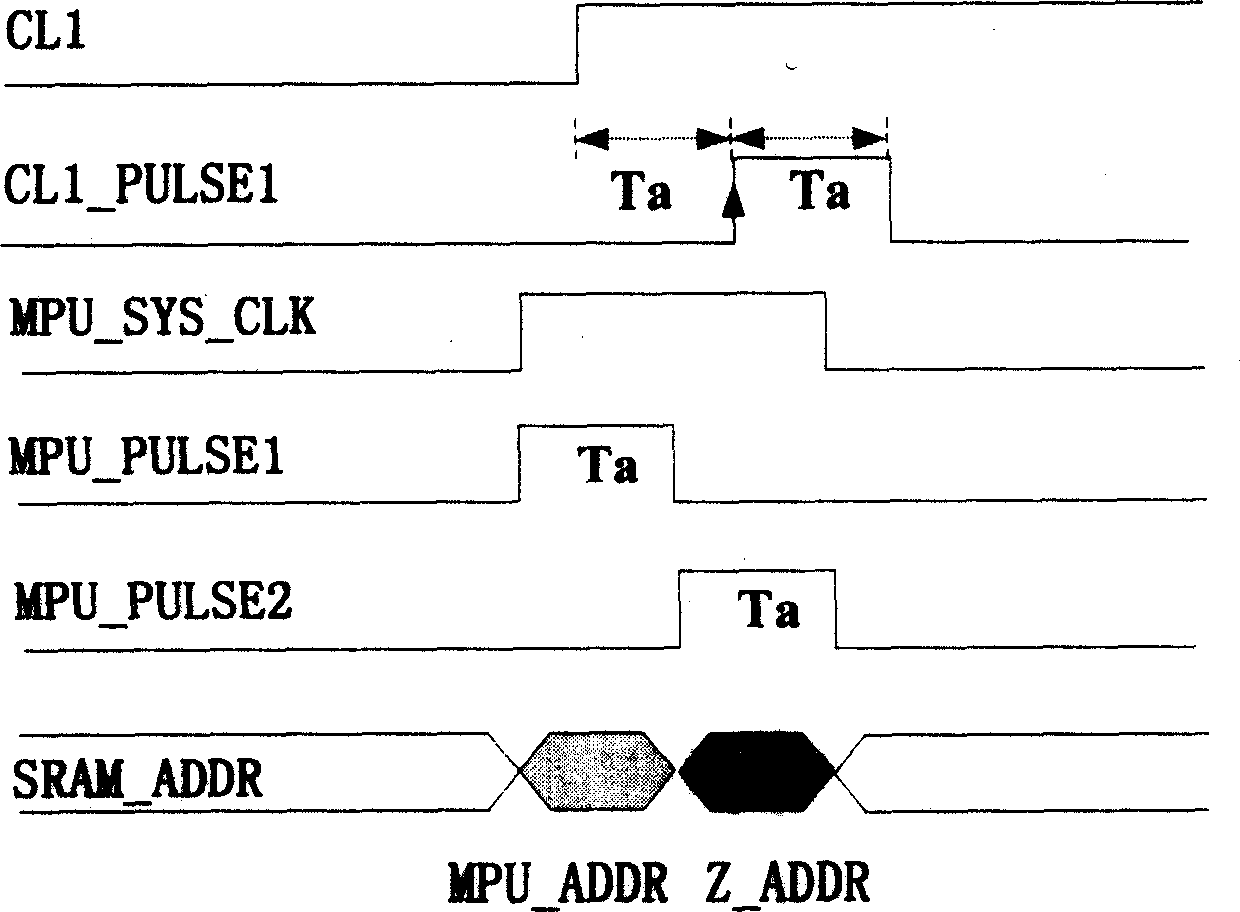

[0024] refer to Figure 1~2 In the present invention, the row scan clock CL1 and the MPU system clock MPU_SYS_CLK are used as the basic operation clocks, and each basic operation clock generates two sub-control signals with a pulse width of Ta when its rising edge arrives.

[0025] In order to ensure that the read and write operation of the MPU takes precedence over the row scan operation, the sub-control signal generated by CL1 is output after a delay of Ta. These two sub-control signals represent two time operation areas respectively. When the MPU_PULSE1 signal does not fall between the rising edge of CL1 and the falling edge of CL1_PULSE1, no timing conflict occurs; otherwise, it is determined that a timing conflict occurs. The first sub-control signal CL1_PULSE1 generated by the rising edge of the line scan signal CL1 is used as the operation area of the line scan, and all the control signals required for the line scan are generated in this operation area, and the line ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com