Semiconductor memory

一种存储器、半导体的技术,应用在静态存储器、数字存储器信息、信息存储等方向,能够解决器件面积增大等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] Embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

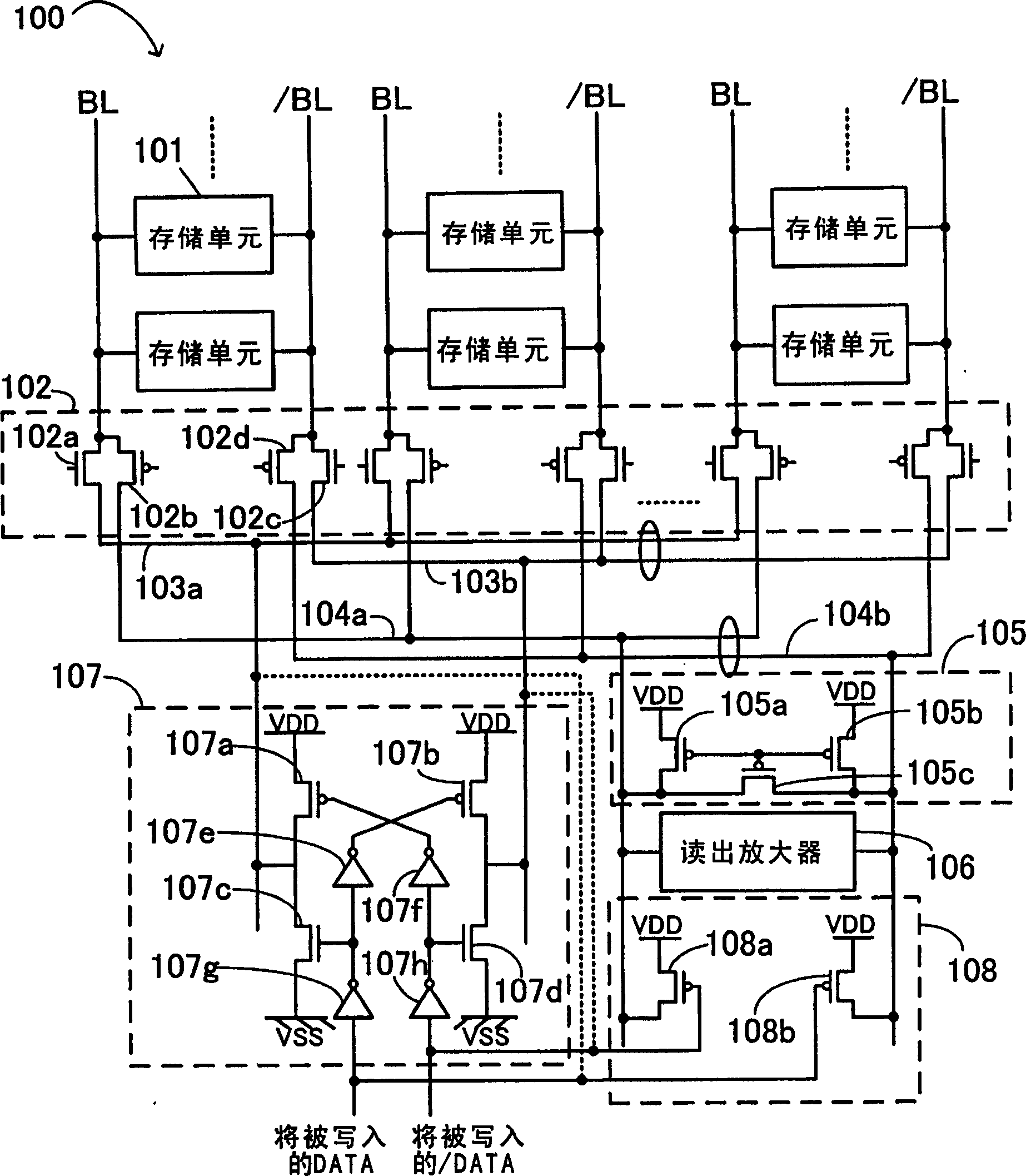

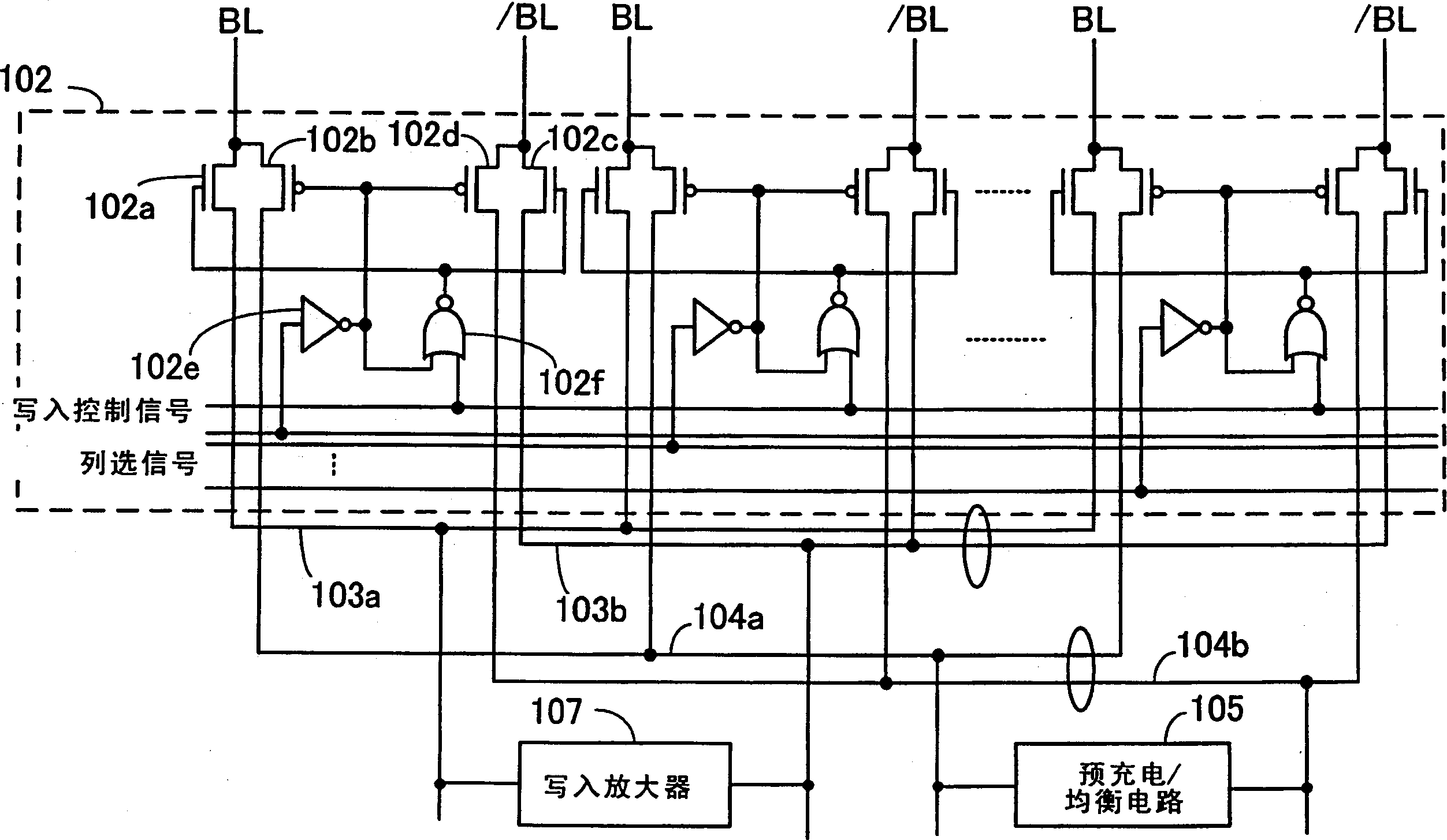

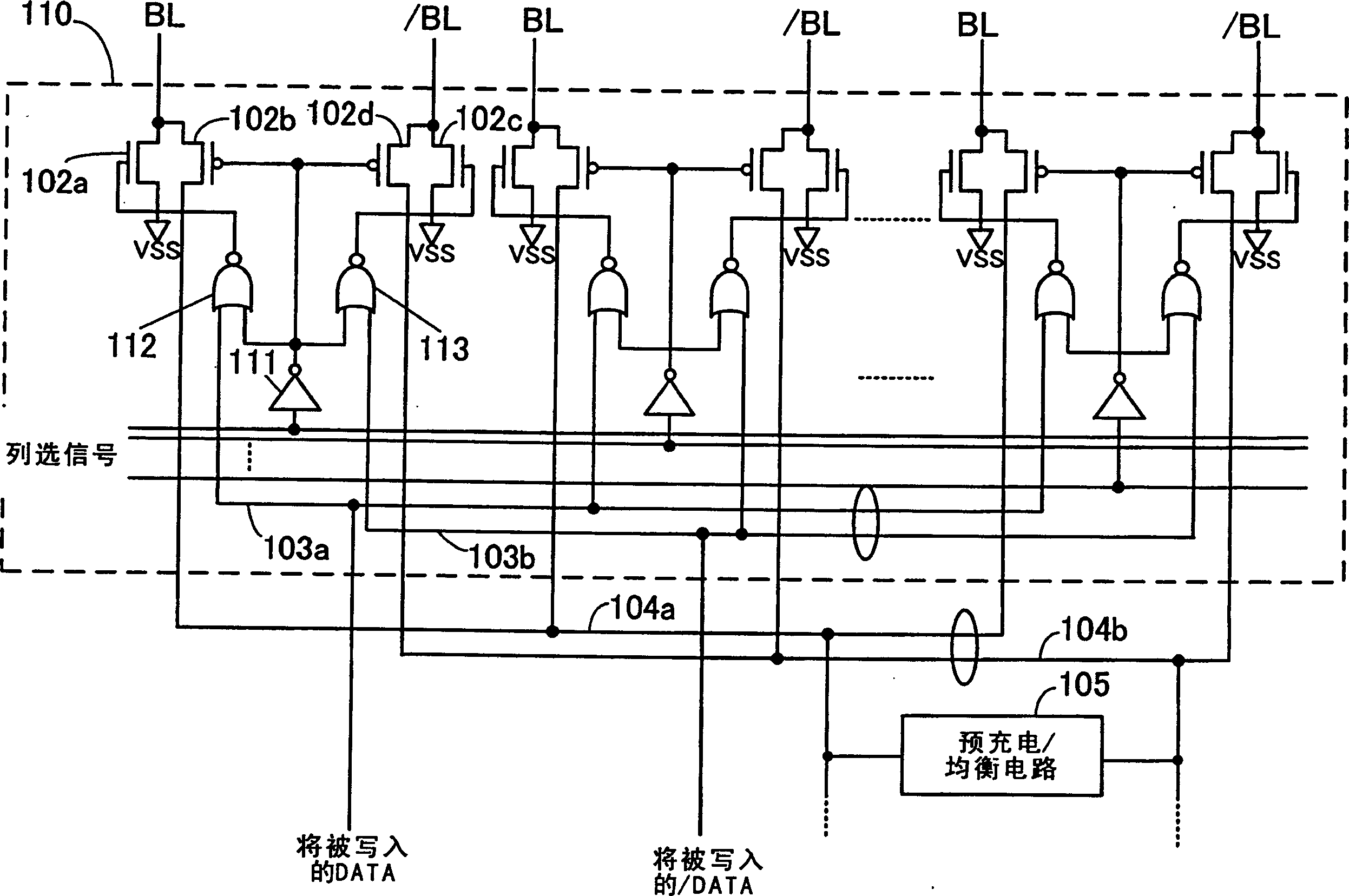

[0040] figure 1 is a circuit diagram of the semiconductor memory according to the first embodiment of the present invention.

[0041] The semiconductor memory 100 according to the first embodiment of the present invention includes a plurality of memory cells 101, a column selection circuit 102, write data buses 103a and 103b, read data buses 104a and 104b, a precharge circuit 105, a sense amplifier 106, a write An input amplifier 107 and a voltage boosting circuit section 108, wherein the plurality of memory cells 101 are arranged in the direction of rows and columns like a matrix, and are connected between complementary bit lines BL and / BL. exist figure 1 , the word lines WL connected to the plurality of memory cells 101 are not shown (see Figure 5 ).

[0042] The column selection circuit 102 selects the bit lines BL and / BL in response to the co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com